编写Verilog代码:

输入in,输出为out,对输入in维持的周期进行计数计数周期为N,如果N<4输出out为0;如果N>4,则拉高out并保持N/4个周期数,限定out的输出高电平数不大于6.

此题可以由状态加上两个计数器组成,状态机有4个状态分别为:

S_IDLE:初始状态,

S_CNT:输入信号高电平持续周期计数;

S_DE:判断输出高电平持续的周期数;

S_OUT:输出out。

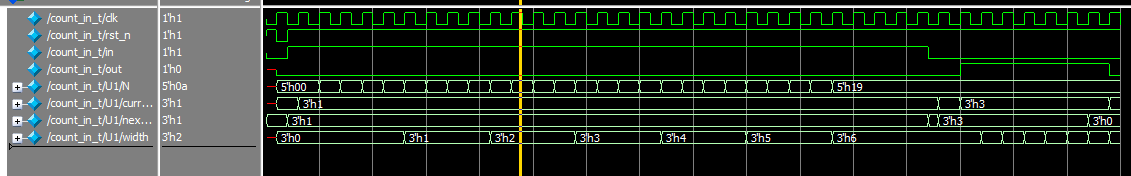

代码,testbench以及仿真结果如下:

module count_in( out,in,clk,rst_n);

parameter S0=2'b00,

S1=2'b01,

S2=2'b10,

S3=2'b11;

input in,clk,rst_n;

output out;

reg out;

reg [2:0] current_state,next_state;

reg [4:0] N;

reg [2:0] width;

always@(posedge clk or negedge rst_n)

begin

if (!rst_n)

current_state<=S0;

else

current_state<=next_state;

end

always@(*)

begin

next_state=2'bxx;

case(current_state)

S0:begin

if (in==1'b1)

next_state=S1;

else

next_state=S0;

end

S1:begin

if (in==1'b1)

next_state=S1;

else

next_state=S2;

end

S2:begin

if (width==0)

next_state=S0;

else

next_state=S3;

end

S3:begin

if (width==0)

next_state=S0;

else

next_state=S3;

end

default:next_state=S0;

endcase

end

always @ (*)

begin

if (current_state==S3)

out=1'b1;

else

out=1'b0;

end

always @ (posedge clk or negedge rst_n)

begin

if (!rst_n)

N<=0;

else if (current_state==S1)

begin

if (N<=5'd24)

N<=N+1'b1;

else

N<=N;

end

else if (current_state==S0)

N<=0;

end

always @ (posedge clk or negedge rst_n)

begin

if (!rst_n)

width<=0;

else if (current_state==S1)

begin

if (N<4)

width<=0;

else if (N<8)

width<=3'b001;

else if (N<12)

width<=3'b010;

else if (N<16)

width<=3'b011;

else if (N<20)

width<=3'b100;

else if (N<24)

width<=3'b101;

else

width<=3'b110;

end

else if (current_state==S3)

width<=width-1'b1;

end

endmodule

module count_in_t;

reg clk,rst_n;

reg in;

wire out;

count_in U1(.clk(clk),.rst_n(rst_n),.in(in),.out(out));

initial

begin

clk=1'b0;

forever #10 clk=~clk;

end

initial

begin

rst_n=1'b1;

in=1'b0;

#10 rst_n=1'b0;

#10 rst_n=1'b1; in=1'b1;

#600 in=1'b0;

end

endmodule

最后

以上就是正直铅笔最近收集整理的关于一天一道Verilog编程题(-)的全部内容,更多相关一天一道Verilog编程题(-)内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复