一、设计要求

1、设计一个能显示日期、小时、分钟、秒的数字电子钟,并具有整点报时的功能。

2、可手动校正时、分时间和日期值,时间以24小时为一个周期,有校时功能,可以分别对时及分进行单独校时,使其校正到标准时间;

3、计时过程具有报时功能,当时间到达整点前10秒进行蜂鸣报时; 为了保证计时的稳定及准确须由晶体振荡器提供表针时间基准信号由晶振电路产生1HZ标准的信号,分、秒为六十进制计数器,时为二十四进制计数器。

二、 实验设计和分析

2.1 工作原理

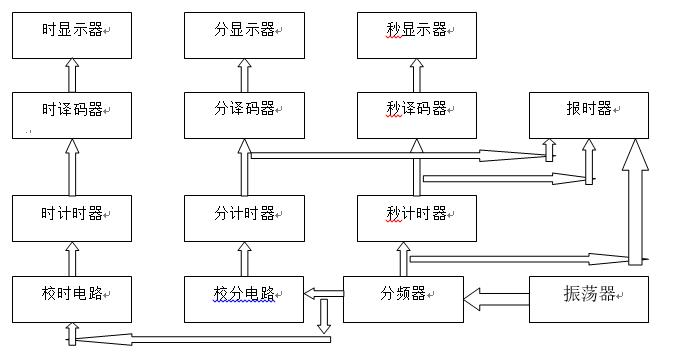

数字钟是一个将“ 时”,“分”,“秒”显示于人的视觉器官的计时装置。它的计时周期为24小时,显示满刻度为23时59分59秒,另外应有校时功能和报时功能。因此,一个基本的数字钟电路主要由译码显示器、“时”,“分”,“秒”计数器、校时电路、报时电路和振荡器组成。干电路系统由秒信号发生器、“时、分、秒”计数器、译码器及显示器、校时电路、整点报时电路组成。秒信号产生器是整个系统的时基信号,它直接决定计时系统的精度,一般用石英晶体振荡器加分频器来实现。将标准秒信号送入“秒计数器”,“秒计数器”采用60进制计数器,每累计60秒发送一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。“分计数器”也采用60进制计数器,每累计60分钟,发出一个“时脉冲”信号,该信号将被送到“时计数器”。“时计数器”采用24进制计时器,可实现对一天24小时的累计。译码显示电路将“时”、“分”、“秒”计数器的输出状态由七段显示译码器译码,通过六位LED七段显示器显示出来。整点报时电路时根据计时系统的输出状态产生一个脉冲信号,然后触发音频发生器实现报时。校时电路时用来对“时”、“分”显示数字进行校对调整的。

数字电子钟由振荡器、分频器 计数器、译码显示、报时等电路组成。其中振荡器和分频器组成标准秒信号发生器,由不同进制的计数器、译码器和显示器组 成计时系统。秒信号送入计数器进行计数,把累加的结果 以‘时,、‘分,、‘秒’的数字显示出来。‘时’显示由24进制 计数器、译码器、显示器构成,‘分’、‘秒’显示分别由60进 制计数器、译码器、显示器构成。可进行整点报时,计时出 现误差时,可以用校时电路校时、校分。

2.2系统总体框架图

2.3振荡器

振荡器产生的时基信号通常频率都很高,要使它成为能用过来计时的“秒”信号,需由分频器来完成。分频器的级数和每级的分频次数要根据时基频率来决定。例如,目前石英电子钟多采用32768HZ的时标信号,将此信号经过15级即可得到周期为1S的“秒”信号。也可选用其他频率的时基信号,确定好分频次数后再选选择合适的集成电路。

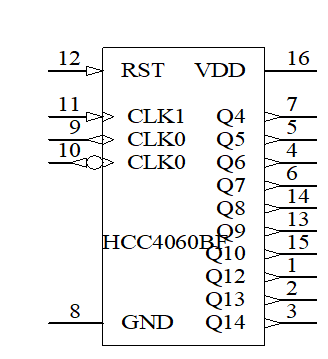

2.3.1由石英晶体振荡器构成的1HZ秒脉冲信号

石英晶体振荡器产生的32768Hz时标信号进行15分频。选用14为二进制计数器分频器CMOS集成电路cc4060,由它可以得到14分频的信号。再将TTL集成电路74LS74双D触发器钟的一个触发器结成计数器型,完成第15级分频,即可得到周期为1s的冲信号。

振荡器与分频器连接电路和cc4060引脚排列下图:

三、功能设计实现

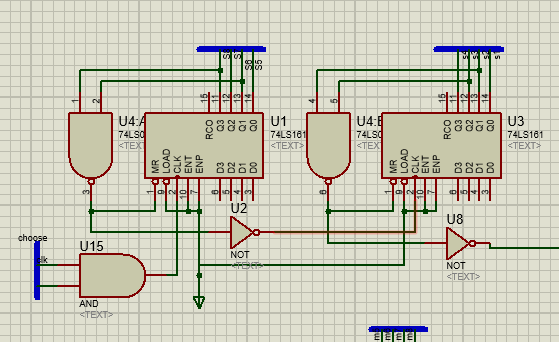

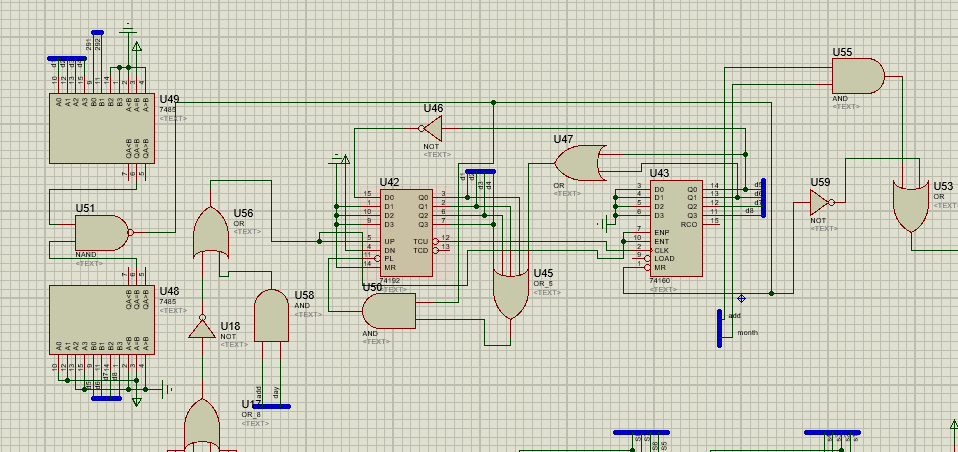

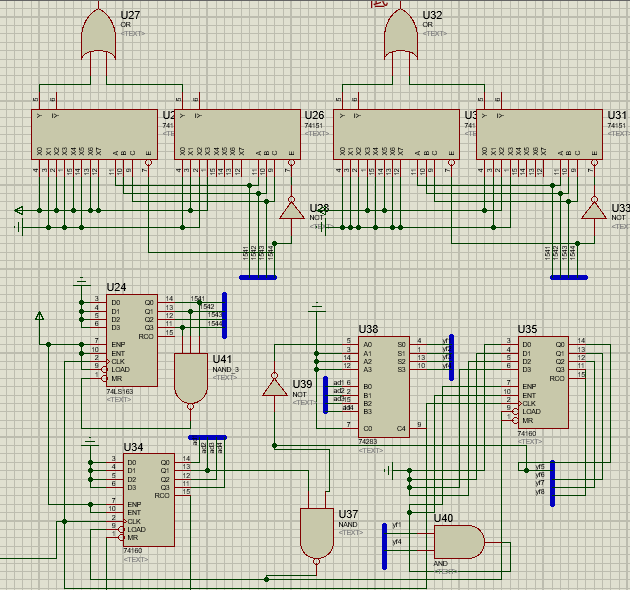

1、数字时钟的分、秒计数器都是采用两个74LS161完成60进制的计数。 秒信号发生器是数字电子钟的核心部分,它的精度和稳定度决定了时信号发生器和分信号发生器的精度。“秒”计数器为60进制计数器。实现此100模数的计数器是由两片中规模集成计数器74LS161构成的。分”计数器也是60进制计数器。同“秒”计数器一样是由两片中规模集成计数器74LS161构成。将两片74LS161按同秒计数器的方法先接成10进制加法计数器,再按“秒”计数器电路的方法连接就可实现100进制的计数器。再用同“秒”计数器的方法实现60进制。具体实现如下图:

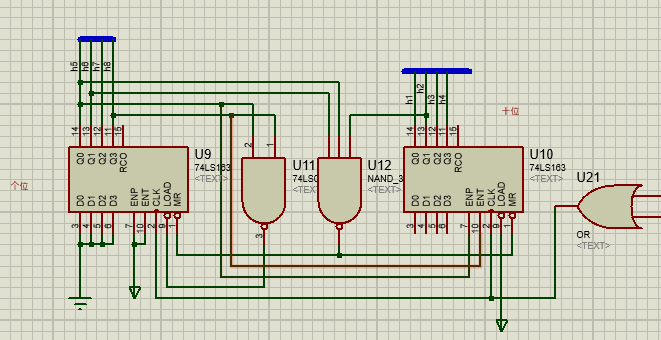

2、数字时钟的时计数器采用两个74LS163完成24进制。时计数器是24进制计数器。实现此模数的计数器也是由两片中规模集成计数器74LS90构成。同“分”、“秒”计数器一样,先将两片计数器74LS90连接成24进制的加法计数器,再把两片计数器74LS90用“秒”计数器的方法接成可实现100进制的计数器。当计数器状态为“2QD2QC2QB2QA、1QD1QC1QB1QA=0010、0100”时,要求计数器归零。通过2QB、1QC送出的置数脉冲使两片计数器74LS90同时清零,这样就构成了24进制计数器。具体实现如下图:

3、本次课程设计的重点是平年闰年对于大月,小月,二月(只算平年的29天)的天数的控制。所以天数在计数的时候需要根据月份的具体情况反馈回来一个三种情况,分别为二进制的00,01,10表示二月29天,小月30天,大月31天。由“天”图中的上面一部分根据返回的三种值进行天数的控制。分别在计数到30,31,32的时候清零,由于74LS192采用异步清零的方式,显示的最大值分别为29,30,31。然后清零重新计数。具体实现如下图:

4、数字时钟的月的计数部分分为计数部分和反馈部分。上面一部分采用两个8选一选择器组合成的16(>12个月)选一选择器(proteus中有16选一选择器,可以简化),反馈两位二进制需要两个16选一选择器。下面部分实际上是两个12进制计数器。一个用来显示,一个用来做反馈选择具体实现如下图:

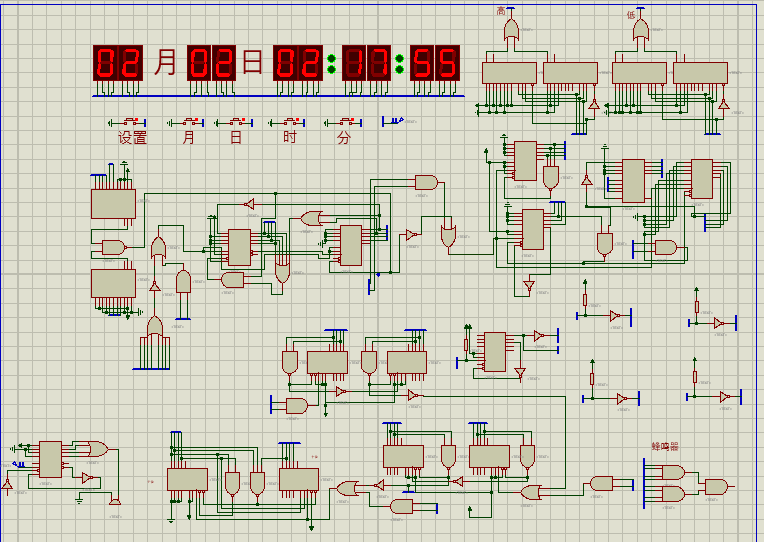

四 、程序仿真图

五、附录(源代码和虚拟仿真图下载)

由于篇幅有限相应的代码和仿真图已经上传(包括程序和课程设计报告),有需要的自取:

https://download.csdn.net/download/qq_44699923/12240923

另附一份数字时钟课程设计报告,有需要的自取:

https://download.csdn.net/download/qq_44699923/12240936

看到有人问就补充说明一下,之所以是.pdsprj文件,是因为我是新版proteus编辑的,如果想要.dsn文件只需要用proteus8.0编译一下重新保存就可以得到.dsn文件。

最后

以上就是如意面包最近收集整理的关于数字逻辑之数字时钟课程设计(含proteus仿真图及代码)的全部内容,更多相关数字逻辑之数字时钟课程设计(含proteus仿真图及代码)内容请搜索靠谱客的其他文章。

发表评论 取消回复