【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

很多人都以为写fpga,就是编写verilog,学习一门编程语言而已。这种观点,其实只对了一半。verilog作为一门语言,其本身是为了简化数字电路设计而存在的。但是,这种语言,和软件的编程语言不一样。这是因为,软件的编程语言是变成一条一条的汇编指令,最终这些汇编指令都是由cpu来执行完成的。数字电路则不同,verilog里面的语句是需要变成门电路、触发器、rom、ram、消耗fpga资源的。因此,在编写的时候需要格外慎重。

学过数字电路的同学,一般都会知道组合逻辑和时序逻辑。组合逻辑就是输出和输入是强相关的。只要输入发生变化,输出也会及时发生变化。时序逻辑则不同,它的输出只会发生在时钟上升沿或者下降沿的时候对输入进行响应。除此之外,时序逻辑还有记忆功能。这说明,输出结果除了和输入有关,还和历史状态有关,这本身就很有意义了。

所以,真正学好fpga,并不是说谁的verilog语法了解的多谁就学的好。关键是还在于理清组合逻辑和时序逻辑,设计好时序。在根据功能需求设计好时序图之后,就可以尝试一下设计状态机。有了上面两个部分的加持,就可以把时序图转化为verilog语句了。

有些同学说,为什么在fpga计算的过程中要拆分成组合逻辑和时序逻辑呢。这中间主要还是基于性能的考虑。假设时序逻辑之间的组合逻辑时间太长,这势必就会影响算法的运行频率。别人可以跑200M,你只能10M。如果把较长的运算过程拆分成若干个子状态,这样就可以实现流水线操作。数据a在做a状态运算时,数据b就可以做b状态运算。这样相比而言,运行效率就会比普通的组合逻辑高很多。

说到绘画时序图,现在有很多很好的工具,比如说wavedrom,就是很好的选择。首先尝试编写组合逻辑,比如在浏览器url输入https://wavedrom.com/editor.html,

对应的json文件是,

{ "signal" : [

{ "name": "input", "wave": "01..01." },

{ "name": "output", "wave": "01..01." }

]

}

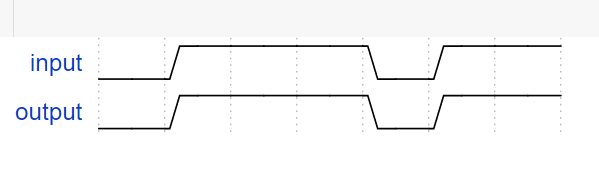

相关的效果图就是这样的,

换成verilog代码就是,

assgin b = a;如果是时序图,那么需要加上clk、rst、cnt,json文件修改如下

{ "signal" : [

{ "name": "clk", "wave": "p........." },

{ "name": "rst", "wave": "01.0.......",phase:0.5 },

{ "name": "cnt", "wave": "x223456789", data:["0","0","1","2","3","4","5","6","7"] }

]

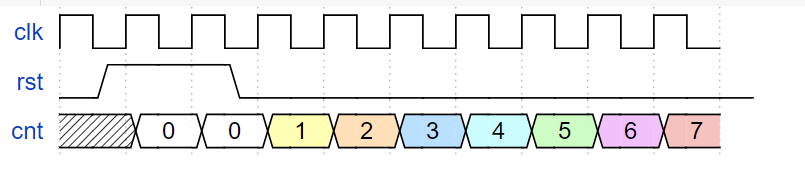

}相对应的图形也会不同的,

转换成verilog代码就是,

always@(posedge clk or posedge rst)

if(rst)

cnt <= 8'h0;

else

cnt <= cnt + 1;不管是什么样的需求或者是硬件协议标准,最终都是要转化成时序图、状态机的。所以开发过程中最好多画时序图,多画状态机。正向去开发软件,这样就会理解的更加深刻。虽然学习的过程中可能会慢一点。

最后

以上就是结实篮球最近收集整理的关于学fpga(组合逻辑和时序逻辑)的全部内容,更多相关学fpga(组合逻辑和时序逻辑)内容请搜索靠谱客的其他文章。

发表评论 取消回复