- 一 设计思路

- 二 verilog代码

- (一)程序代码变量说明

- (二)程序代码

- (三)时序模拟图

一 设计思路

- 采用组合逻辑电路,设计掩膜式只读存储器(Mask ROM)(在制造时写入内容,以后只能读,不能写入)。

- 3位地址线([2:0] addr):可以实现8个存储单元(字)的寻址,8个地址及其存储的8位数据的真值表如下(下表中各地址存储的数据D是地址addr的2倍):

| addr2 | addr1 | addr0 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 |

- 8位数据输出端([7:0] data_out)

- 读控制输入端R,低电平有效,R为1时输出为高阻态。

若读控制输入端(R)为低电平,则将3位地址线([2:0] addr)寻址到的ROM单元([7:0] rom[0:7])中的数据送到输出端([7:0] data_out),否则输出高阻态。

二 verilog代码

(一)程序代码变量说明

input R, // 读控制输入端,低电平有效

input [2:0] addr, // 3位地址线

output [7:0] data_out // 8位数据输出端

wire [7:0] rom[0:7];

(二)程序代码

软件:Quartus II 9.0

module ROM(

input R,

input [2:0] addr,

output [7:0] data_out);

wire [7:0] rom[0:7];

assign rom[0] = 8'b0;

assign rom[1] = 8'b00000010;

assign rom[2] = 8'b00000100;

assign rom[3] = 8'b00000110;

assign rom[4] = 8'b00001000;

assign rom[5] = 8'b00001010;

assign rom[6] = 8'b00001100;

assign rom[7] = 8'b00001110;

assign data_out = !R ? rom[addr] : 8'bz;

endmodule

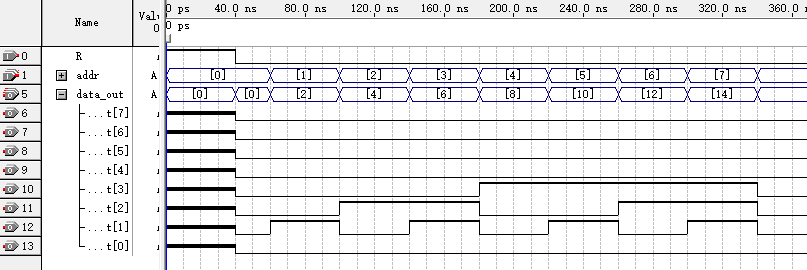

(三)时序模拟图

读控制端R为1时,输出data_out为高阻态。

读控制端R为0时,依次输出第0-7个地址对应的rom中的数据。

最后

以上就是漂亮自行车最近收集整理的关于verilog设计8x8位ROM一 设计思路二 verilog代码的全部内容,更多相关verilog设计8x8位ROM一内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复