文章目录

- RAM & ROM

- ROM:只读存储器

- 概念

- 源代码

- testbench

- 仿真波形

- RAM:随机访问内存

- 概念

- 源代码与testbench

- 仿真波形

RAM & ROM

ROM:只读存储器

概念

- ROM内部的数据是在ROM制造工序中,在工厂里用也输的方法被烧录进去的,其中的内容只能读不能改,一旦烧录进去,用户只能验证写入的资料是否正确,不能再做任何修改,如果发现资料有任何错误,则只能舍弃不用,重新订做一份,ROM是在生产线上生产的,由于成本高,一般只用在大批量应用的场合

源代码

module romv(dout,clk,addm,cs);

input clk;

input [2:0] addm;

input cs;

output [7:0] dout;

reg [7:0] dout;

reg [7:0]rom[7:0];

initial begin

rom[0]=8'b00000000;

rom[1]=8'b00000001;

rom[2]=8'b00000010;

rom[3]=8'b00000011;

rom[4]=8'b00000100;

rom[5]=8'b00000101;

rom[6]=8'b00000110;

rom[7]=8'b00000111;

end

always @(posedge clk)

if(cs)

dout<=8'bz;

else

dout<=rom[addm];

endmodule

testbench

module romv_tb;

reg clk,cs;

reg [2:0] addm;

wire [7:0] dout;

romv u2(dout,clk,addm,cs);

initial begin

clk=0;addm=0;cs=0;

end

always #10 clk=~clk;

initial begin

repeat(7) #20 addm=addm+1;

end

endmodule

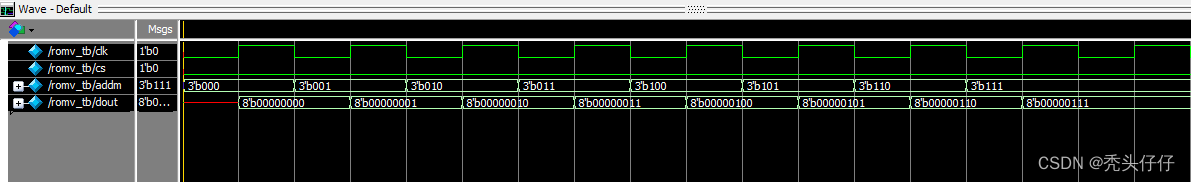

仿真波形

- 解释:

- 与RAM不同的是,RAM可以进行读写,而ROM只能对已经写好在内存地址的数据进行读取。所以在进行代码的编写时,要事先在相应地址写入一部分数据。在测试仿真阶段,若输入已写好数据的地址,将会在data输出端将其数据进行输出显示

RAM:随机访问内存

概念

- 随机访问内存(RAM)相当于PC机上的移动存储,用来存储和保存数据的。在任何时候都可以读写,RAM通常用作操作系统或其他正在运行的程序的临时存储介质(可称作系统内存)。不过,当电源关闭时时RAM不能保留数据,如果需要保存数据,就必须把它们写入到一个长期的存储器中(例如硬盘)。正因为如此,有时也将RAM称作"可变存储器"。RAM内存可以进一步分为静态RAM(SRAM)和动态内存(DRAM)两大类

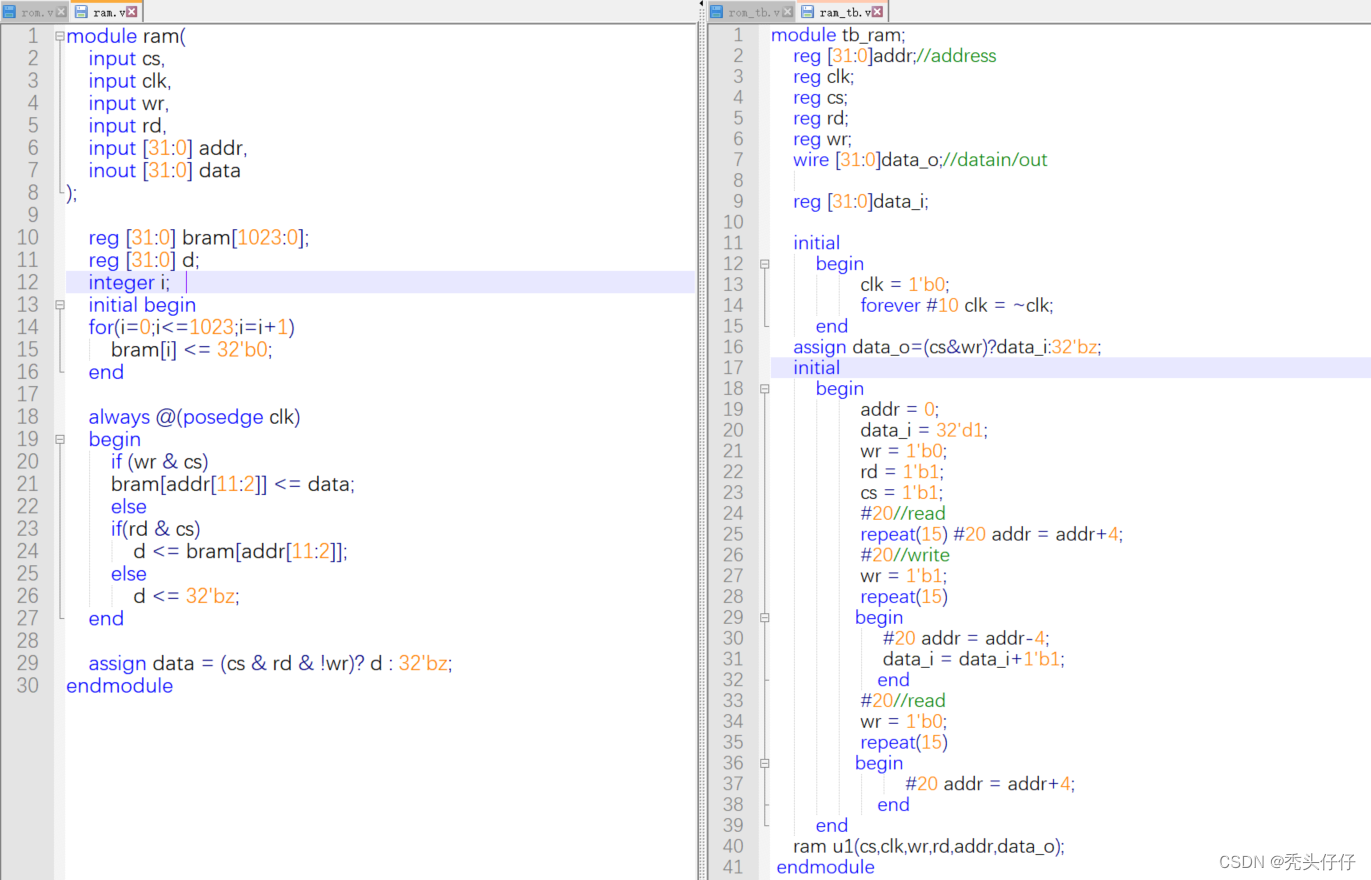

源代码与testbench

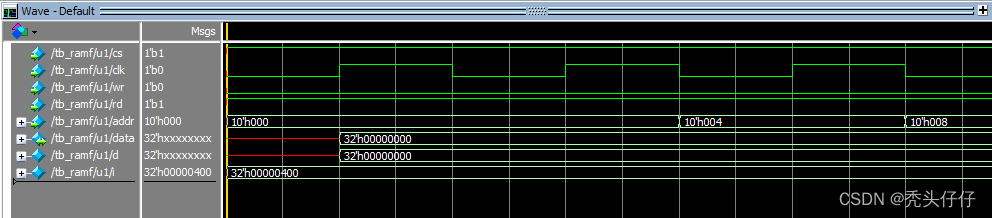

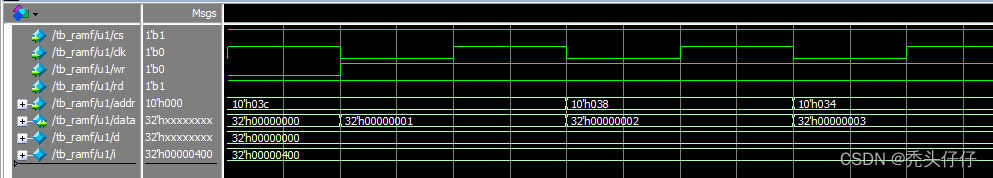

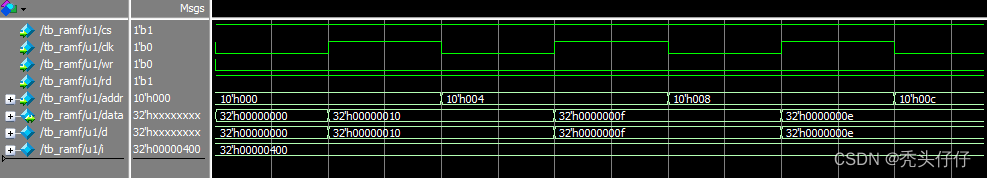

仿真波形

- 解释:

- RAM外部可见端口分别为一位的CS片选输入信号、一位的clk时钟输入信号、共计两位的wr/rd读写输入信号端口、32位的addr地址输入端口、32位的data数据写入/读出的输入输出双向端口

- 解释:

- 写有效时,数据可以从data输入端进行数据的输入,并且写入到指定的addr地址位置。在此处进行的测试代码直接将地址端随时钟信号进行递增,而所需输入到地址的data数据也进行给定测试

- 解释:

- 读有效时,地址可以从addr地址输入端进行读入,并且在相应的地址区域找到相应的数据,并由data数据输出端送出。若输入的地址有效且原本已经存入数据,则正常情况下应该在data中显示。由于data设定的位inout双向输入输出端口,故在进行读出操作时,需为代码设定一个临时缓冲变量,将所需传递的数据先赋值给临时缓冲变量,再通过三态门与条件运算符读出data

最后

以上就是激昂石头最近收集整理的关于【Verilog】ROM & RAM的全部内容,更多相关【Verilog】ROM内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复