我是靠谱客的博主 着急鱼,这篇文章主要介绍【Verilog数字系统设计——编程实现512x8的ROM和RAM】Verilog数字系统设计——编程实现512x8的ROM和RAM,现在分享给大家,希望可以做个参考。

Verilog数字系统设计——编程实现512x8的ROM和RAM

题目

- 编程实现512x8的ROM和RAM。

- ROM、RAM至少应该包含的端口包括地址线、数据线、片选线、读写使能端,复位端和时钟端(其中部分信号线只适用于RAM)。

- ROM、RAM和总测试模块分别包含在不同的.v文件中。

- 要求完成程序编辑、编译、时序仿真;

- 实验提交Verilog设计文件(.v文件)、仿真波形截图文件打包,压缩包以自己的学号+姓名命名;

- 一人提交一份作业文档,邮件方式提交,提交格式参见cs2.swfu.edu.cn/~ypy下的“上交作业.doc”(注意实验次数)、

代码

module myram(data,addr,clk,reset,wr_en,cs);

input clk,reset,wr_en,cs;

input [8:0]addr;

inout [7:0]data;

reg [7:0] temp;

reg [7:0] mymem [511:0];

integer i;

always @(posedge clk or negedge reset)

begin

if(!reset)

begin

for(i=0;i<512;i=i+1)

mymem[i] <= 0;

end

else if((cs==1'b1) &&(wr_en==1'b1))

begin

mymem[addr] <= data;

end

else if((cs==1'b1) &&(wr_en==1'b0))

begin

temp<=mymem[addr];

end

else

temp<=8'bzz;

end

assign data=wr_en?8'bzz:temp;

endmodule

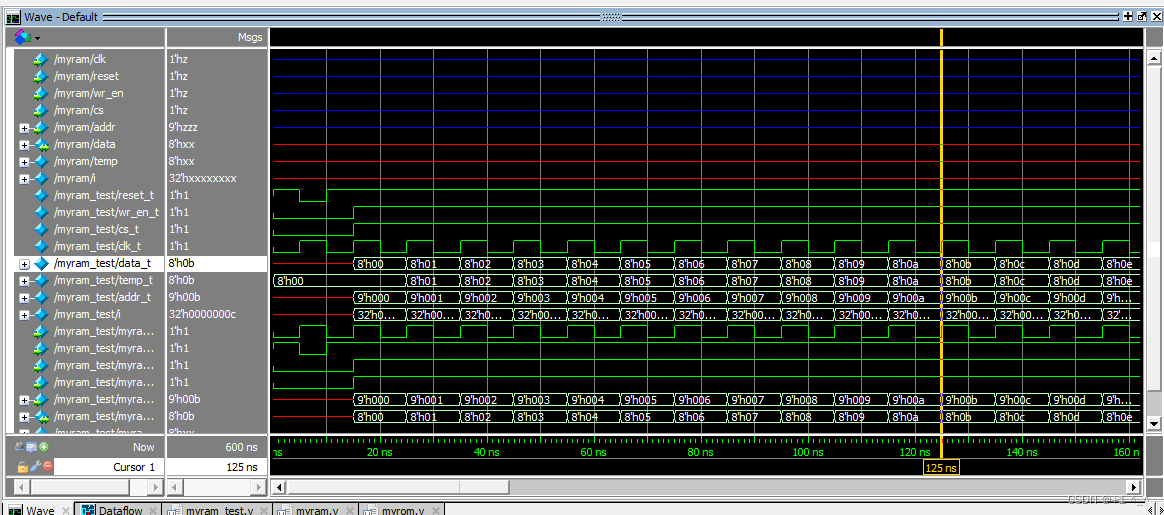

module myram_test;

reg reset_t,wr_en_t,cs_t,clk_t;

wire [7:0]data_t;

reg [7:0]temp_t;

reg [8:0]addr_t;

integer i;

myram myram(.data(data_t),.addr(addr_t),.clk(clk_t),.reset(reset_t),.wr_en(wr_en_t),.cs(cs_t));

initial

begin

reset_t=1;

wr_en_t=0;

cs_t=0;

clk_t=0;

temp_t=0;

#5

reset_t=0;

#5

reset_t=1;

#5

cs_t=1;

wr_en_t=1;

for (i = 0; i < 256; i = i + 1)

begin

@(posedge clk_t)

begin

addr_t = i;

temp_t =i;

end

end

#50

wr_en_t=0;

addr_t=0;

for (i = 0; i < 256; i = i + 1)

begin

@(posedge clk_t)

addr_t = i;

end

end

always #5 clk_t=~clk_t;

assign data_t=wr_en_t?8'bzz:temp_t;

endmodule

module myrom(data,addr,clk,reset,wr_en,cs);

input clk,reset,wr_en,cs;

input [8:0]addr;

output [7:0]data;

reg [7:0] data;

reg [7:0] mymem [511:0];

integer i;

always @(posedge clk or negedge reset)

begin

if(!reset)

begin

for(i=0;i<511;i=i+1)

mymem[i] <= i;

end

else if((cs==1'b1) &&(wr_en==1'b0))

begin

data<=mymem[addr];

end

else

data<=8'bzz;

end

//assign data=temp;

endmodule

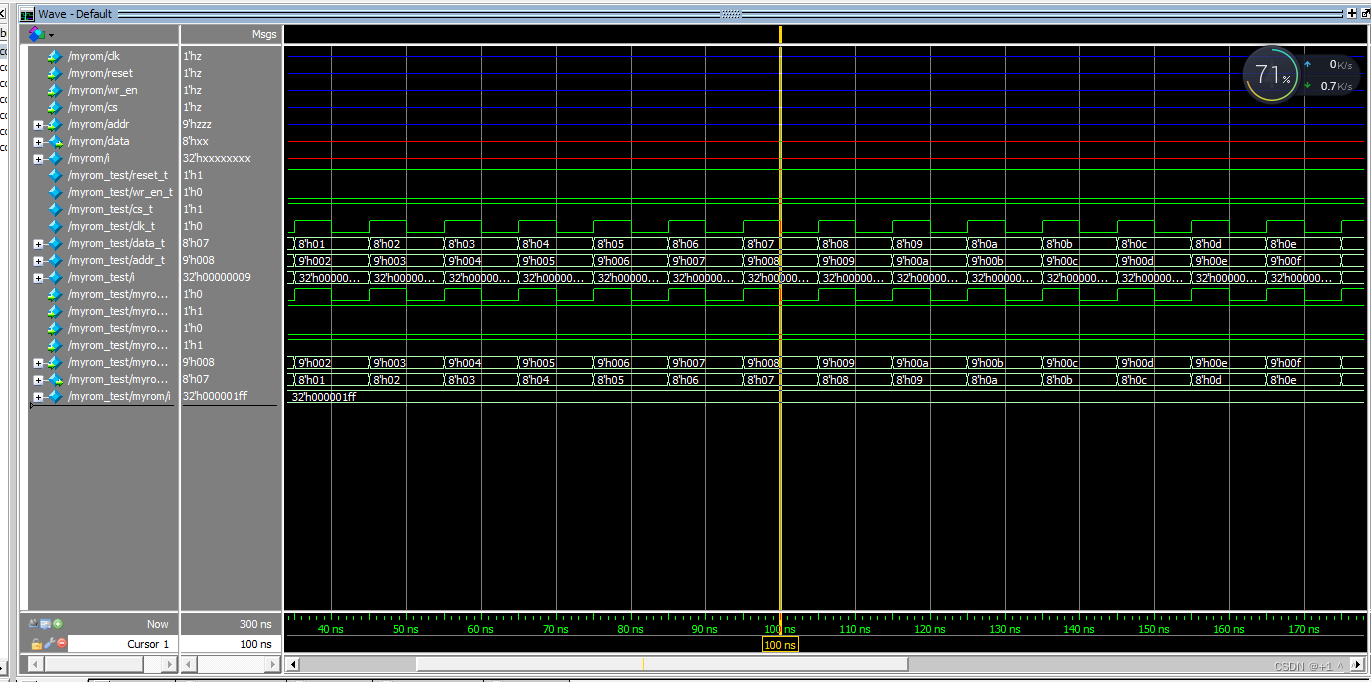

module myrom_test;

reg reset_t,wr_en_t,cs_t,clk_t;

wire [7:0]data_t;

reg [8:0]addr_t;

integer i;

myrom myrom(.data(data_t),.addr(addr_t),.clk(clk_t),.reset(reset_t),.wr_en(wr_en_t),.cs(cs_t));

initial

begin

reset_t=1;

wr_en_t=0;

cs_t=0;

clk_t=0;

#5

reset_t=0;

#5

reset_t=1;

cs_t=1;

wr_en_t=0;

addr_t=0;

for (i = 0; i < 256; i = i + 1)

begin

@(posedge clk_t)

begin

addr_t = i;

end

end

end

always #5 clk_t=~clk_t;

endmodule

最后

以上就是着急鱼最近收集整理的关于【Verilog数字系统设计——编程实现512x8的ROM和RAM】Verilog数字系统设计——编程实现512x8的ROM和RAM的全部内容,更多相关【Verilog数字系统设计——编程实现512x8内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复