二刷HDLBits发现自己可以独立做出这道题,来分享一下自己的解法。

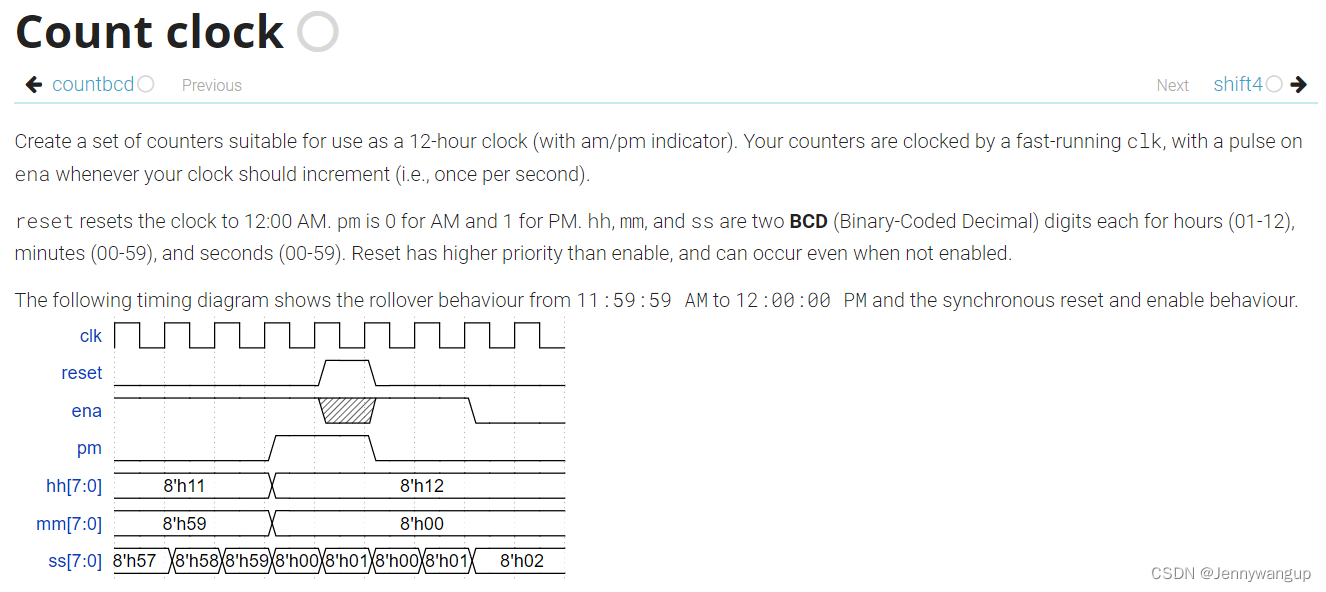

这道题主要难点就是计数器的十位和个位需要分开计数,如果直接按照八位一起计数就会产生十六进制的结果。

module top_module(

input clk,

input reset,

input ena,

output pm,

output [7:0] hh,

output [7:0] mm,

output [7:0] ss);

wire [2:0]num2;

assign num2[0] = ena;

assign num2[1] = (ss[7:4] == 4'd5) && (ss[3:0] == 4'd9) && ena;

assign num2[2] = (mm[7:4] == 4'd5 && mm[3:0] == 4'd9) && (ss[7:4] == 4'd5 && ss[3:0] == 4'd9) && ena;

always @ (posedge clk)begin

if(reset)begin

pm <= 1'b0;

hh[7:4] <= 4'd1;

hh[3:0] <= 4'd2;

end

else if(num2[2])begin

if(hh[7:4] == 4'd1 && hh[3:0] == 4'd2)begin

hh[7:4] <= 4'd0;

hh[3:0] <= 4'd1;

end

else begin

if(hh[7:4] == 4'd1 && (hh[3:0] == 4'd1 || hh[3:0] == 4'd0))begin

hh[3:0] <= hh[3:0] + 1'b1;

end

else if(hh[7:4] == 4'd0 && hh [3:0] == 4'd9)begin

hh[7:4] <= 4'd1;

hh[3:0] <= 4'd0;

end

else begin

hh [3:0]<= hh[3:0] + 1'b1;

end

if(hh[7:4] == 4'd1 && hh[3:0] == 4'd1 && num2[2])begin

pm <= ~pm;

end

end

end

end

fncount s1(.clk(clk), .reset(reset), .ena(num2[0]), .num1(ss));

fncount m1(.clk(clk), .reset(reset), .ena(num2[1]), .num1(mm));

endmodule

module fncount(

input clk,

input reset,

input ena,

output reg[7:0]num1);

always @ (posedge clk)begin

if(reset)begin

num1 <= 8'd0;

end

else if(ena)begin

if(num1[7:4] == 4'd5 && num1[3:0] == 4'd9)begin

num1[7:4] <= 4'd0;

num1[3:0] <= 4'd0;

end

else begin

if(num1[3:0] == 4'd9)begin

num1[3:0] <= 4'd0;

num1[7:4] <= num1[7:4] + 1'b1;

end

else begin

num1[3:0] <= num1[3:0] + 1'b1;

end

end

end

end

endmodule

最后

以上就是完美天空最近收集整理的关于HDLBits Count clock-12hour clock的全部内容,更多相关HDLBits内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复