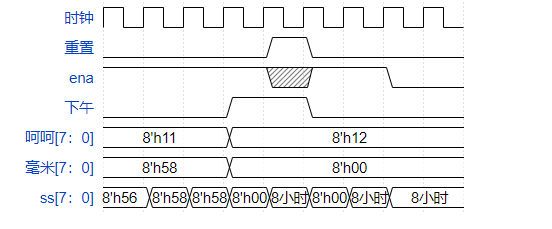

创建12小时制计数器。

当ena使能时(注意:复位最高优先级),时钟正常工作,否则始终所有状态不变

正常工作时,高电平同步复位,复位为12:00:00am,am时pm为0。

一个时钟秒加一,11:59:59时,下一个状态pm进行翻转,同时要设置计数器的进位

module top_module(

input clk,

input reset,

input ena,

output pm,

output [7:0] hh,

output [7:0] mm,

output [7:0] ss);

wire s0_reset,s1_reset,m0_reset,m1_reset,s0_s1,s1_m0,m0_m1,h0_in,h1_in;

wire[2:0] change;

assign s0_reset = (ena&ss[3:0]==9)?(1):(reset);

assign s1_reset = (ena&ss[7:4]==5&ss[3:0]==9)?(1):(reset);

assign m0_reset = (ena&mm[3:0]==9&s1_m0)?(1):(reset);

assign m1_reset = (ena&mm[7:4]==5&m0_m1)?(1):(reset);

assign s0_s1 = (ss[3:0]==9)?(1):(0);

assign s1_m0 = (ss[7:4]==5&ss[3:0]==9)?(1):(0);

assign m0_m1 = (mm[3:0]==9&s1_m0)?(1):(0);

assign h0_in = (mm[7:4]==5&m0_m1)?(1):(0);

assign h1_in = (hh[3:0]==9&h0_in)?(1):(0);

assign change = (hh[7:4]==1&hh[3:0]==2&h0_in)?(1):((hh[7:4]==1&hh[3:0]==1&h0_in)?(2):((hh[3:0]==9&h0_in)?(3):(0)));

nine_zero s0(clk,s0_reset,0,1,ena,ss[3:0]);

nine_zero s1(clk,s1_reset,0,s0_s1,ena,ss[7:4]);

nine_zero m0(clk,m0_reset,0,s1_m0,ena,mm[3:0]);

nine_zero m1(clk,m1_reset,0,m0_m1,ena,mm[7:4]);

always@(posedge clk)begin

if(reset)begin

hh[3:0]<=2;

hh[7:4]<=1;

pm<=0;

end

else begin

case (change)

2'b00:begin

hh[3:0] = hh[3:0] + h0_in;

hh[7:4] = hh[7:4] + h1_in;

end

2'b01:begin

hh[3:0]<=1;

hh[7:4]<=0;

end

2'b10:begin

pm<=~pm;

hh[3:0]<=2;

hh[7:4]<=1;

end

2'b11:begin

hh[3:0]<=0;

hh[7:4]<=1;

end

endcase

end

end

endmodule

module nine_zero(input clk,input reset,input reset_to,input in,input ena,output reg[3:0] out);

always@(posedge clk)begin

if(reset)begin

out<=reset_to;

end

else begin

if(!ena)begin

out<=out;

end

else begin

out<=out+in;

end

end

end

endmodule

最后

以上就是英勇荷花最近收集整理的关于HDLBits—Count clock的全部内容,更多相关HDLBits—Count内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复