常用数字二倍频电路介绍

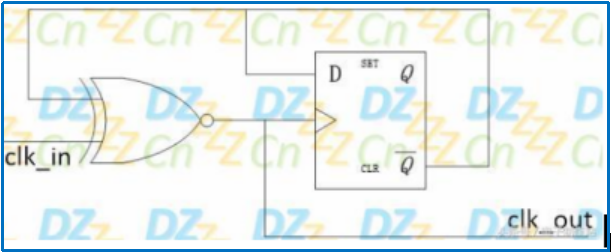

由一个同或门与一个时钟上升沿有效的D触发器(连接成翻转器)组成,其中clk_in为外部输入时钟周期信号,clk_out为二倍频输出信号。下图为其输入输出波形。

在t0时刻:(稳定状态)

clk_in为低电平,D触发器为复位状态(即Q=0、Q#=1),这样Q#与clk_in经"同或门"后为低电平(异出为0),此时为初始稳定状态,如下图所示:

当t1时刻到来时:(并非稳定状态)

clk_in时钟变为高电平,此时D触发器尚未翻转,“同或门"另一输入引脚亦仍为高电平,则"同或门"输出转变为高电平(同出为"1”),同时此输出作为有效时钟上升沿触发D触发器翻转,则有Q=1、Q#=0,如下图所示:

当t2时刻到来:(稳定状态)

之后每次输入信号变化一次,则重复一次稳定状态、不稳定状态、稳定状态的变化。从D触发器翻转输出至"同或门"输出变化那一段时间,称为延时(Tdelay),在这个电路里也就是高电平宽度。在74系列逻辑器件中,这个延时值大约为几十个纳秒(ns),在可编程逻辑(FPGA/CPLD中)则只有几个纳秒,可以通过在这个延时链路上插入多个缓冲器来增加高电平的宽度(也就是占空比)。

Verilog HDL语言描述电路

-

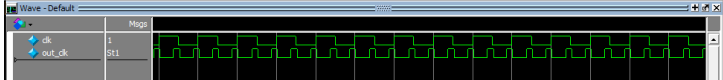

常用方法

module frequency_multiplier ( input clk, output out_clk ); reg temp_mul; assign out_clk = ~(clk ^ ~temp_mul); always @(posedge out_clk) begin temp_mul <= ~temp_mul ; end endmodulemodelsim 后仿真结果(必须用后仿真)

-

在脉冲频率不足100k(步进电机控制频率<<500k)的情况下还可以采用高频检测输入脉冲信号的上升沿和下降沿加延时5us实现倍频功能

module frequency_multiplier ( input clk, input rst_n, input clk_in, output clk_out, output wire pos_edge, output wire neg_edge, output wire both_edge, output ref_clk ); assign ref_clk = clk_in; reg clkin_r0, clkin_r1; // 状态寄存器 always @ (posedge clk or negedge rst_n)begin if (!rst_n) begin clkin_r0 <= 1'b0; clkin_r1 <= 1'b0; end else begin clkin_r0 <= clk_in; clkin_r1 <= clkin_r0; end end wire clkin_sign; //wire pos_edge,neg_edge,both_edge; assign pos_edge = (~clkin_r1)& ( clkin_r0); assign neg_edge = clkin_r1 & (~clkin_r0); assign both_edge = clkin_r1 ^ clkin_r0; // 双边沿检测,或pos_edge|neg_edge assign clkin_sign = ~both_edge; reg [31:0] counter; always @(posedge clk or negedge clkin_sign) begin if (!clkin_sign) counter <= 0; else if (counter >= 32'd1000) //检测到沿后延时5us counter <= 32'd1000; else counter <= counter + 1; end assign clk_out =(counter == 32'd1000)? 0 : 1; endmodule

最后

以上就是缥缈热狗最近收集整理的关于数字二倍频电路的全部内容,更多相关数字二倍频电路内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复