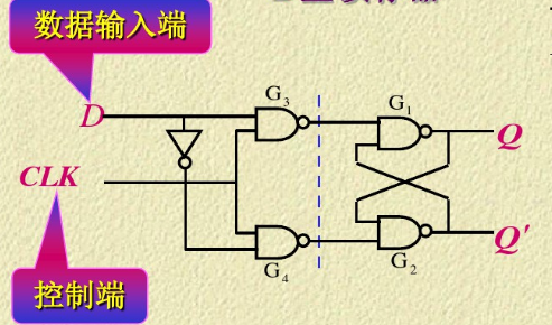

D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

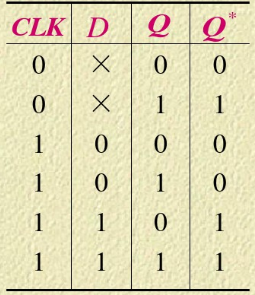

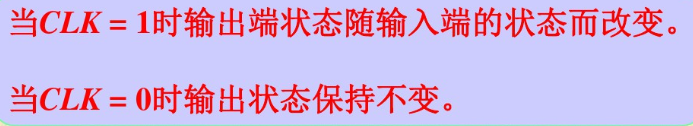

真值表:

特征方差程:

verilog代码:

module d(clk,d,q);

input d,clk;

output q;

reg q;

always @(d,clk)

if(clk)

q <= d;

endmodule

测试程序:

`timescale 1 ns/1ps

module d_tb;

reg D,CLK;

wire Q;

d Df(CLK,D,Q);

always #10 CLK=~CLK;

initial

begin

D=1'b0;CLK=1'b0;

#10 D=1'b1;

#15 D=1'b0;

#20 D=1'b1;

#25 D=1'b0;

#20 $stop;

end

endmodule

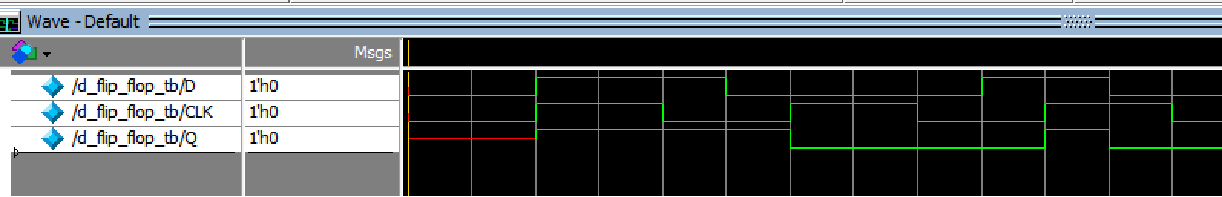

仿真结果:

从图中可以看出,CLK低电平时Q保持不变,CLK高电平时输出Q与输入D相同。

注意:always @(d,clk)正确

always @(clk)错误

括号里面为敏感信号,如果不包含d,那么在CLK不变的情况下,q就感应不到d的变化,q的值就不正确!!!

最后

以上就是感动指甲油最近收集整理的关于电平触发的D触发器 Verilog的全部内容,更多相关电平触发的D触发器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复