1,http://blog.sina.com.cn/s/blog_72c14a3d010150m4.html

erilog入门经验(一) always块使用

https://blog.csdn.net/phenixyf/article/details/46364193如果我们把按键的输出做为一个时钟域(时钟频率未知,但信号的slow rate是已知的,既最大20ms左右)的信号,用另外一个时钟来采集这个按键的输出,则就可以把按键的消抖归结为一个最基本的CDC问题来处理。而问题的核心是如何确定采集时钟的频率。假设采集时钟的周期小于20ms,那么,采集时钟就有可能两次采到按键断开时的不确定的值,就没有办法避免采用CDC电路所想避免的问题。所以采集时钟的周期必须要大于20ms。假设采集时钟的周期大于120ms的话,就有可能采不到按键的闭合信号,所以采集时钟的周期必须小于120ms。我们在这里选用周期为25ms的采集时钟(频率为40Hz)。

下面的verilog实现实际上是一个标准的CDC电路,直接可以用来做按键的消抖。

module RMV_BJ (

BJ_CLK, //采集时钟,40Hz

RESET, //系统复位信号

BUTTON_IN, //按键输入信号

BUTTON_OUT //消抖后的输出信号

);

input B_CLK;

input RESET;

input BUTTON_IN;

output BUTTON_OUT;

reg BUTTON_IN_Q, BUTTON_IN_2Q, BUTTON_IN_3Q;

always @(posedge BJ_CLK or negedge RESET)

begin

if(~RESET)

begin

BUTTON_IN_Q <= 1'b1;

BUTTON_IN_2Q <= 1'b1;

BUTTON_IN_3Q <= 1'b1;

end

else

begin

BUTTON_IN_Q <= BUTTON_IN;

BUTTON_IN_2Q <= BUTTON_IN_Q;

BUTTON_IN_3Q <= BUTTON_IN_2Q;

end

end

wire BUTTON_OUT = BUTTON_IN_2Q | BUTTON_IN_3Q;

endmodule

主要对Q1,Q2,Q3讲解下。

前提条件,当按下后的持续低电平(BUTTON_IN=0)时间不低于120ms

当按键按下后,BUTTON_IN=0,此时

t=0 ms,Q1=BUTTON_IN=0;Q2=1;Q3=1;

t=25 ms,Q1=BUTTON_IN=0;Q2<=Q1=0;Q3=1;

t=50 ms,Q1=BUTTON_IN=0;Q2<=Q1=0;Q3<=Q2=0;

wire BUTTON_OUT = BUTTON_IN_2Q | BUTTON_IN_3Q=0|0=0;输出低电平

2,verilog中关于并行处理的心得

https://blog.csdn.net/jiangbeicaizi000/article/details/52093945

并行处理的对象的值都是此时刻之前的值

3,http://www.stepfpga.com/doc/7._%E6%8C%89%E9%94%AE%E6%B6%88%E6%8A%96

// Module Function:按键消抖

module debounce (clk,rst,key,key_pulse);

parameter N = 1; //要消除的按键的数量

input clk; //系统时钟

input rst; //复位信号

input [N-1:0] key; //输入的按键

output [N-1:0] key_pulse; //按键动作产生的脉冲

reg [N-1:0] key_rst_pre; //定义一个寄存器型变量存储上一个触发时的按键值

reg [N-1:0] key_rst; //定义一个寄存器变量储存储当前时刻触发的按键值

wire [N-1:0] key_edge; //检测到按键由高到低变化是产生一个高脉冲

//利用非阻塞赋值特点,将两个时钟触发时按键状态存储在两个寄存器变量中

always @(posedge clk or negedge rst)

begin

if (!rst) begin

key_rst <= {N{1'b1}}; //初始化时给key_rst赋值全为1,{}中表示N个1

key_rst_pre <= {N{1'b1}};

end

else begin

key_rst <= key; //第一个时钟上升沿触发之后key的值赋给key_rst,同时key_rst的值赋给key_rst_pre

key_rst_pre <= key_rst; //非阻塞赋值。相当于经过两个时钟触发,key_rst存储的是当前时刻key的值,key_rst_pre存储的是前一个时钟的key的值

end

end

assign key_edge = key_rst_pre & (~key_rst);//脉冲边沿检测。当key检测到下降沿时,key_edge产生一个时钟周期的高电平

reg [17:0] cnt; //产生延时所用的计数器,系统时钟12MHz,要延时20ms左右时间,至少需要18位计数器

//产生20ms延时,当检测到key_edge有效是计数器清零开始计数

always @(posedge clk or negedge rst)

begin

if(!rst)

cnt <= 18'h0;

else if(key_edge)

cnt <= 18'h0;

else

cnt <= cnt + 1'h1;

end

reg [N-1:0] key_sec_pre; //延时后检测电平寄存器变量

reg [N-1:0] key_sec;

//延时后检测key,如果按键状态变低产生一个时钟的高脉冲。如果按键状态是高的话说明按键无效

always @(posedge clk or negedge rst)

begin

if (!rst)

key_sec <= {N{1'b1}};

else if (cnt==18'h3ffff)

key_sec <= key;

end

always @(posedge clk or negedge rst)

begin

if (!rst)

key_sec_pre <= {N{1'b1}};

else

key_sec_pre <= key_sec;

end

assign key_pulse = key_sec_pre & (~key_sec);

endmodule

4,

【读书笔记】详细解析基于FPGA的独立按键消抖

http://blog.chinaaet.com/lincoding/p/5100050183

5,FPGA最小系统http://www.cnblogs.com/crazybingo/archive/2011/07/26/2117116.html

6,

Verilog中同步复位和异步复位比较

点击打开链接

https://blog.csdn.net/kobesdu/article/details/16356997

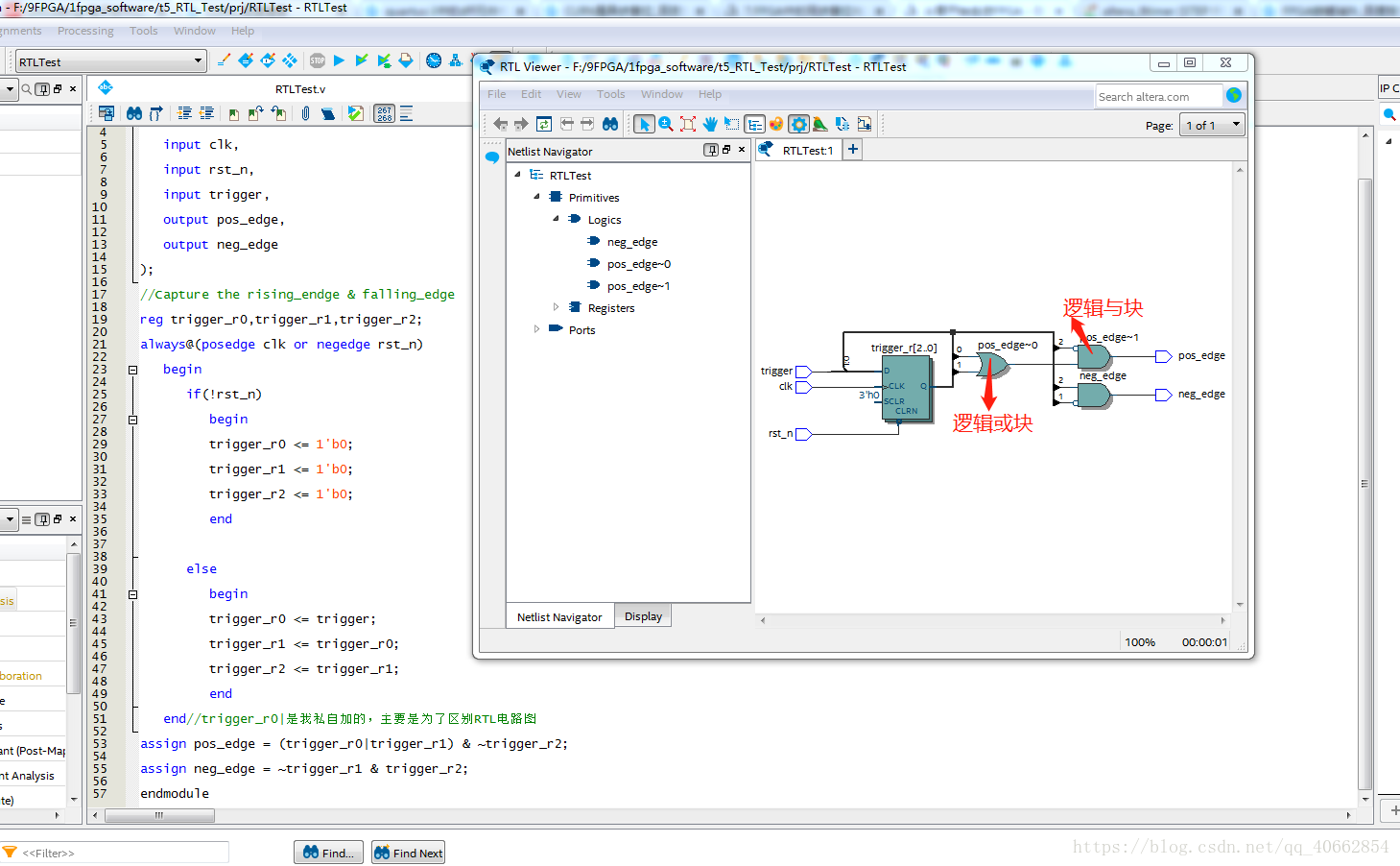

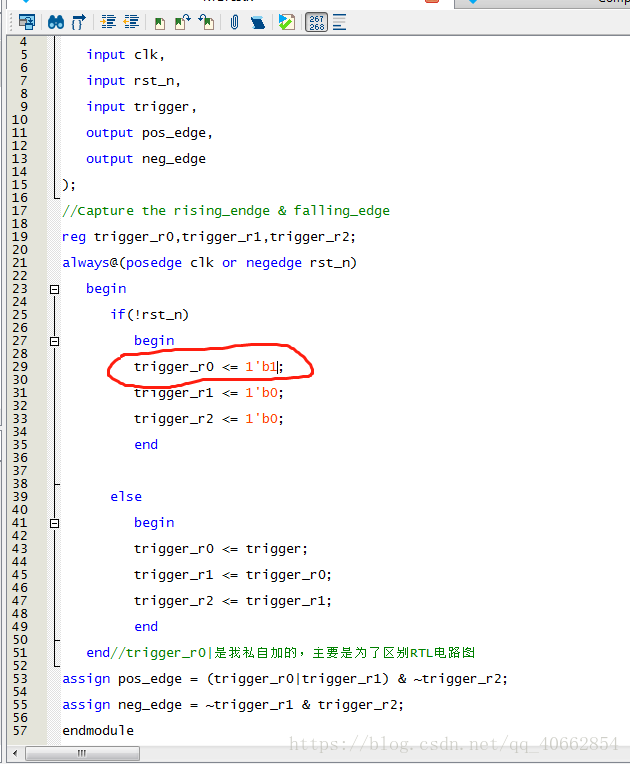

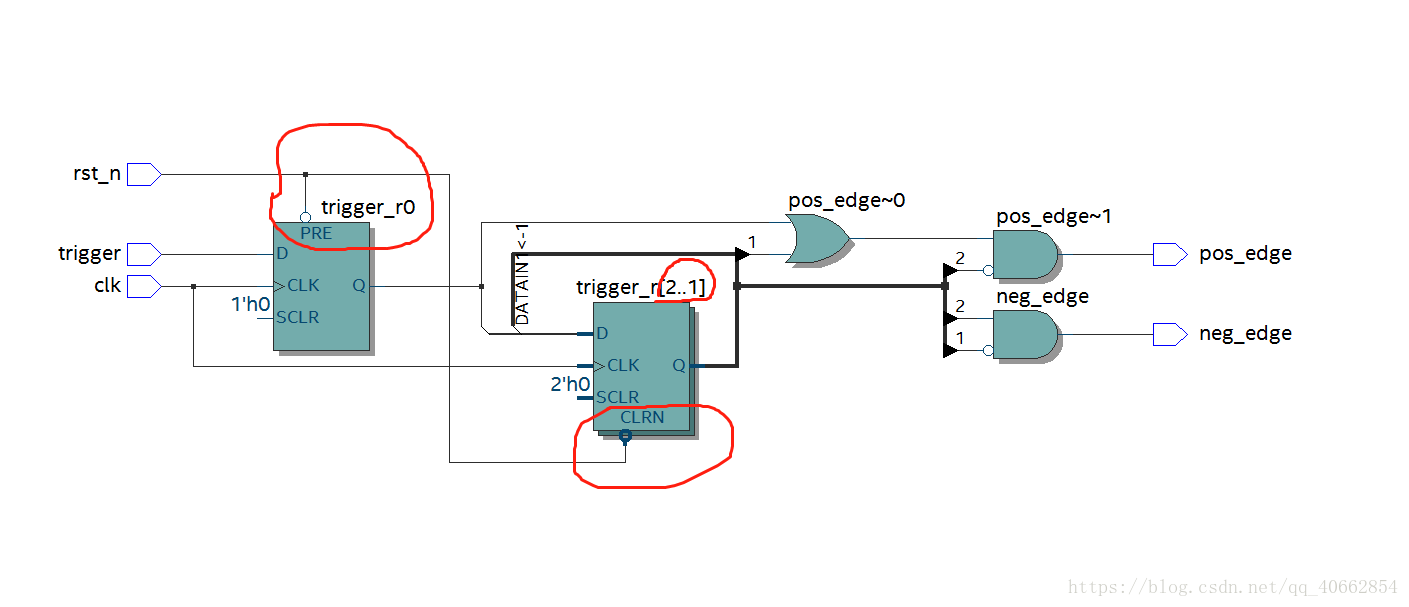

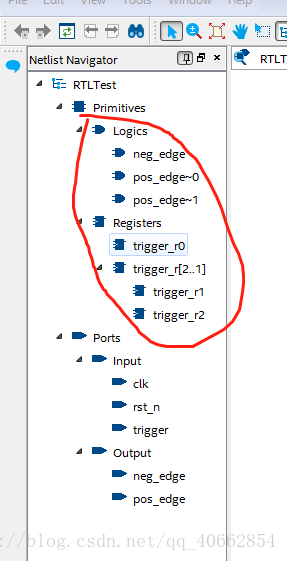

7,实验操作

当把0改成1后

变化

8,Verilog 4位 二选一 多路选择器

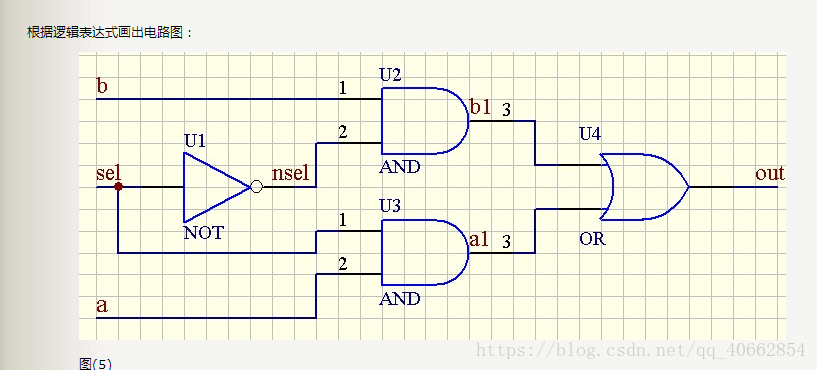

https://www.cnblogs.com/zxl2431/archive/2010/09/17/1829603.html

下面这个图可以看到NOT,AND,OR的图形表示

这位博主的这几个触发器等器件不错

随笔分类 - FPGA小练习

勿在浮沙建高楼加法器,乘法器综合以后会是什么样子?

posted @ 2012-12-15 11:27 zxl2431 阅读(213) | 评论 (0) 编辑

啥子是LUT

posted @ 2010-12-08 17:04 zxl2431 阅读(2389) | 评论 (1) 编辑

DE2上SRAM测试(一)

posted @ 2010-12-06 15:18 zxl2431 阅读(878) | 评论 (3) 编辑

Verilog 串口实验

posted @ 2010-12-04 14:40 zxl2431 阅读(869) | 评论 (0) 编辑

简单的人机界面——LCD1602+PS2

posted @ 2010-11-06 22:34 zxl2431 阅读(587) | 评论 (0) 编辑

Calculator

posted @ 2010-11-05 16:52 zxl2431 阅读(148) | 评论 (0) 编辑

FPGA经典模块(1)——分频器

posted @ 2010-10-25 13:44 zxl2431 阅读(3005) | 评论 (0) 编辑

简单状态机设计(2)

posted @ 2010-10-09 20:34 zxl2431 阅读(218) | 评论 (0) 编辑

简单状态机设计(1)

posted @ 2010-10-07 16:26 zxl2431 阅读(5042) | 评论 (5) 编辑

基本时序逻辑电路练习

posted @ 2010-09-24 21:13 zxl2431 阅读(1300) | 评论 (0) 编辑

基本组合逻辑电路练习

posted @ 2010-09-19 21:32 zxl2431 阅读(4445) | 评论 (0) 编辑

用Verilog HDL的三种建模方式描述——2选1数据选择器

posted @ 2010-09-17 21:32 zxl2431 阅读(16052) | 评论 (0) 编辑

按照缺氧老兄的博客modelsim仿真成功

posted @ 2010-09-15 22:41 zxl2431 阅读(407) | 评论 (1) 编辑

Powered by:

博客园

https://www.cnblogs.com/zxl2431/category/261884.html

随笔分类 - FPGA小练习

勿在浮沙建高楼加法器,乘法器综合以后会是什么样子?

posted @ 2012-12-15 11:27 zxl2431 阅读(213) | 评论 (0) 编辑

啥子是LUT

posted @ 2010-12-08 17:04 zxl2431 阅读(2389) | 评论 (1) 编辑

DE2上SRAM测试(一)

posted @ 2010-12-06 15:18 zxl2431 阅读(878) | 评论 (3) 编辑

Verilog 串口实验

posted @ 2010-12-04 14:40 zxl2431 阅读(869) | 评论 (0) 编辑

简单的人机界面——LCD1602+PS2

posted @ 2010-11-06 22:34 zxl2431 阅读(587) | 评论 (0) 编辑

Calculator

posted @ 2010-11-05 16:52 zxl2431 阅读(148) | 评论 (0) 编辑

FPGA经典模块(1)——分频器

posted @ 2010-10-25 13:44 zxl2431 阅读(3005) | 评论 (0) 编辑

简单状态机设计(2)

posted @ 2010-10-09 20:34 zxl2431 阅读(218) | 评论 (0) 编辑

简单状态机设计(1)

posted @ 2010-10-07 16:26 zxl2431 阅读(5042) | 评论 (5) 编辑

基本时序逻辑电路练习

posted @ 2010-09-24 21:13 zxl2431 阅读(1300) | 评论 (0) 编辑

基本组合逻辑电路练习

posted @ 2010-09-19 21:32 zxl2431 阅读(4445) | 评论 (0) 编辑

用Verilog HDL的三种建模方式描述——2选1数据选择器

posted @ 2010-09-17 21:32 zxl2431 阅读(16052) | 评论 (0) 编辑

按照缺氧老兄的博客modelsim仿真成功

posted @ 2010-09-15 22:41 zxl2431 阅读(407) | 评论 (1) 编辑

最后

以上就是积极信封最近收集整理的关于【FPGA】4,按键的消抖,verilog中关于并行处理的心得,FPGA最小系统,Verilog中同步复位和异步复位比较erilog入门经验(一) always块使用【读书笔记】详细解析基于FPGA的独立按键消抖的全部内容,更多相关【FPGA】4,按键的消抖,verilog中关于并行处理的心得,FPGA最小系统,Verilog中同步复位和异步复位比较erilog入门经验(一)内容请搜索靠谱客的其他文章。

发表评论 取消回复