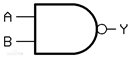

1. 与非门

与非门(NAND gate)是数字逻辑中实现逻辑与非的逻辑门。

真值表:

A | B | Y |

0 | 0 | 1 |

0 | 1 | 0 |

1 | 0 | 0 |

1 | 1 | 0 |

与非门是一种通用的逻辑门,因为任何布尔函数都能用与非门实现。

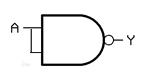

实现非门:

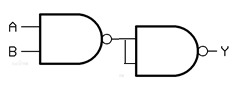

实现与门:

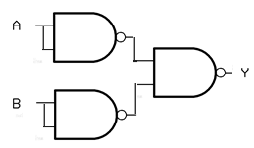

实现或门:

2. 数据选择器

数据选择器(MUX)的逻辑功能是在地址选择信号的控制下,从多路数据中选择一路数据作为输出信号。

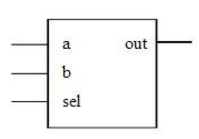

下图所示为二选一数据选择器原理图,a、b为输入端,sel为控制端,out为输出端

实现的功能为:

sel=0时,out=a;

sel=1时,out=b;

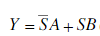

可以得到逻辑表达式:

可以得到电路逻辑图:

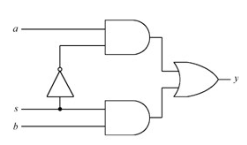

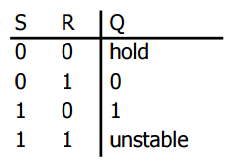

3. RS锁存器

结合与非门的真值表,可知:

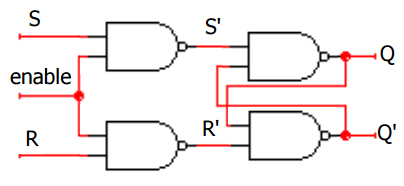

4. 门控RS锁存器

enable=1时,相当于RS锁存器;

enable=0时,相当于hold

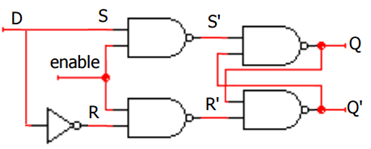

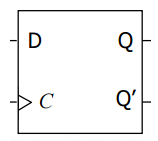

5. D锁存器

为了避免出现unstable的情况:

Enable=1时,Qn+1=D

Enable=0时,Qn+1=Qn

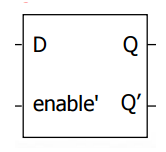

封装D锁存器,得到:

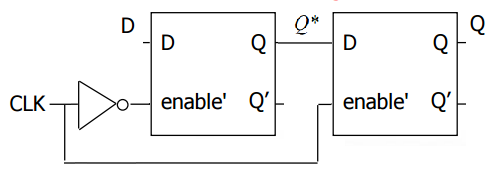

6. D触发器

由两个D锁存器,可以得到D触发器

CLK=0时,D值传递至Q*;CLK=1时,Q*值传递至Q;即CLK为上边沿时,D值可以传递至Q

封装D触发器,可以得到:

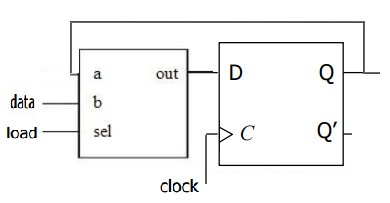

7. 简单寄存器

Clock为时钟信号,可以确保寄存器同步工作;

Data为数据输入端,当load=0时,保持;当load=1时,输入数据data;

可见,该简单寄存器是实现RAM的基础。

最后

以上就是缓慢汽车最近收集整理的关于从与非门到寄存器的全部内容,更多相关从与非门到寄存器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复