一、D触发器

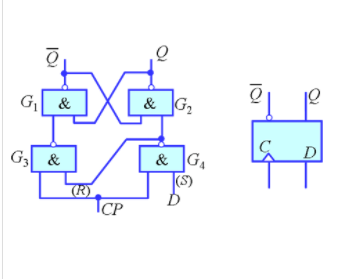

1.结构

2.工作原理

SD和RD接至基本RS触发器的输入端,它们分别是预置和清零端,低电平有效。当SD=1且RD=0时(SD的非为0,RD的非为1,即在两个控制端口分别从外部输入的电平值,原因是低电平有效),不论输入端D为何种状态,都会使Q=0,Q非=1,即触发器置0;当SD=0且RD=1(SD的非为1,RD的非为0)时,Q=1,Q非=0,触发器置1,SD和RD通常又称为直接置1和置0端。我们设它们均已加入了高电平,不影响电路的工作。

3.特征

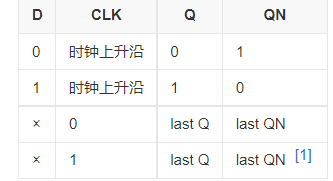

①功能表

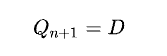

②方程

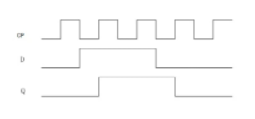

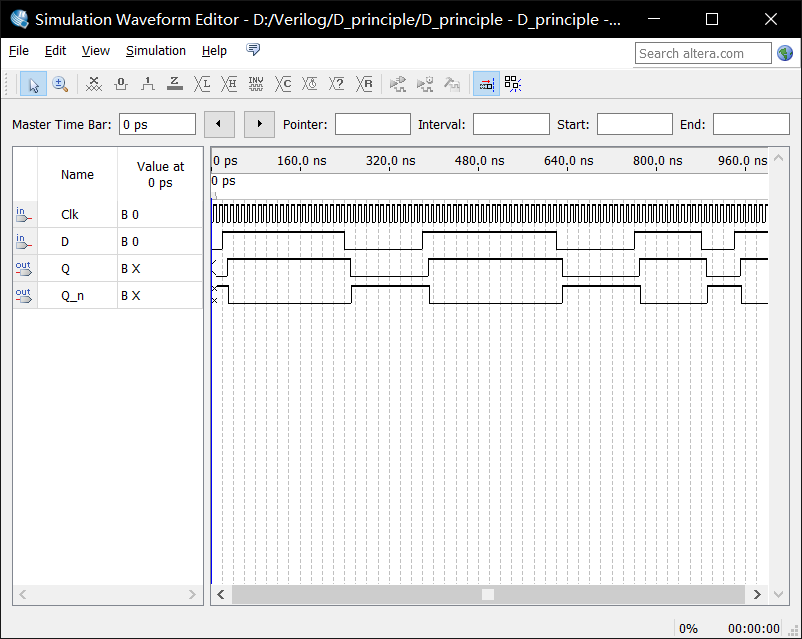

③时序图

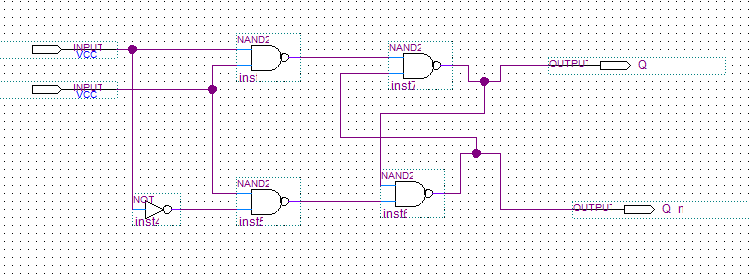

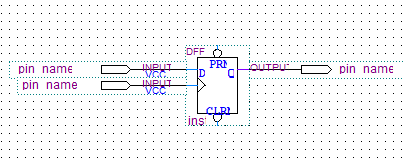

二、D触发器原理图并仿真

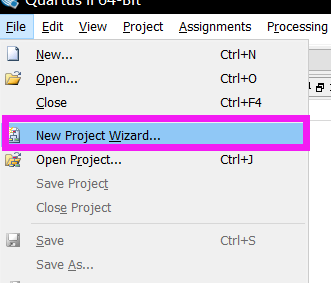

1.新建工程

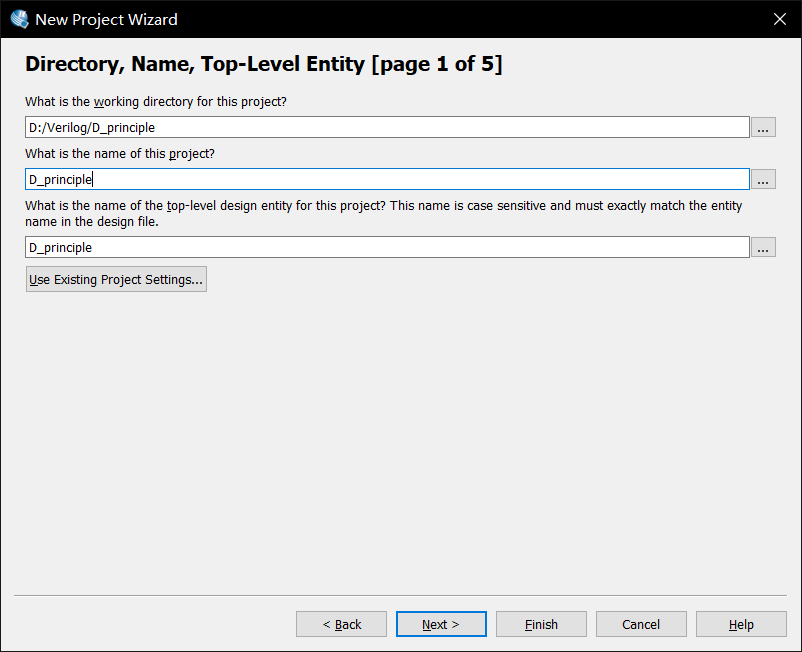

2.选择路径及项目名称等

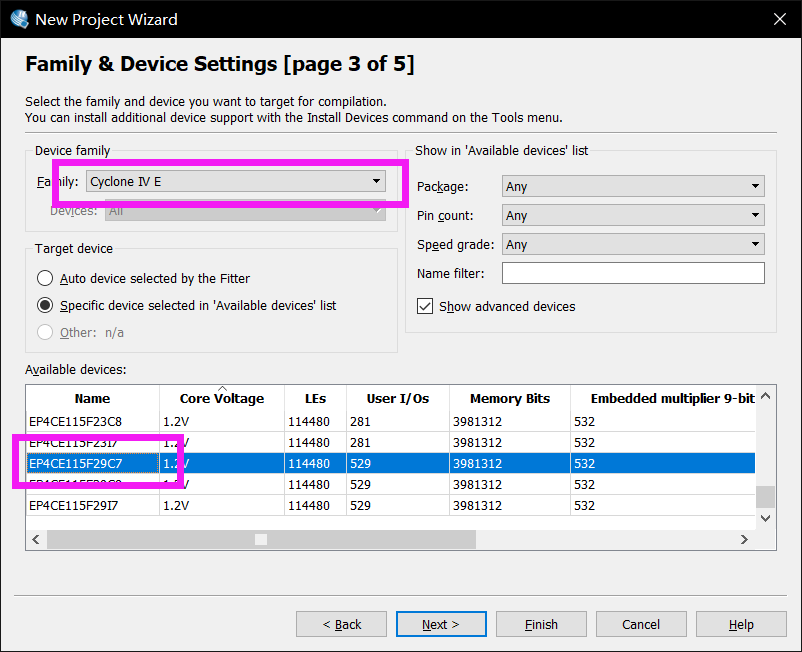

3.选择芯片直接next到finish

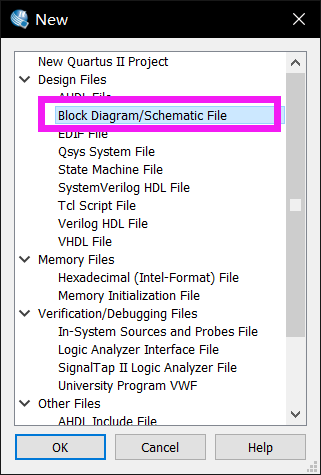

4.

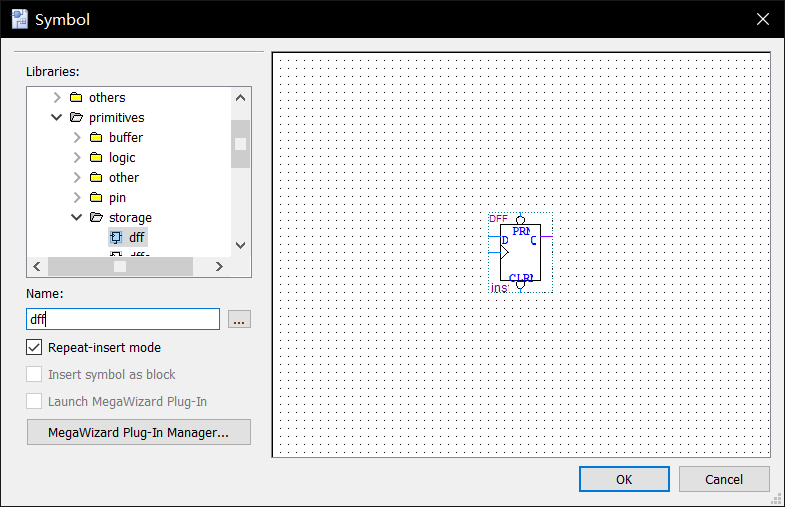

5.选择元器件

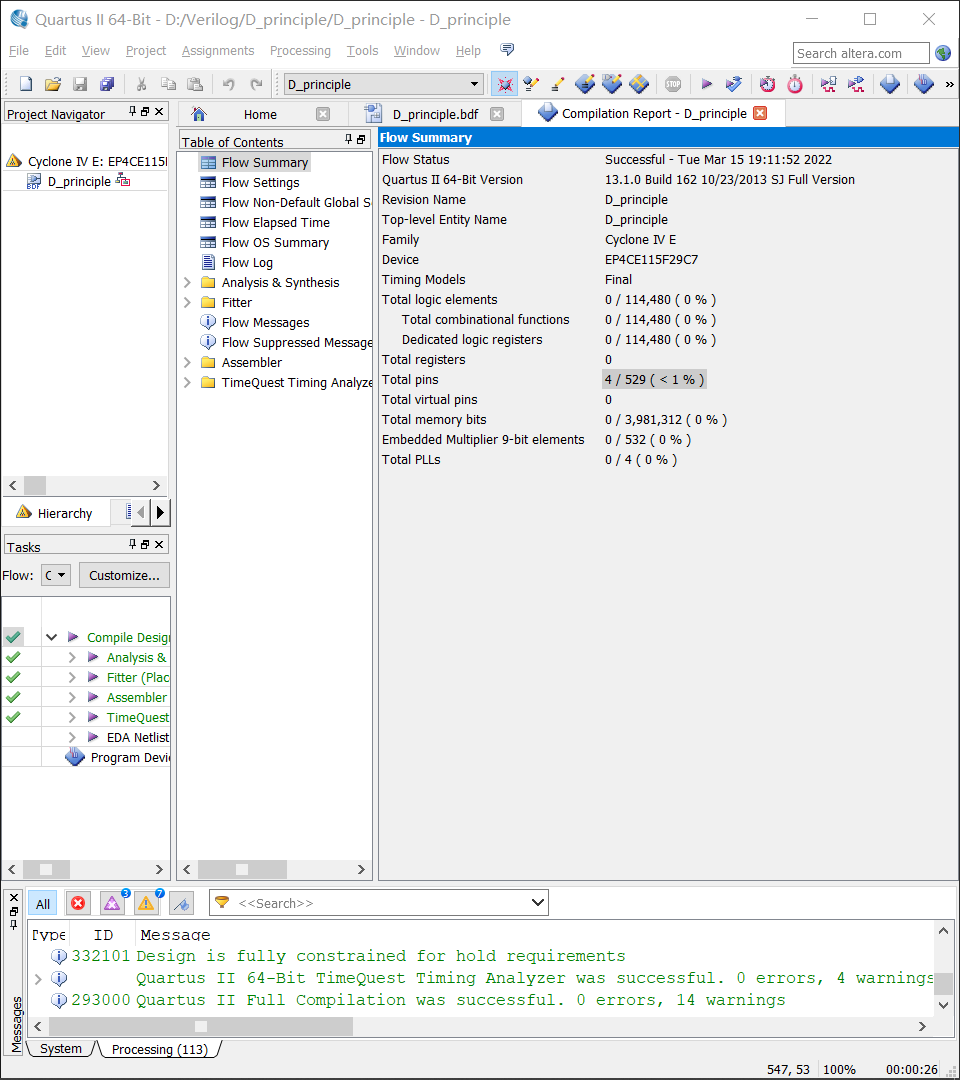

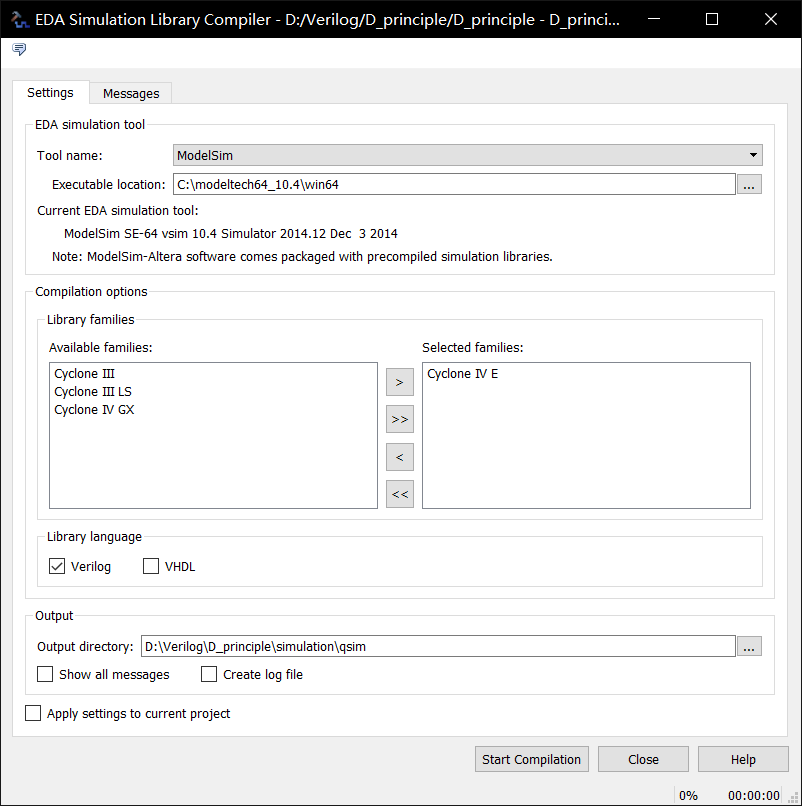

6.编译

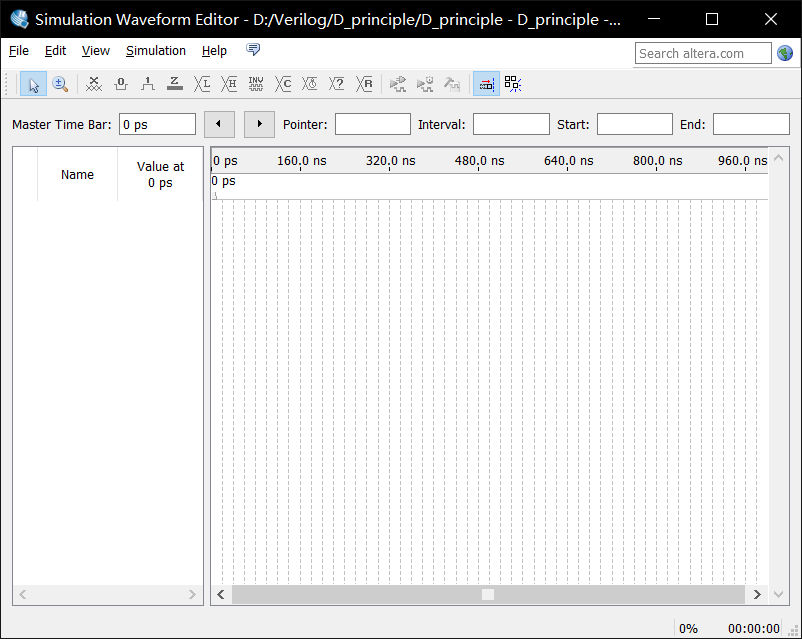

7.选择新建文件,选择VWF文件

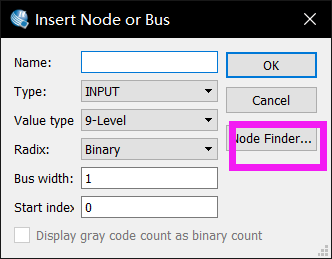

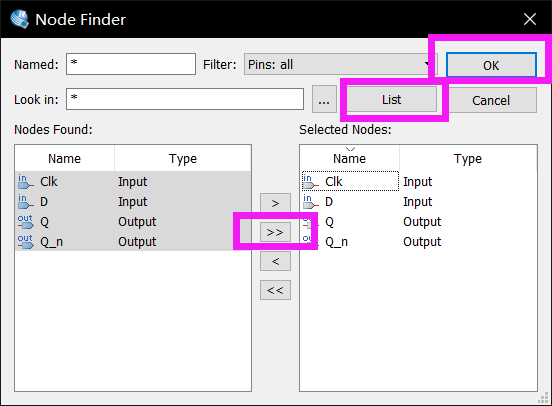

双击左边空白

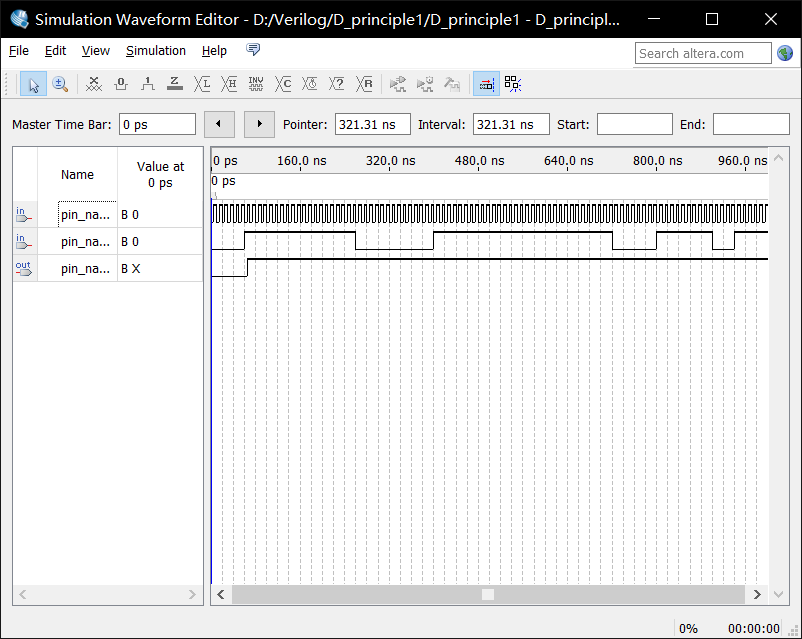

三、调用D触发器仿真

1.重复之前的步骤

2.创建vwf文件并按照之前的步骤运行

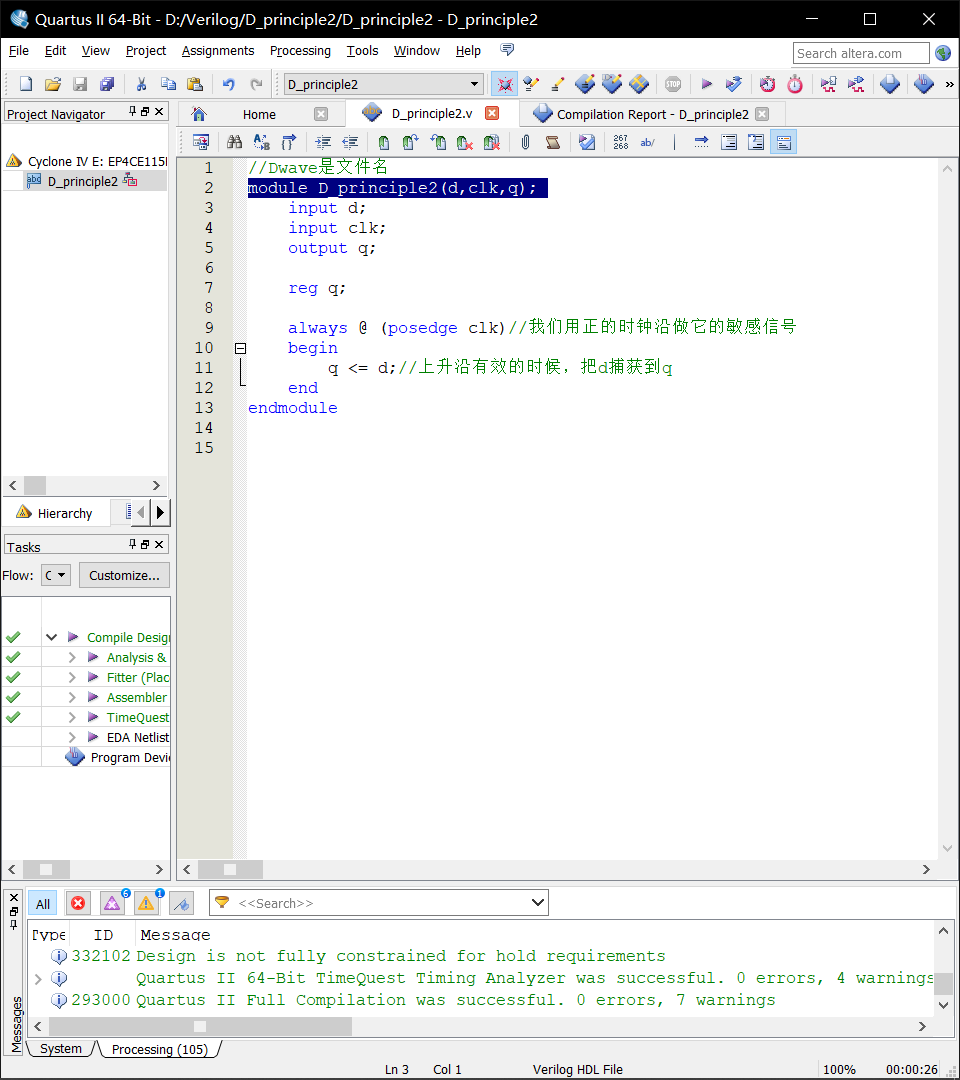

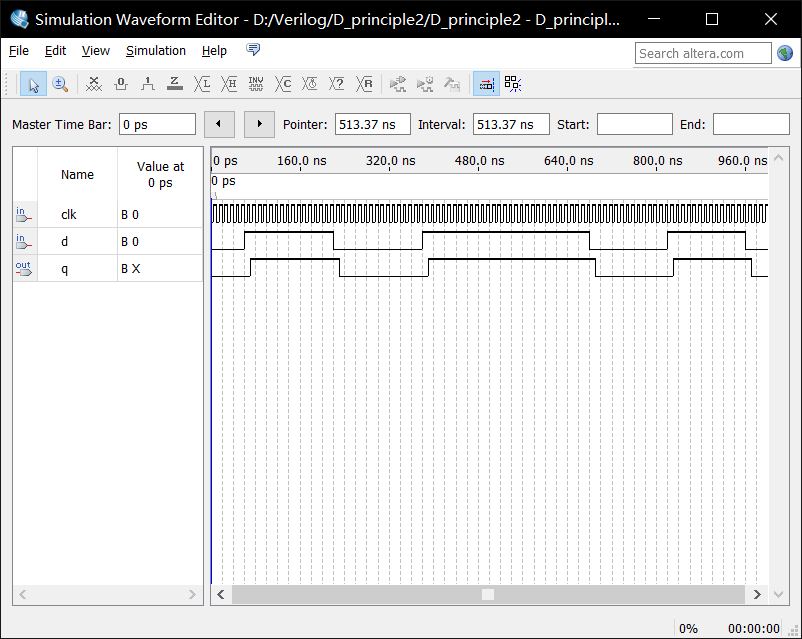

四、verilog实现D触发器

1.创建新项目

2.写入代码并运行

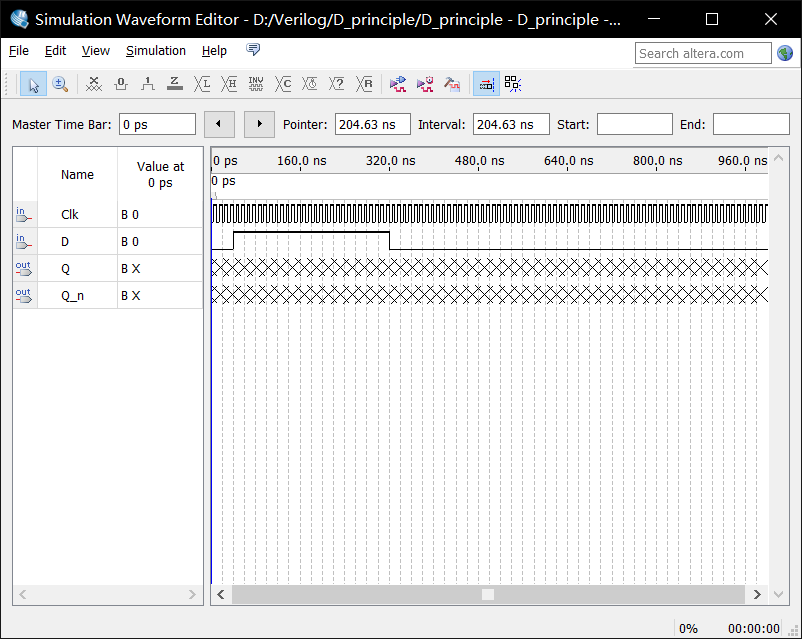

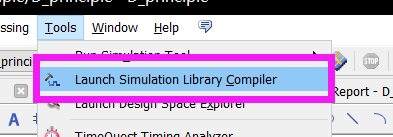

3.编译之后也是波形仿真

最后

以上就是大气夕阳最近收集整理的关于Quartus-II 三种方式进行D触发器仿真的全部内容,更多相关Quartus-II内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复