代码段

module Top(

input ST,

input CLR,

input clk_25M,

output [3:0] AN,

output [7:0] SEG

);

reg[15:0] Data;

reg[3:0] Data_Show;

wire[1:0] BIT_SEL;

reg Increment;

integer clk_num=0;

delay_2ms uu1(clk_25M,BIT_SEL);

initial begin Data <= 16'b0; Increment = 1'b0;end

always@(posedge clk_25M)begin

if(clk_num<5000000) begin

clk_num = clk_num+1;

Increment = 1'b0;

end

else begin

clk_num = 0;

Increment = 1'b1;

end

end

always@(posedge CLR or posedge Increment)

if(CLR) begin

Data <= 16'b0000000000000000;

end

else if(ST) begin

if(Data[3:0]==4'b1001) begin

Data[3:0]<=4'b0000;

if(Data[7:4]==4'b1001) begin

Data[7:4]<=4'b0000;

if(Data[11:8]==4'b1001)begin

Data[11:8]<=4'b0000;

if(Data[15:12]==4'b1001)

Data[15:12]<=4'b0000;

else

Data[15:12]<=Data[15:12]+4'b0001;

end

else

Data[11:8]<=Data[11:8]+4'b0001;

end

else

Data[7:4]<=Data[7:4]+4'b0001;

end

else

Data[3:0]<=Data[3:0]+4'b0001;

end

always @(*) begin

case(BIT_SEL)

0:Data_Show[3:0]<=Data[15:12];

1:Data_Show[3:0]<=Data[11:8];

2:Data_Show[3:0]<=Data[7:4];

3:Data_Show[3:0]<=Data[3:0];

default:Data_Show[3:0]<=Data[3:0];

endcase

end

SMG uu2(Data_Show,BIT_SEL,SEG,AN);

endmodule

module delay_2ms(

input clk_25M,

output reg[1:0] BIT_SEL

);

integer cnt=0;

initial begin BIT_SEL <= 2'b00; end

always@(posedge clk_25M) begin

cnt<=cnt+1;

if(cnt>50000) begin

BIT_SEL<=BIT_SEL+2'b01;

cnt<=0;

end

end

endmodule

module SMG(

input wire[3:0] Data,

input wire[1:0] Bit_sel,

output reg[7:0] Seg,

output reg[3:0] AN

);

always @(*) begin

case(Bit_sel)

2'b00:AN<=4'b1000;

2'b01:AN<=4'b1001;

2'b10:AN<=4'b1010;

2'b11:AN<=4'b1011;

default:AN<=4'b1111;

endcase

end

always @(*) begin

case(Data[3:0])

0:Seg[7:0]<=8'b00000011;

1:Seg[7:0]<=8'b10011111;

2:Seg[7:0]<=8'b00100101;

3:Seg[7:0]<=8'b00001101;

4:Seg[7:0]<=8'b10011001;

5:Seg[7:0]<=8'b01001001;

6:Seg[7:0]<=8'b01000001;

7:Seg[7:0]<=8'b00011111;

8:Seg[7:0]<=8'b00000001;

9:Seg[7:0]<=8'b00001001;

10:Seg[7:0]<=8'b00010001;

11:Seg[7:0]<=8'b11000001;

12:Seg[7:0]<=8'b01100011;

13:Seg[7:0]<=8'b10000101;

14:Seg[7:0]<=8'b01100001;

15:Seg[7:0]<=8'b01110001;

default:Seg[7:0]<=8'b11111111;

endcase

end

endmodule

测试文件

module test;

// Inputs

reg ST;

reg CLR;

reg clk_25M;

// Outputs

wire [3:0] AN;

wire [7:0] SEG;

// Instantiate the Unit Under Test (UUT)

Top uut (

.ST(ST),

.CLR(CLR),

.clk_25M(clk_25M),

.AN(AN),

.SEG(SEG)

);

always #20 clk_25M=~clk_25M;

initial begin

CLR = 0;

ST= 0;

clk_25M = 0;

#100;

CLR = 0;

ST= 1;

end

endmodule

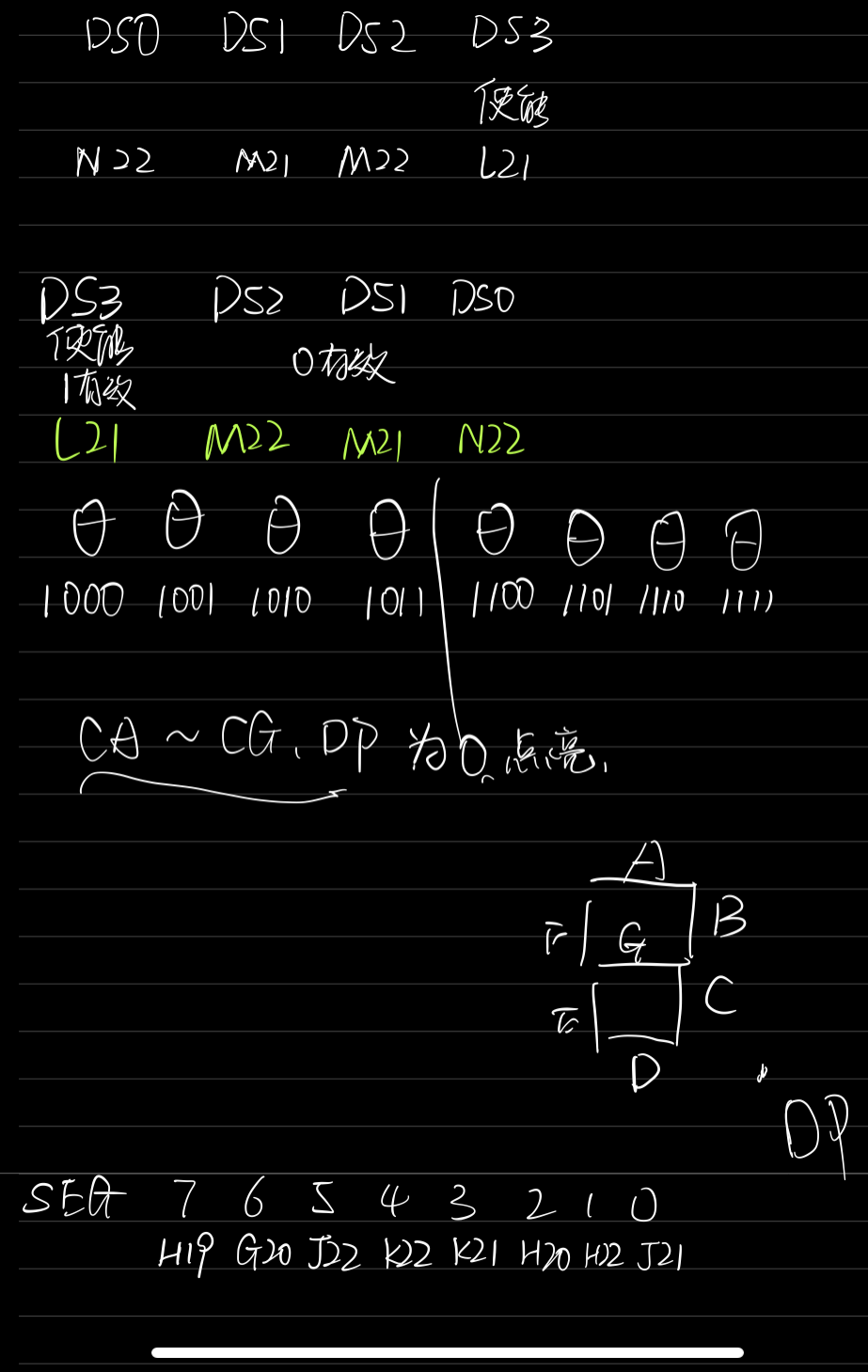

管脚配置

# PlanAhead Generated IO constraints

NET "AN[3]" IOSTANDARD = LVCMOS18;

NET "AN[2]" IOSTANDARD = LVCMOS18;

NET "AN[1]" IOSTANDARD = LVCMOS18;

NET "AN[0]" IOSTANDARD = LVCMOS18;

NET "SEG[7]" IOSTANDARD = LVCMOS18;

NET "SEG[6]" IOSTANDARD = LVCMOS18;

NET "SEG[5]" IOSTANDARD = LVCMOS18;

NET "SEG[4]" IOSTANDARD = LVCMOS18;

NET "SEG[3]" IOSTANDARD = LVCMOS18;

NET "SEG[2]" IOSTANDARD = LVCMOS18;

NET "SEG[1]" IOSTANDARD = LVCMOS18;

NET "SEG[0]" IOSTANDARD = LVCMOS18;

NET "clk_25M" IOSTANDARD = LVCMOS18;

NET "CLR" IOSTANDARD = LVCMOS18;

NET "ST" IOSTANDARD = LVCMOS18;

# PlanAhead Generated physical constraints

NET "clk_25M" LOC = H4;

NET "CLR" LOC = T3;

NET "ST" LOC = U3;

# PlanAhead Generated IO constraints

NET "CLR" PULLDOWN;

NET "ST" PULLDOWN;

# PlanAhead Generated physical constraints

NET "AN[3]" LOC = L21;

NET "AN[2]" LOC = M22;

NET "AN[1]" LOC = M21;

NET "AN[0]" LOC = N22;

NET "SEG[7]" LOC = H19;

NET "SEG[6]" LOC = G20;

NET "SEG[5]" LOC = J22;

NET "SEG[4]" LOC = K22;

NET "SEG[3]" LOC = K21;

NET "SEG[2]" LOC = H20;

NET "SEG[1]" LOC = H22;

NET "SEG[0]" LOC = J21;

最后

以上就是热情雪碧最近收集整理的关于数电实验18:数码管扫描显示的全部内容,更多相关数电实验18内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复