数码管动态扫描显示电路设计

一、实验目的

1. 学习动态显示数码管的使用。

2. 学习数据选择器及其信号分配方法。

二、基本实验内容

用 Verilog HDL 设计一个 4 位数码管动态扫描显示电路,在实验箱的数码管上固定显示 2022。

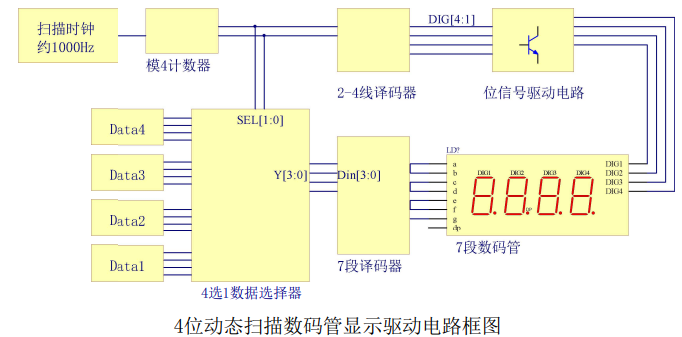

实验电路框图如下:

三、代码实现

顶层模块:

module zwm_1898_10(clk,en,DIG,seg,codeout,Y,Q);

input clk,en;//时钟和使能信号

output [1:0] Q;//计数信号

output [3:0] Y;

output [3:0] DIG;//位选信号

output [6:0] codeout;//七段数码管译码信号

output [3:0] seg;//位选信号

//调用子模块

zwm_1898_10_1 a(clk,Q,en);

zwm_1898_10_2 b(.x(Q),.DIG(DIG),.seg(seg));

zwm_1898_10_3 c(.SEL(Q),.Y(Y));

zwm_1898_10_4 d(.Din(Y),.codeout(codeout));

endmodule4计数器模块:

module zwm_1898_10_1(clk,Q,en);//4计数器

input clk,en;

output reg[1:0]Q;

always @(posedge clk)

if(en==1'b1)

begin

if(Q==2'd3)

Q<=2'd0;

else

Q<=2'd1+Q;

end

endmodule2-4线译码器:

module zwm_1898_10_2(x,DIG,seg);//2-4线译码器

input [1:0] x;

output reg[3:0] DIG;//位选信号

output [3:0]seg;//位选信号

assign seg=4'b0000;

always @(x)

begin

case(x)

2'd0:DIG <= 4'b0001;//数码管位1亮

2'd1:DIG <= 4'b0010;//数码管位2亮

2'd2:DIG <= 4'b0100;//数码管位3亮

2'd3:DIG <= 4'b1000;//数码管位4亮

default:DIG <= 4'bx;

endcase

end

endmodule4选1数据选择器:

module zwm_1898_10_3(SEL,Y);//数据选择器

input [1:0] SEL;

output reg[3:0] Y;

always @(SEL)

begin

case(SEL)

2'd0:Y <= 4'b0010;

2'd1:Y <= 4'b0010;

2'd2:Y <= 4'b0000;

2'd3:Y <= 4'b0010;

default: Y <=4'bx;

endcase

end

endmodule七段译码器:

module zwm_1898_10_4 (codeout, Din); //译码器

input[3:0] Indec;

output[6:0] codeout;

reg [6:0]codeout;

always@(Din)

begin

case(Din)

4'd0 : codeout=7'b1111110;

4'd1 : codeout=7'b0110000;

4'd2 : codeout=7'b1101101;

4'd3 : codeout=7'b1111001;

4'd4 : codeout=7'b0110011;

4'd5 : codeout=7'b1011011;

4'd6 : codeout=7'b1011111;

4'd7 : codeout=7'b1110000;

4'd8 : codeout=7'b1111111;

4'd9 : codeout=7'b1111011;

default: codeout=7'bx;

endcase

end

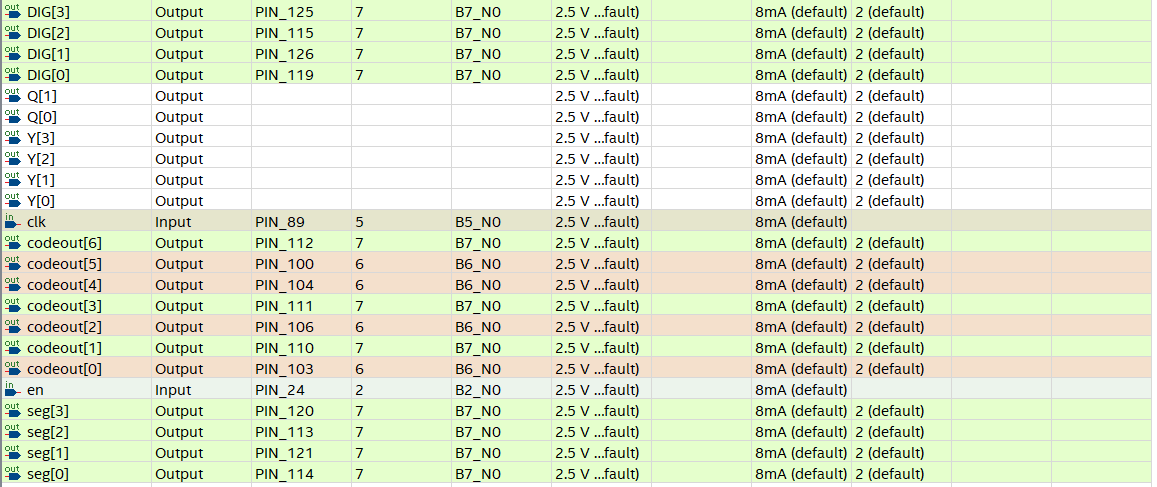

endmodule四、引脚分配

最后

以上就是健康鸭子最近收集整理的关于数码管动态扫描显示电路设计的全部内容,更多相关数码管动态扫描显示电路设计内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复