二进制优先级编码器设计

- 实验目的

- 实验要求

- 实验原理

- 程序代码

- 测试用例

- 仿真波形图

- 电路管脚图

- 引脚配置文件

- 工程文件

实验目的

- 学习二进制优先级编码器的原理与设计方法

- 掌握灵活运用Verilog HDL语言进行各种描述与建模的技巧和方法

实验要求

- 使用合适的表述方式实现3位二进制优先级编码器。

- 课前任务:在Xilinx ISE上完成创建工程、编辑程序源代码、编程、综合、仿真、验证,确保逻辑正确性。

- 实验室任务:配置管脚,生成*.bit文件,完成板级验证。

- 撰写实验报告。

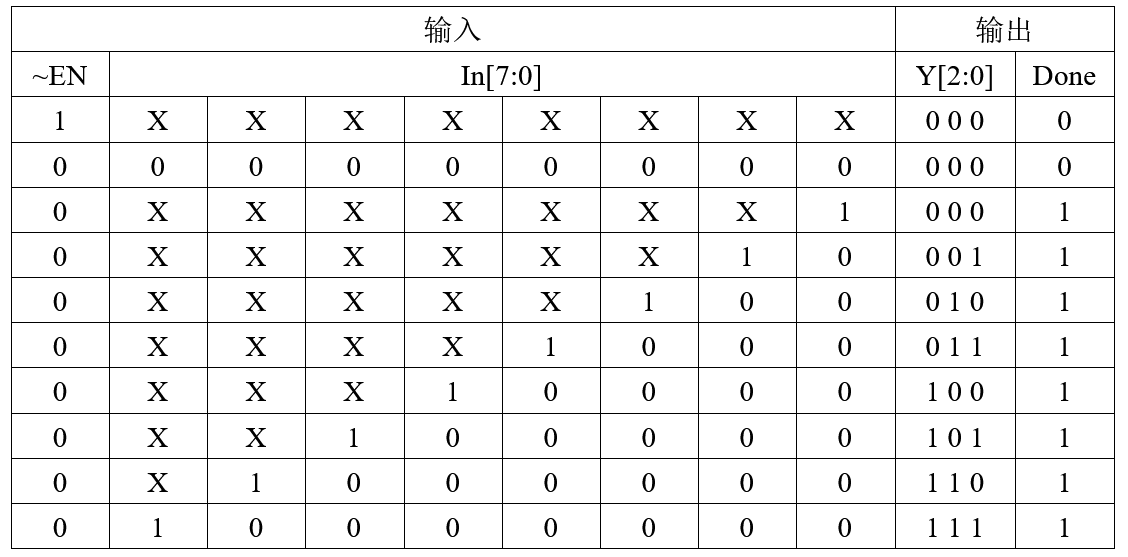

实验原理

当使能信号输入为0时,二进制译码器开始工作,对于输入为1的位,按照优先级顺序进行编码输出,若输出有效则Done输出为1。

程序代码

module yxj(IN,EN,Y,Done);

input[7:0] IN;

input EN;

output reg Done;

output reg[2:0] Y;

always @(IN or EN)

if(!EN)

begin

if(IN[0]) begin Y[2]=0;Y[1]=0;Y[0]=0; Done=0;end

else if(IN[1]) begin Y[2]=0;Y[1]=0;Y[0]=1; Done=1;end

else if(IN[2]) begin Y[2]=0;Y[1]=1;Y[0]=0; Done=1;end

else if(IN[3]) begin Y[2]=0;Y[1]=1;Y[0]=1; Done=1;end

else if(IN[4]) begin Y[2]=1;Y[1]=0;Y[0]=0; Done=1;end

else if(IN[5]) begin Y[2]=1;Y[1]=0;Y[0]=1; Done=1;end

else if(IN[6]) begin Y[2]=1;Y[1]=1;Y[0]=0; Done=1;end

else if(IN[7]) begin Y[2]=1;Y[1]=1;Y[0]=1; Done=1;end

else begin Y[2]=0;Y[1]=0;Y[0]=0;Done=0;end

end

else begin Y[2]=0;Y[1]=0;Y[0]=0;Done=0;end

endmodule

测试用例

initial begin

IN = 0;EN = 0;

#100;

EN=1; IN[0]=1;IN[1]=0;IN[2]=0;IN[3]=0;IN[4]=0;IN[5]=0;IN[6]=0;IN[7]=0;

#100;

EN=0; IN[0]=0;IN[1]=1;IN[2]=0;IN[3]=0;IN[4]=0;IN[5]=0;IN[6]=0;IN[7]=0;

#100;

EN=0; IN[0]=0;IN[1]=0;IN[2]=1;IN[3]=0;IN[4]=0;IN[5]=0;IN[6]=0;IN[7]=0;

#100;

EN=0; IN[0]=0;IN[1]=0;IN[2]=0;IN[3]=1;IN[4]=0;IN[5]=0;IN[6]=0;IN[7]=0;

#100;

EN=0; IN[0]=0;IN[1]=0;IN[2]=0;IN[3]=0;IN[4]=1;IN[5]=0;IN[6]=0;IN[7]=0;

#100;

EN=0; IN[0]=0;IN[1]=0;IN[2]=0;IN[3]=0;IN[4]=0;IN[5]=1;IN[6]=0;IN[7]=0;

#100;

EN=0; IN[0]=0;IN[1]=0;IN[2]=0;IN[3]=0;IN[4]=0;IN[5]=0;IN[6]=1;IN[7]=0;

#100;

EN=0; IN[0]=0;IN[1]=0;IN[2]=0;IN[3]=0;IN[4]=0;IN[5]=0;IN[6]=0;IN[7]=1;

#100;

EN=0; IN[0]=1;IN[1]=0;IN[2]=0;IN[3]=0;IN[4]=0;IN[5]=0;IN[6]=0;IN[7]=1;

#100;

EN=0; IN[0]=1;IN[1]=0;IN[2]=0;IN[3]=0;IN[4]=0;IN[5]=0;IN[6]=0;IN[7]=1;

end

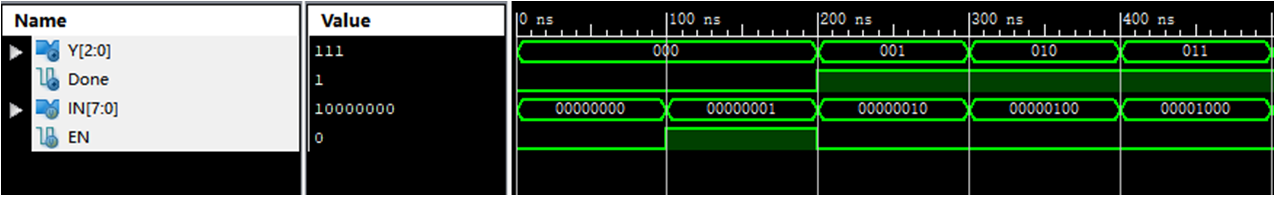

仿真波形图

从波形图可以看出:

当EN=0时,Y[2:0]会根据IN[7:0]的输入值按照优先级产生不同输出

因此该模块实现了二进制优先级编码器的功能。

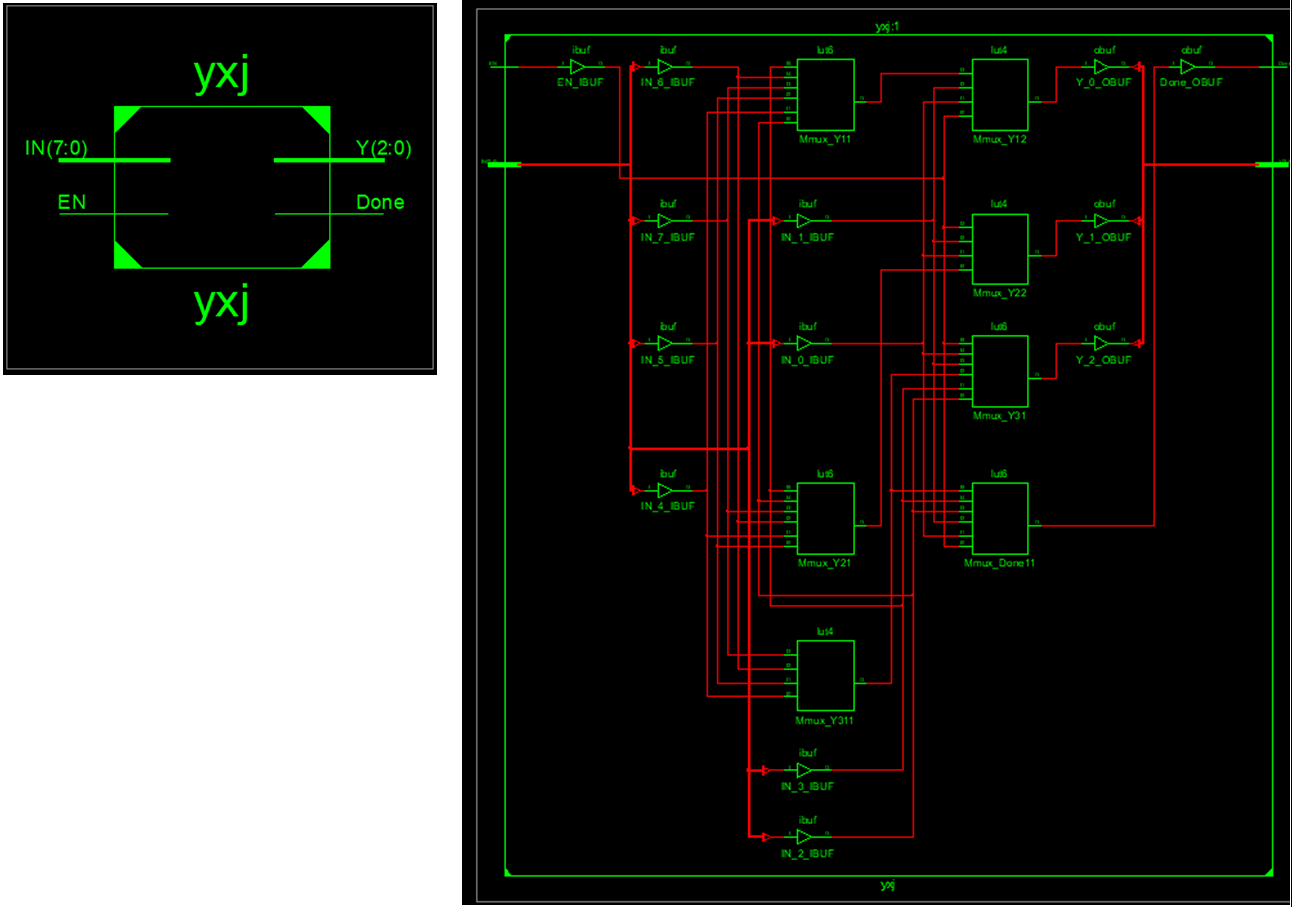

电路管脚图

引脚配置文件

NET "IN[7]" IOSTANDARD = LVCMOS18; NET "IN[7]" LOC = Y6;

NET "IN[6]" IOSTANDARD = LVCMOS18; NET "IN[6]" LOC = Y4;

NET "IN[5]" IOSTANDARD = LVCMOS18; NET "IN[5]" LOC = W4;

NET "IN[4]" IOSTANDARD = LVCMOS18; NET "IN[4]" LOC = V4;

NET "IN[3]" IOSTANDARD = LVCMOS18; NET "IN[3]" LOC = V3;

NET "IN[2]" IOSTANDARD = LVCMOS18; NET "IN[2]" LOC = T4;

NET "IN[1]" IOSTANDARD = LVCMOS18; NET "IN[1]" LOC = U3;

NET "IN[0]" IOSTANDARD = LVCMOS18; NET "IN[0]" LOC = T3;

NET "Y[2]" IOSTANDARD = LVCMOS18; NET "Y[2]" LOC = R1;

NET "Y[1]" IOSTANDARD = LVCMOS18; NET "Y[1]" LOC = P2;

NET "Y[0]" IOSTANDARD = LVCMOS18; NET "Y[0]" LOC = P1;

NET "Done" IOSTANDARD = LVCMOS18; NET "Done" LOC = M1;

NET "EN" IOSTANDARD = LVCMOS18; NET "EN" LOC = R4;

NET "EN" PULLDOWN;NET "IN[7]" PULLDOWN;NET "IN[6]" PULLDOWN;

NET "IN[5]" PULLDOWN;NET "IN[4]" PULLDOWN;NET "IN[3]" PULLDOWN;

NET "IN[2]" PULLDOWN;NET "IN[1]" PULLDOWN;NET "IN[0]" PULLDOWN;

工程文件

工程文件: 二进制优先级编码器设计实验.

最后

以上就是内向西装最近收集整理的关于杭电数字电路课程设计-实验四-二进制优先级编码器设计实验的全部内容,更多相关杭电数字电路课程设计-实验四-二进制优先级编码器设计实验内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复