任务与函数区别

| 比较点 | 任务 | 函数 |

|---|---|---|

| 输入、输出 | 可以有任意多个,各种类型的参数 | 至少有一个输入(不能有输出端口,包括inout端口) |

| 调用 | 任务只能在过程语句中调用,不能在连续赋值语句assign中调用 | 函数可以作为赋值操作的表达式,用于过程赋值和连续赋值语句 |

| 触发事件控制 | 任务不能出现always语句;可以包含延迟控制语句(#),但只能用于仿真,不克用于综合 | 函数不能出现always、# 语句,要保证函数的执行在零时间内完成 |

| 调用其他函数和任务 | 任务可以调用其他任务和函数 | 函数只能调用函数,但不能调用任务 |

| 返回值 | 无返回值 | 调用表达式返回一个值 |

| 其他说明 | 可以作为一条完整的语句 | 只能作为赋值操作的表达式,不能作为一个独立的语句 |

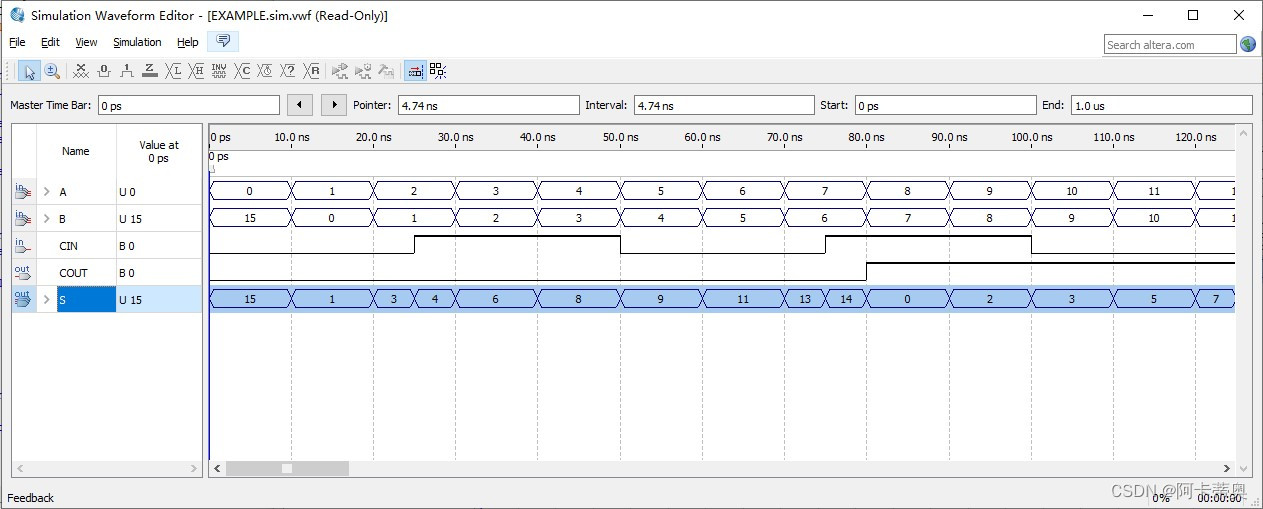

任务 TASK

/*

任务调用 -- 4比特全加器实现

*/

module EXAMPLE(

A,B,CIN,S,COUT

);

input[3:0] A,B;

input CIN;

output[3:0] S;

output COUT;

reg[3:0]S;

reg COUT;

reg[1:0]S0,S1,S2,S3;

task ADD;

input A,B,CIN;

output[1:0] C;

reg[1:0] C;

reg S,COUT;

begin

S = A^B^CIN;

COUT = (A&B)|(A&CIN)|(B&CIN);

C = {COUT,S};

end

endtask

always@(A or B or CIN)begin

ADD(A[0],B[0],CIN,S0);

ADD(A[1],B[1],S0[1],S1);

ADD(A[2],B[2],S1[1],S2);

ADD(A[3],B[3],S2[1],S3);

S={S3[0],S2[0],S1[0],S0[0]};

COUT = S3[1];

end

endmodule

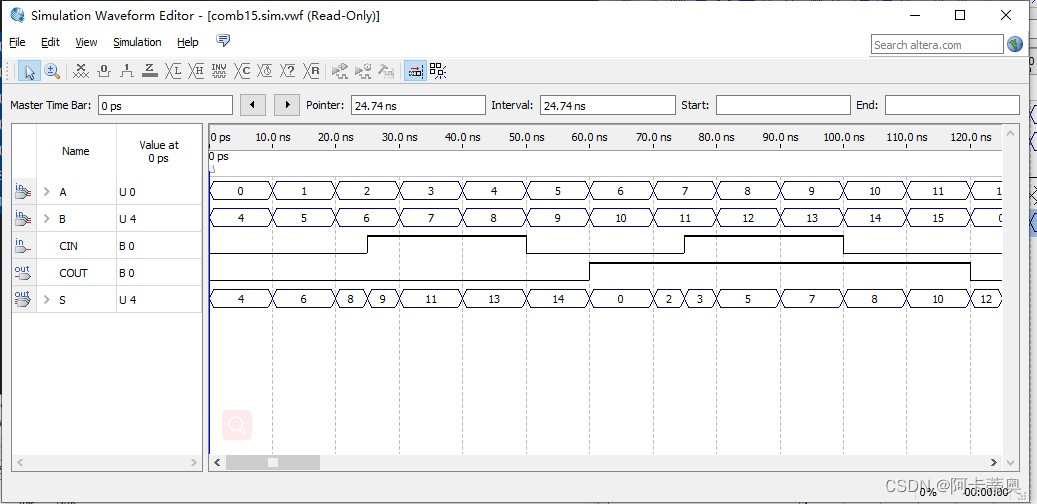

函数 FUNCTION

- 函数定义只能做模块中,不能在过程块中;

- 函数至少有一个端口(不能出现输出端口和双向端口)

- 函数内可以调用函数不能调用任务;

- 函数定义结构体中不能出现过程控制语句(always语句)

- 函数结构中不能使用任何形势的时间控制语句(# wait等),不能使用disable中止语句;

- 函数调用可以在过程块中完成,也可以在assign的连续语句中完成;

- 函数调用不能作为单独语句出现,只能作为赋值语句的右端操作数;

/*

函数调用 -- 4比特全加器实现

*/

module comb15(

A,B,CIN,S,COUT

);

input[3:0] A,B;

input CIN;

output[3:0] S;

output COUT;

wire[1:0]S0,S1,S2,S3;

function signed[1:0]ADD;

input A,B,CIN;

reg S,COUT;

begin

S = A^B^CIN;

COUT = (A&B)|(A&CIN)|(B&CIN);

ADD = {COUT,S};

end

endfunction

assign

S0 = ADD(A[0],B[0],CIN),

S1 = ADD(A[1],B[1],S0[1]),

S2 = ADD(A[2],B[2],S1[1]),

S3 = ADD(A[3],B[3],S2[1]),

S={S3[0],S2[0],S1[0],S0[0]},

COUT = S3[1];

endmodule

最后

以上就是认真板凳最近收集整理的关于Verilog HDL——任务与函数的全部内容,更多相关Verilog内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复