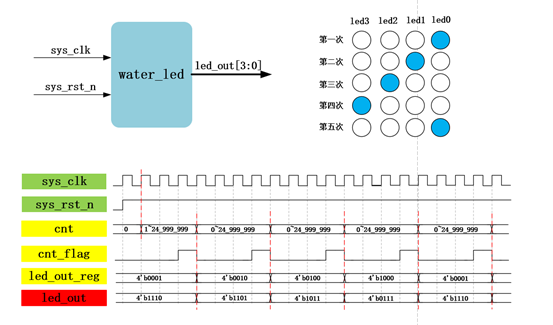

一、波形图

要实现流水灯,首先需要一个计数器,我们实现的是0.5s亮,然后0.5s灭的流水灯,所以根据50mhz的晶振可以计算出,0.5s最大计数值为24999999,所以cnt的值为0~24999999,是一个25位宽的数值。设置一个标志信号来控制输出led,我们采取的是左移实现循环,但是左移会出现全为低电平的情况,因此设置一个led_out_reg对其进行左移然后取反,即可得到我们需要的结果。

二、实现

1.程序

module water_led

#(

parameter CNT_MAX = 25’d24_999_999

)

(

input wire sys_clk,

input wire sys_rst_n,

output wire [3:0] led_out

);

reg [24:0] cnt;

reg cnt_flag;

reg [3:0] led_out_reg;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1’b0)

cnt <= 25’d0;

else if (cnt == CNT_MAX)

cnt <= 25’d0;

else

cnt <= cnt + 25’d1;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1’b0)

cnt_flag <= 1’b0;

else if (cnt == (CNT_MAX-25’d1))

cnt_flag <= 1’b1;

else

cnt_flag <= 1’b0;

/*********

下面的两个else if 不能调换,如果调换会先执行前面的

if—else语句中间的程序,为阻塞赋值

******************/

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1’b0)

led_out_reg <= 4’b0001;

else if ((led_out_reg == 4’b1000) && (cnt_flag == 1’b1))

led_out_reg <= 4’b0001;

else if (cnt_flag == 1’b1)

led_out_reg <= led_out_reg << 1;

else

led_out_reg <= led_out_reg;

assign led_out = ~led_out_reg;

endmodule

2.仿真程序

`timescale 1ns/1ns

module tb_water_led ();

reg sys_clk ;

reg sys_rst_n ;

wire [3:0] led_out;

initial

begin

sys_clk = 1’b0;

sys_rst_n <= 1’b0;

#20

sys_rst_n <= 1’b1;

end

always #10 sys_clk = ~sys_clk;

water_led

#(

.CNT_MAX(25’d24)

)

water_led_inst

(

.sys_clk (sys_clk) ,

.sys_rst_n (sys_rst_n) ,

.led_out (led_out)

);

endmodule

最后

以上就是单薄世界最近收集整理的关于11FPGA流水灯的全部内容,更多相关11FPGA流水灯内容请搜索靠谱客的其他文章。

发表评论 取消回复