实验一

首先在我的电脑选择一个盘打开

然后在一个位置创建一个文件夹

然后新建一个记事本文档将文件后缀名改为.v

然后将实验代码输入到记事本文件中并保存

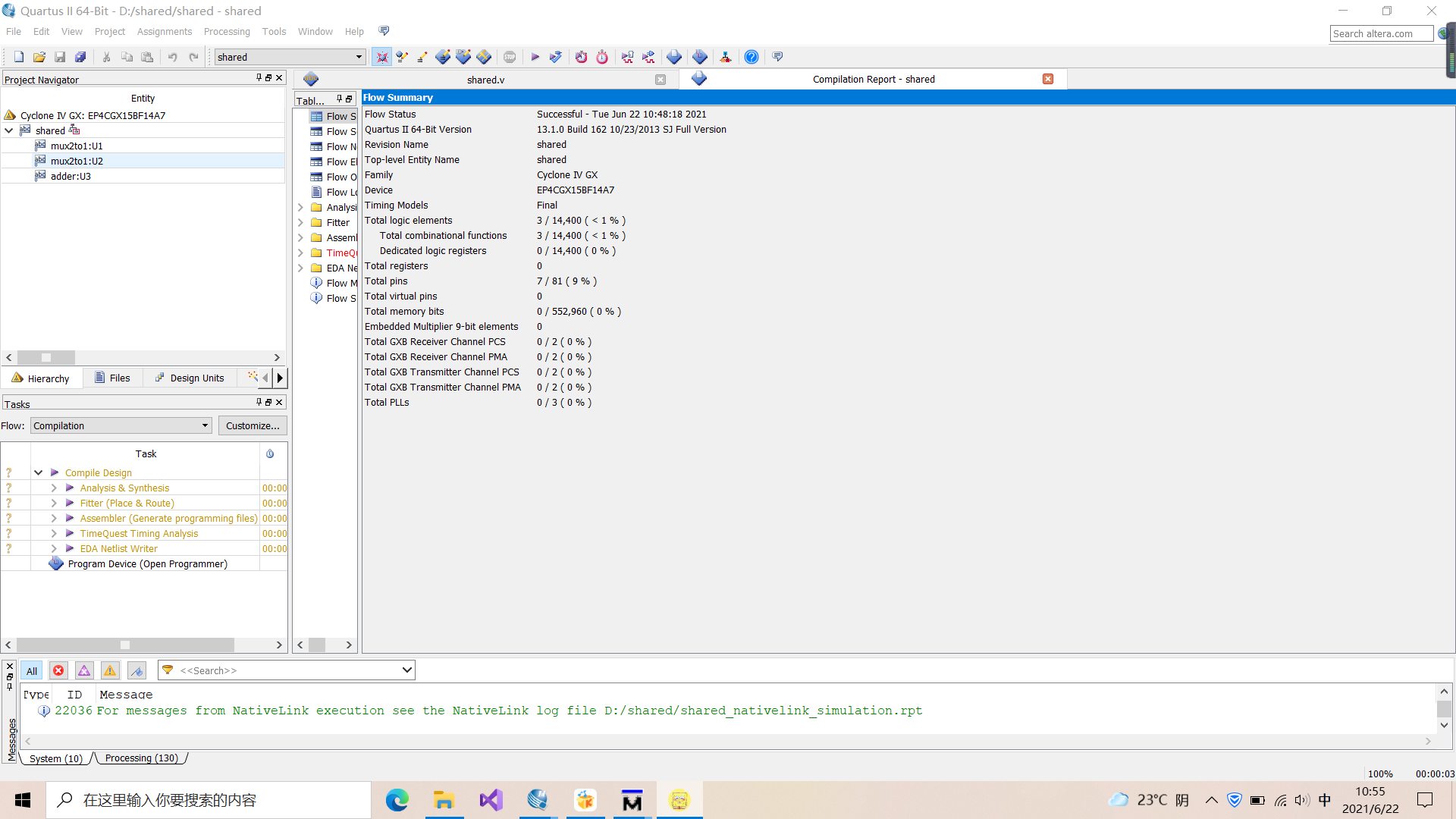

然后打开Quartus II软件新建一个工程

在弹出的选择界面中找到刚刚建立的记事本文档,工程名和记事本文档名字一样

然后在下一个选择框中同样找到那个文件所在位置,调整相应的状态点击完成

然后代码就导入到了工程中在最左侧的方框中右键文件点击setting然后又会弹出一个选择框

然后调成modesilm然后调整一系列数据点击OK然后最左侧方框点击files

点击文件右键点一个东西,然后播放,正常运行后,即可联立modesilm

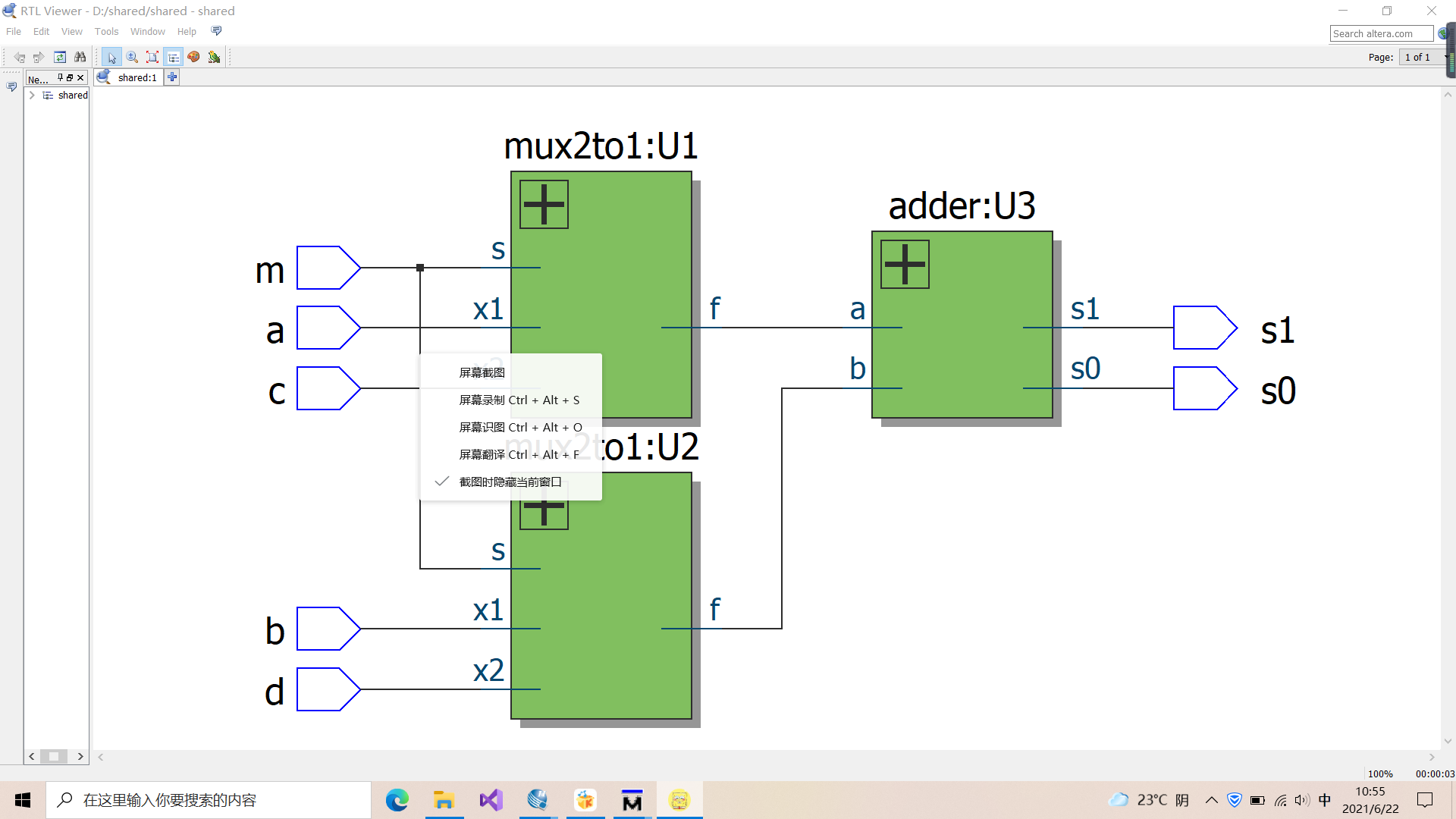

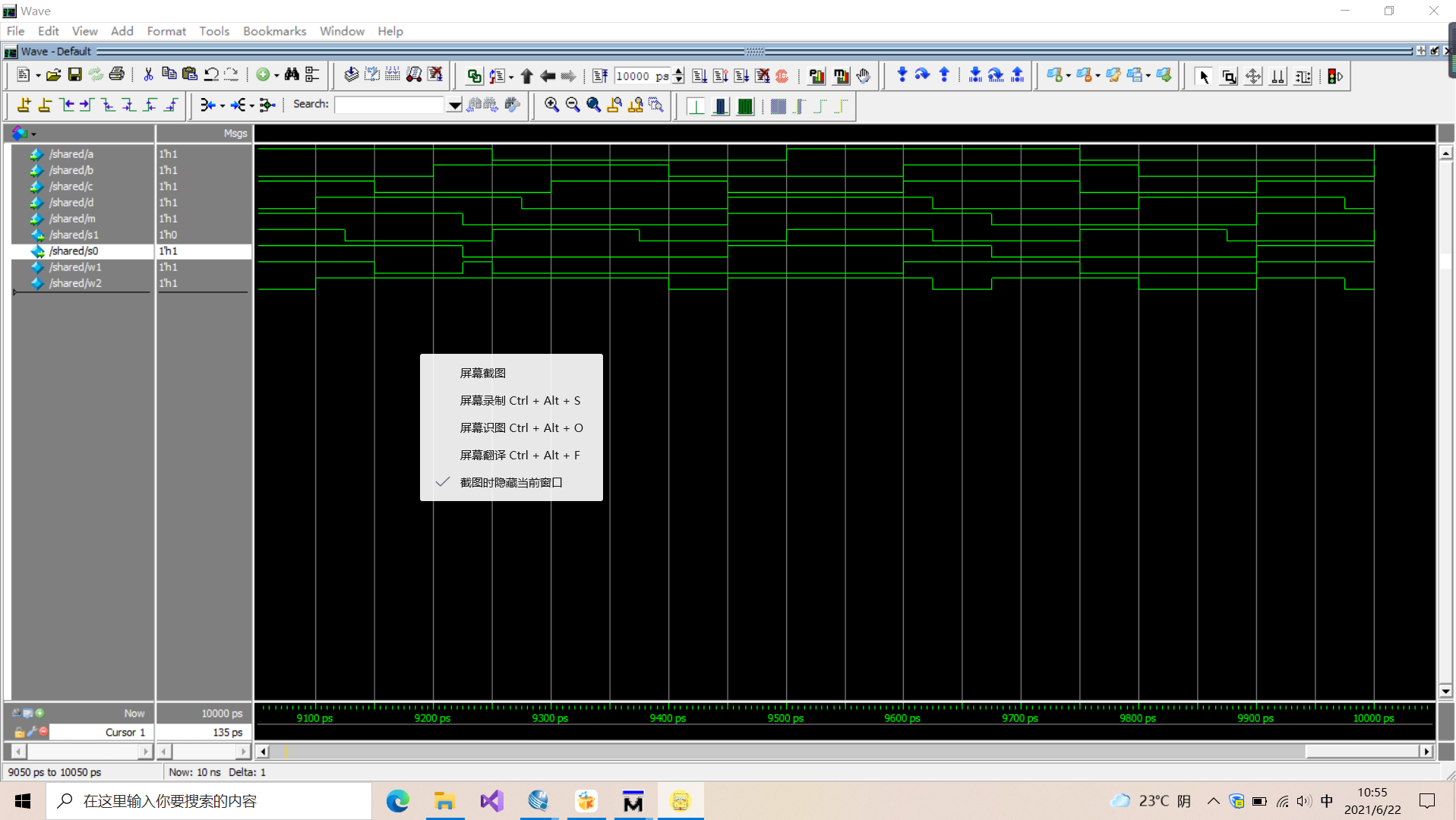

然后更改一些数据就可以得到下图

实验代码

module shared(a,b,c,d,m,s1,s0);

input a,b,c,d,m;

output s1,s0;

wire w1,w2;

mux2to1 U1(a,c,m,w1);

mux2to1 U2(b,d,m,w2);

adder U3(w1,w2,s1,s0);

endmodule

module mux2to1(x1,x2,s,f);

input x1,x2,s;

output f;

assign f=(~s&x1)|(s&x2);

endmodule

module adder(a,b,s1,s0);

input a,b;

output s1,s0;

assign s1=a&b;

assign s0=a^b;

endmodule

实验代码图

实验效果图

实验仿真图

实验视频

http://www.iqiyi.com/v_1e0l4mbkcsk.html

实验二

首先在我的电脑选择一个盘打开

然后在一个位置创建一个文件夹

然后新建一个记事本文档将文件后缀名改为.v

然后将实验代码输入到记事本文件中并保存

然后打开Quartus II软件新建一个工程

在弹出的选择界面中找到刚刚建立的记事本文档,工程名和记事本文档名字一样

然后在下一个选择框中同样找到那个文件所在位置,调整相应的状态点击完成

然后代码就导入到了工程中在最左侧的方框中右键文件点击setting然后又会弹出一个选择框

然后调成modesilm然后调整一系列数据点击OK然后最左侧方框点击files

点击文件右键点一个东西,然后播放,正常运行后,即可联立modesilm

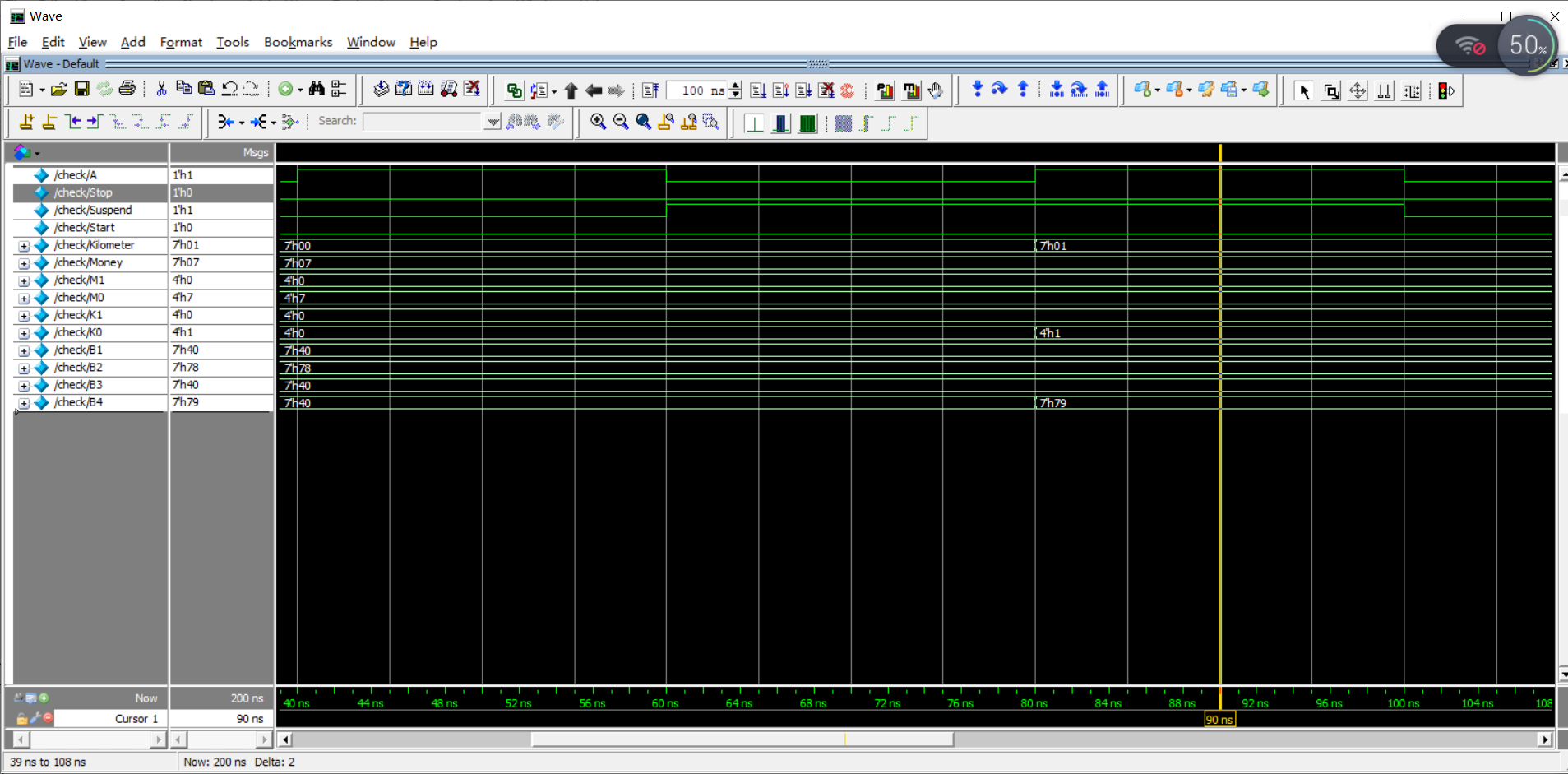

然后更改一些数据就可以得到下图

实验代码

module driver(kilometer,money,a,stop,start,suspend,m1,m0,k1,k0,b1,b2,b3,b4);

input stop,start,suspend;

input a;

output[6:0]kilometer,money;

output[3:0]m1,m0,k1,k0;

output[6:0]b1,b2,b3,b4;

reg[6:0]kilometer,money;

reg[3:0]m1,m0,k1,k0;

reg[6:0]b1,b2,b3,b4;

reg[3:0]money_reg,kilometer_reg;

always@(posedge a)

begin

if(stop)

begin

kilometer<=0;

end

else if(start)

begin

kilometer<=0;

end

else

begin

if(suspend)

kilometer<=kilometer+1;

else

kilometer<=kilometer;

end

end

always@(kilometer)

begin

if(kilometer>9)

begin

money=money+3;

end

else if(kilometer>3)

begin

money=money+2;

end

else money=7;

m1=money/10;

m0=money%10;

k1=kilometer/10;

k0=kilometer%10;

end

always@(m1)

begin

case(m1)

4’b0000:begin b1<=7’b1000000;end

4’b0001:begin b1<=7’b1111001;end

4’b0010:begin b1<=7’b0100100;end

4’b0011:begin b1<=7’b0110000;end

4’b0100:begin b1<=7’b0011001;end

4’b0101:begin b1<=7’b0010010;end

4’b0110:begin b1<=7’b0000010;end

4’b0111:begin b1<=7’b1111000;end

4’b1000:begin b1<=7’b0000000;end

4’b1001:begin b1<=7’b0010000;end

endcase

end

always@(m0)

begin

case(m0)

4’b0000:begin b2<=7’b1000000;end

4’b0001:begin b2<=7’b1111001;end

4’b0010:begin b2<=7’b0100100;end

4’b0011:begin b2<=7’b0110000;end

4’b0100:begin b2<=7’b0011001;end

4’b0101:begin b2<=7’b0010010;end

4’b0110:begin b2<=7’b0000010;end

4’b0111:begin b2<=7’b1111000;end

4’b1000:begin b2<=7’b0000000;end

4’b1001:begin b2<=7’b0010000;end

endcase

end

always@(k1)

begin

case(k1)

4’b0000:begin b3<=7’b1000000;end

4’b0001:begin b3<=7’b1111001;end

4’b0010:begin b3<=7’b0100100;end

4’b0011:begin b3<=7’b0110000;end

4’b0100:begin b3<=7’b0011001;end

4’b0101:begin b3<=7’b0010010;end

4’b0110:begin b3<=7’b0000010;end

4’b0111:begin b3<=7’b1111000;end

4’b1000:begin b3<=7’b0000000;end

4’b1001:begin b3<=7’b0010000;end

endcase

end

always@(k0)

begin

case(k0)

4’b0000:begin b4<=7’b1000000;end

4’b0001:begin b4<=7’b1111001;end

4’b0010:begin b4<=7’b0100100;end

4’b0011:begin b4<=7’b0110000;end

4’b0100:begin b4<=7’b0011001;end

4’b0101:begin b4<=7’b0010010;end

4’b0110:begin b4<=7’b0000010;end

4’b0111:begin b4<=7’b1111000;end

4’b1000:begin b4<=7’b0000000;end

4’b1001:begin b4<=7’b0010000;end

endcase

end

endmodule

实验仿真图

实验视频

http://www.iqiyi.com/v_105wtbcdt6k.html

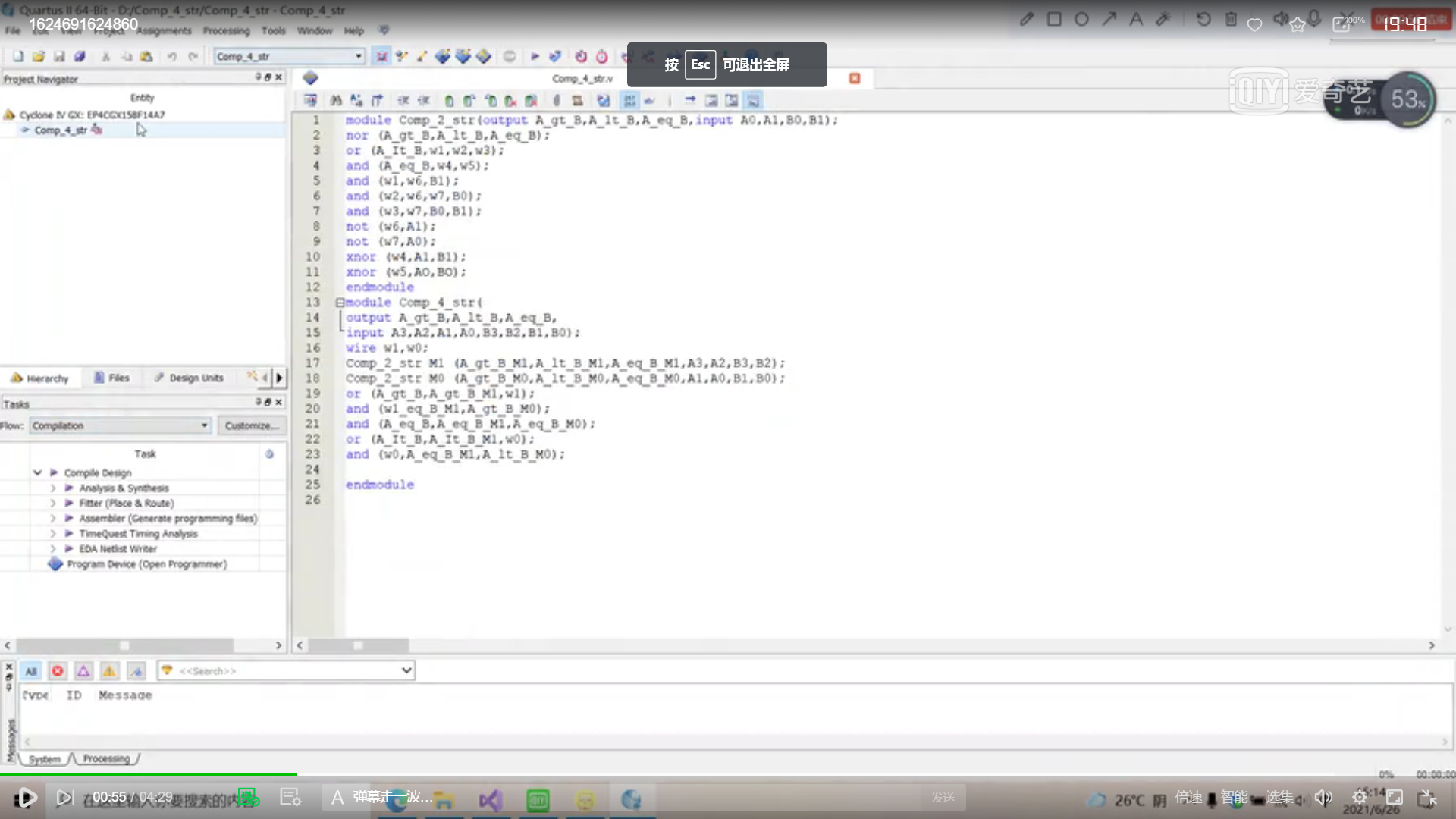

实验三

首先在我的电脑选择一个盘打开

然后在一个位置创建一个文件夹

然后新建一个记事本文档将文件后缀名改为.v

然后将实验代码输入到记事本文件中并保存

然后打开Quartus II软件新建一个工程

在弹出的选择界面中找到刚刚建立的记事本文档,工程名和记事本文档名字一样

然后在下一个选择框中同样找到那个文件所在位置,调整相应的状态点击完成

然后代码就导入到了工程中在最左侧的方框中右键文件点击setting然后又会弹出一个选择框

然后调成modesilm然后调整一系列数据点击OK然后最左侧方框点击files

点击文件右键点一个东西,然后播放,正常运行后,即可联立modesilm

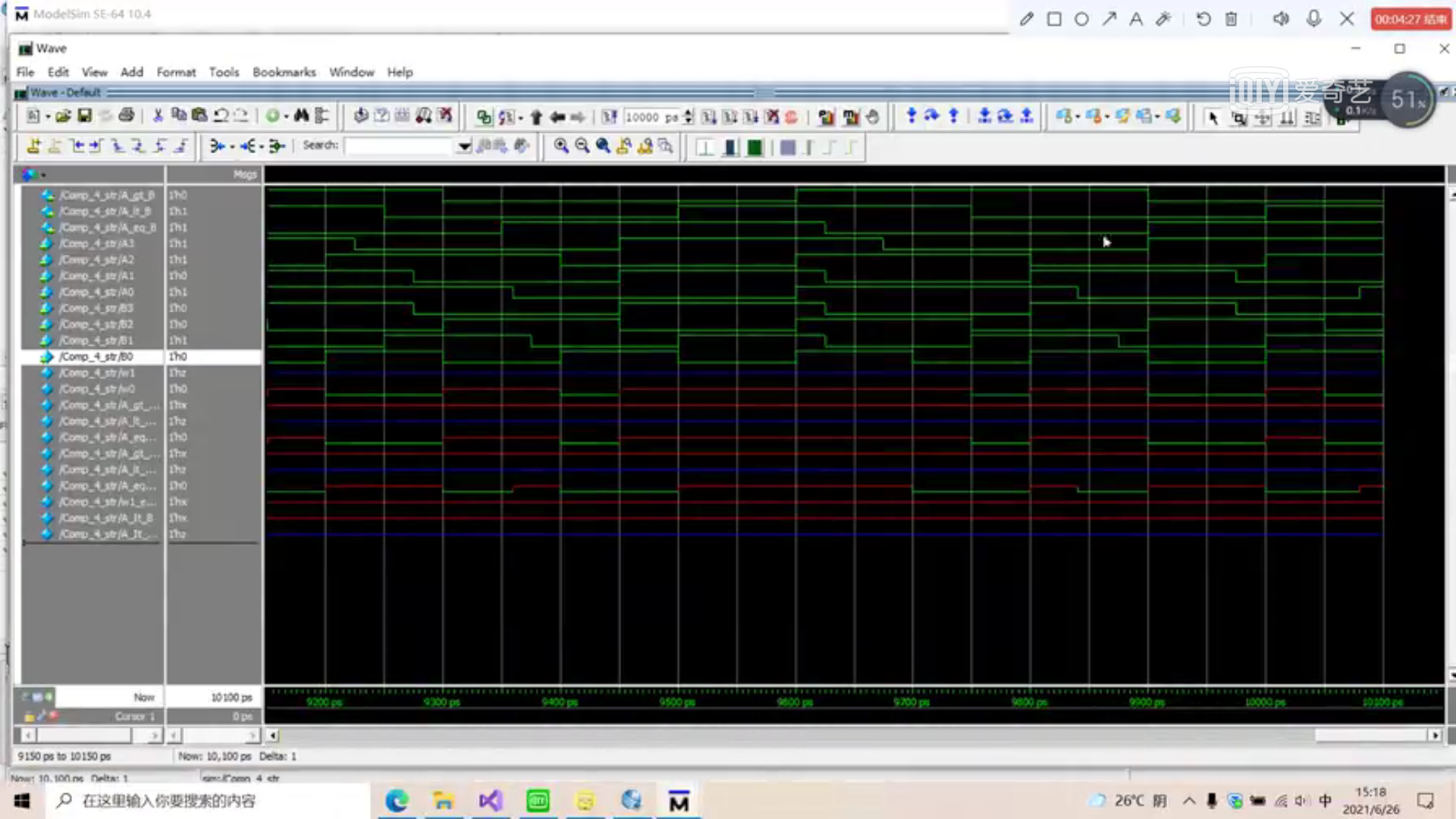

然后更改一些数据就可以得到下图

在这里插入图片描述

实验代码

module Comp_2_str(output A_gt_B,A_lt_B,A_eq_B,input A0,A1,B0,B1);

nor (A_gt_B,A_lt_B,A_eq_B);

or (A_It_B,w1,w2,w3);

and (A_eq_B,w4,w5);

and (w1,w6,B1);

and (w2,w6,w7,B0);

and (w3,w7,B0,B1);

not (w6,A1);

not (w7,A0);

xnor (w4,A1,B1);

xnor (w5,AO,BO);

endmodule

module Comp_4_str(

output A_gt_B,A_lt_B,A_eq_B,

input A3,A2,A1,A0,B3,B2,B1,B0);

wire w1,w0;

Comp_2_str M1 (A_gt_B_M1,A_lt_B_M1,A_eq_B_M1,A3,A2,B3,B2);

Comp_2_str M0 (A_gt_B_M0,A_lt_B_M0,A_eq_B_M0,A1,A0,B1,B0);

or (A_gt_B,A_gt_B_M1,w1);

and (w1_eq_B_M1,A_gt_B_M0);

and (A_eq_B,A_eq_B_M1,A_eq_B_M0);

or (A_It_B,A_It_B_M1,w0);

and (w0,A_eq_B_M1,A_lt_B_M0);

endmodule

实验视频

http://www.iqiyi.com/v_1c99xfakzek.html

最后

以上就是粗暴路人最近收集整理的关于数字电路期末实验报告的全部内容,更多相关数字电路期末实验报告内容请搜索靠谱客的其他文章。

发表评论 取消回复