Verilog 序列信号发生器的三种设计思路

序列信号发生器:同步脉冲作用下循环地产生一串周期性的二进制信号的逻辑器件。

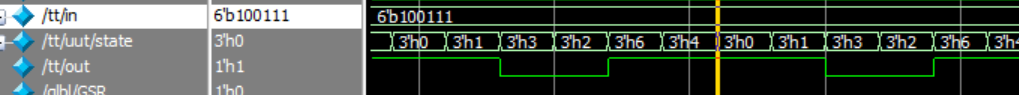

例如产生:100111

方法1:状态机

选择格雷码,每个状态输出一位

module head(

input clk,

input rst_n,

input load,//数据锁存

input [5:0] in,//输入序列

output reg out

);

reg [2:0] state;

reg [5:0] in_reg;

parameter s0=000,s1='b001,s2='b011,s3='b010,s4='b110,s5='b100;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

state<=s0;

out<=0;

end

else

if(load)

begin

in_reg<=in;

state<=s0;

end

else

case(state)

s0:begin

state<=s1;

out<=in_reg[5];

end

s1:begin

state<=s2;

out<=in_reg[4];

end

s2:begin

state<=s3;

out<=in_reg[3];

end

s3:begin

state<=s4;

out<=in_reg[2];

end

s4:begin

state<=s5;

out<=in_reg[1];

end

s5:begin

state<=s0;

out<=in_reg[0];

end

endcase

end

endmodule

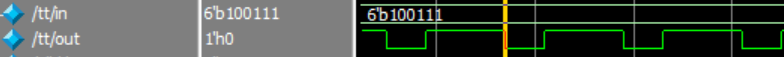

方法2:移位寄存器实现

左移输出

module head(

input clk,

input rst_n,

input load,//数据锁存

input [5:0] in,//输入序列

output out

);

reg [5:0] in_reg;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

in_reg<=0;

else

if(load)

in_reg<=in;

else

in_reg<={in_reg[4:0],in_reg[5]};

end

assign out =rst_n?in_reg[5]:0;

endmodule

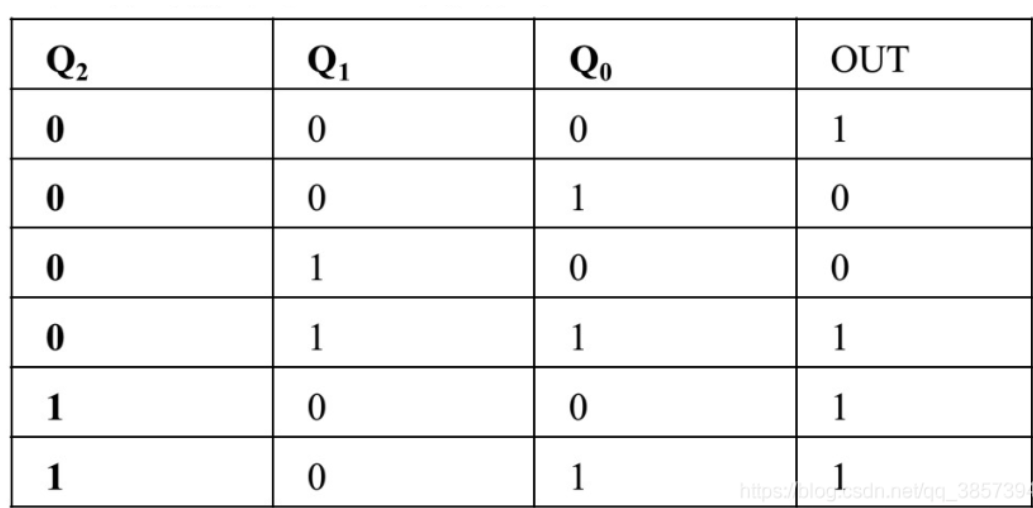

如果问:欲用移位寄存器产生序列信号100111,则至少需要多少级触发器

6位至少需要3级触发器

3个触发器:100->001->011->111->111 重复,不可以。

4个触发器:1001->0011->0111->1111->1110->1100->1001,可以

所以利用移位寄存器至少需要4级触发器

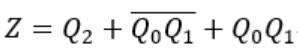

方法三:计数器

module head(

input clk,

input rst_n,

output out

);

reg [5:0] in_reg;

reg [2:0] cnt;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt<=0;

else

cnt<=cnt+1;

end

assign out =cnt[2]|((cnt[1])&(~cnt[0]))|(cnt[1]&cnt[0]);

endmodule

最后

以上就是结实画笔最近收集整理的关于序列信号发生器的全部内容,更多相关序列信号发生器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复