对于序列信号001010, 选择四位: 0010->0101->1010->0100->1000->0001->0010->...... 无重复状态, 则选择该种设计方案(若选择三位会产生重复状态).

由此, 得到状态顺序表.

| 状态顺序表 | ||||

| CLK顺序 | Q3 | Q2 | Q1 | Q0 |

| 0 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 2 | 1 | 0 | 1 | 0 |

| 3 | 0 | 1 | 0 | 0 |

| 4 | 1 | 0 | 0 | 0 |

| 5 | 0 | 0 | 0 | 1 |

| 6 | 0 | 0 | 1 | 0 |

由状态顺序表, 可以看出需要的序列信号由Q3端输出.

根据状态顺序表, 再使电路具备自启动功能, 有下述状态表.

| 状态表 | |||||||

| Q3 | Q2 | Q1 | Q0 | Q3* | Q2* | Q1* | Q0* |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

由于电路本身就是一个同步右移移位寄存器, 所以只需设计D0即可.

| 状态激励表 | ||||

| Q3 | Q2 | Q1 | Q0 | D0 |

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 |

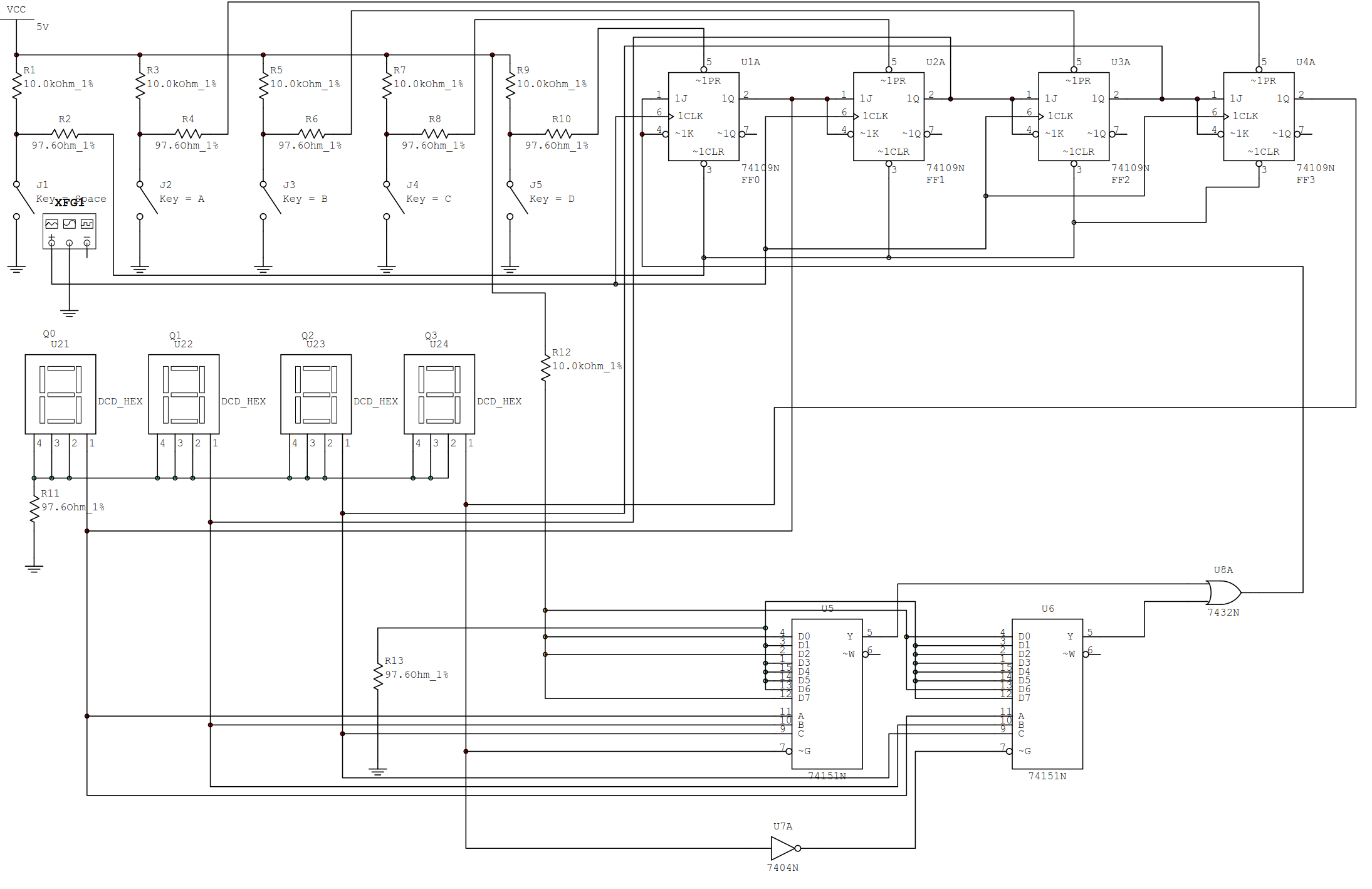

用2片74151和一片非门组成16选1数据选择器, 以此实现D0的逻辑表达式.

根据上面的分析, 绘制电路的原理图.

最后

以上就是英俊世界最近收集整理的关于以同步右移移位寄存器为基础, 设计001010序列信号发生器的全部内容,更多相关以同步右移移位寄存器为基础,内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复