HDLBits网址:https://hdlbits.01xz.net/wiki/Main_Page

1、逻辑移位寄存器

题目

Build a 4-bit shift register (right shift), with asynchronous reset, synchronous load, and enable.

-

areset: Resets shift register to zero.

-

load: Loads shift register with data[3:0] instead of shifting.

-

ena: Shift right (q[3] becomes zero, q[0] is shifted out and disappears).

-

q: The contents of the shift register.

If both the load and ena inputs are asserted (1), the load input has higher priority.

我的设计

移位其实就是做乘法除法,左移为乘法,右移为除法,其他也没有什么好注意的地方了,直接贴代码

module top_module(input clk,input areset, // async active-high reset to zeroinput load,input ena,input [3:0] data,output reg [3:0] q);always@(posedge clk or posedge areset)beginif(areset) q <= 0;else beginif(load) q <= data;elseif(ena) q <= {1'b0,q[3:1]};endendendmodule

2、算术移位寄存器

题目

Build a 64-bit arithmetic shift register, with synchronous load. The shifter can shift both left and right, and by 1 or 8 bit positions, selected by amount.

There is no difference between logical and arithmetic left shifts.

-

load: Loads shift register with data[63:0] instead of shifting.

-

ena: Chooses whether to shift.

-

amount: Chooses which direction and how much to shift.

-

2'b00: shift left by 1 bit.

-

2'b01: shift left by 8 bits.

-

2'b10: shift right by 1 bit.

-

2'b11: shift right by 8 bits.

-

-

q: The contents of the shifter.

我的设计

算术移位和逻辑移位的区别就在于符号问题,逻辑移位无论左移还是右移,都直接补0,因为只是逻辑移位,简单来说就是为了移位而移位,不需要考虑符号的问题;而算术移位,左移是直接补0(与逻辑移位相同),右移的话补符号位。左移补0是因为高位溢出不用理,低位变成高位,所以低位补0;右移补符号位是因为要考虑正负号问题,最高位为符号位,如果符号位为0,正数右移补0,如果符号位为1,负数右移补1。

module top_module(input clk,input load,input ena,input [1:0] amount,input [63:0] data,output reg [63:0] q);always@(posedge clk) beginif(load) q <= data;else if(ena) beginif(amount == 2'b00) q <= {q[62:0],1'b0};else if(amount == 2'b01) q <= {q[55:0],{8{1'b0}}};else if(amount == 2'b10) q <= {q[63],q[63:1]};else if(amount == 2'b11) q <= {{8{q[63]}},q[63:8]};endendendmodule

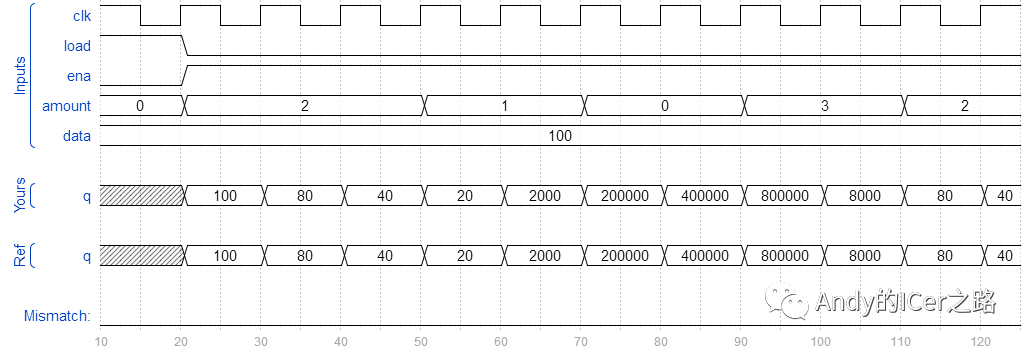

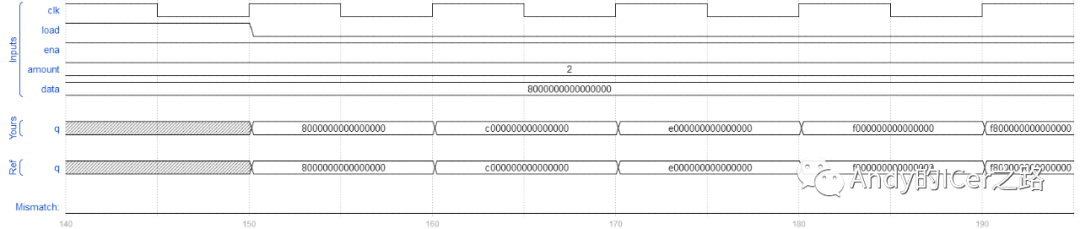

仿真结果

3、循环移位寄存器

题目

Build a 100-bit left/right rotator, with synchronous load and left/right enable. A rotator shifts-in the shifted-out bit from the other end of the register, unlike a shifter that discards the shifted-out bit and shifts in a zero. If enabled, a rotator rotates the bits around and does not modify/discard them.

-

load: Loads shift register with data[99:0] instead of rotating.

-

ena[1:0]: Chooses whether and which direction to rotate.

-

2'b01 rotates right by one bit

-

2'b10 rotates left by one bit

-

2'b00 and 2'b11 do not rotate.

-

-

q: The contents of the rotator.

我的设计

本题的循环移位寄存器有4种模式:加载、循环左移、循环右移、保持现状。(注意:时序逻辑不写完整的if...else...,是不会产生锁存器的)

module top_module(input clk,input load,input [1:0] ena,input [99:0] data,output reg [99:0] q);always @(posedge clk) beginif (load) // Loadq <= data;else if (ena == 2'h1) // Rotate rightq <= {q[0], q[99:1]};else if (ena == 2'h2) // Rotate leftq <= {q[98:0], q[99]};endendmodule

微信公众号

建立了一个微信公众号“Andy的ICer之路”,此公众号主要分享数字IC相关的学习经验,做公众号的目的就是记录自己的学习过程,很多东西回过头来可能就忘记了,为了记住知识和分享知识,希望自己可以保持更新,有兴趣的朋友可以关注一下!

最后

以上就是感动学姐最近收集整理的关于Verilog专题(十六)移位寄存器(逻辑移位、算术移位、循环移位)1、逻辑移位寄存器2、算术移位寄存器3、循环移位寄存器微信公众号的全部内容,更多相关Verilog专题(十六)移位寄存器(逻辑移位、算术移位、循环移位)1、逻辑移位寄存器2、算术移位寄存器3、循环移位寄存器微信公众号内容请搜索靠谱客的其他文章。

发表评论 取消回复