【Verilog学习笔记】D触发器(门级和行为级)+4位寄存器+一个完整的激励程序

首先展示以下完整的程序

`timescale 1ns / 1ps

module hardreg(

input wire clk,

input wire clrb,

input wire [3:0] d,

output wire [3:0] q );

flop_D f1(d[0],clk,clrb,q[0],),

f2(d[1],clk,clrb,q[1],),

f3(d[2],clk,clrb,q[2],),

f4(d[3],clk,clrb,q[3],);

endmodule

/***********************门级表述的D触发器********************************

module flop_D(

input data,

input clock,

input clear,

output q,

output qb);

nand nd1(a,data,clock,clear),

nd2(b,ndata,clock),

nd4(d,c,b,clear),

nd5(e,c,nclock),

nd6(f,d,nclock),

nd8(qb,q,f,clear);

nand nd3(c,a,d),

nd7(q,e,qb);

not iv1(ndata,data),

iv2(nclock,clock);

endmodule

*****************************************************************************/

module flop_D(

input data,

input clock,

inout clear,

output reg q=1'b0 ,

output qb);

always@(posedge clock or posedge clear)

begin

if(clear)

q<=0;

else

q<=data;

end

endmodule

/**************激励模块******************

`timescale 1ns / 1ps

module sim_hardreg( );

reg clock,clearb;

reg[3:0] data;

wire [3:0] qout;

`define stim #100 data=4'b

event end_first_pass;

hardreg reg_4bit (.d(data),.q(qout),.clrb(clearb),.clk(clock));

initial

begin

clock=0;

clearb=1;

end

always #50 clock=~clock;

always@(end_first_pass)

clearb=~clearb;

always@(posedge clock)

$display ("at time %0d clearb=%b data=%d qout=%d",$time,clearb,data,qout);

initial

begin

repeat(4)

begin

data=4'b0000;

`stim 0001;

`stim 0010;

`stim 0011;

`stim 0100;

`stim 0101;

`stim 0110;

`stim 0111;

`stim 1000;

`stim 1001;

`stim 1010;

`stim 1011;

`stim 1100;

`stim 1101;

`stim 1110;

`stim 1111;

#200-> end_first_pass;

end

$finish;

end

endmodule```

关于主程序部分主要需要注意以下几个问题。

1、什么时候input和output可以使用reg型而什么情况下不可以?

当输入输出信号出现在例化中的输出位置时必须用wire型也就是如本程序所示,如果输出错用了reg型会报如下错误:

*[Synth 8-685] variable ‘q’ should not be used in output port connection

2、为什么D触发器中有五个变量而例化的时候只用了四个变量?

要注意如果被引用的模块中有变量有一个在例化中不需要的话,需要用逗号代替,没有逗号是不对的。如果被引用的模块中没有多余的变量时多写了逗号也是不对的。

重点在这个激励模块运用了很多新东西。

1、时钟的一种表示方法

initial

begin

clock=0;

end

always #50 clock=~clock;

用这种方式来产生时钟非常方便也很常用。

2、宏定义

`define stim #100 data=4'b

这句话的含义是指定stim 代替 #100 data=4’b,在以后的程序中一旦看到`stim全部替换成#100 data=4’b。可以使源程序简洁。

3、事件

event end_first_pass;

.....

#200-> end_first_pass;

第一句话用来定义一个事件。而第二句话用来触发这个事件。

触发方式为 # time (触发的时刻)-> (事件名)

4、展示和结束

$display ("at time %0d clearb=%b data=%d qout=%d",$time,clearb,data,qout);

$finish;

第一行用于展示数据,展示数据可以和Modelsim的波形一起反应程序运行的情况。如果用vivado和Modelsim联合仿真的话展示结果可以在Modelsim的Transcript窗口展示。

第二行的finish用来结束程序,在仿真过程中会提示是否要finish如果点击确定的话程序执行完毕会自动关掉,而不展示波形。如果点击取消程序会执行到finish那一步。

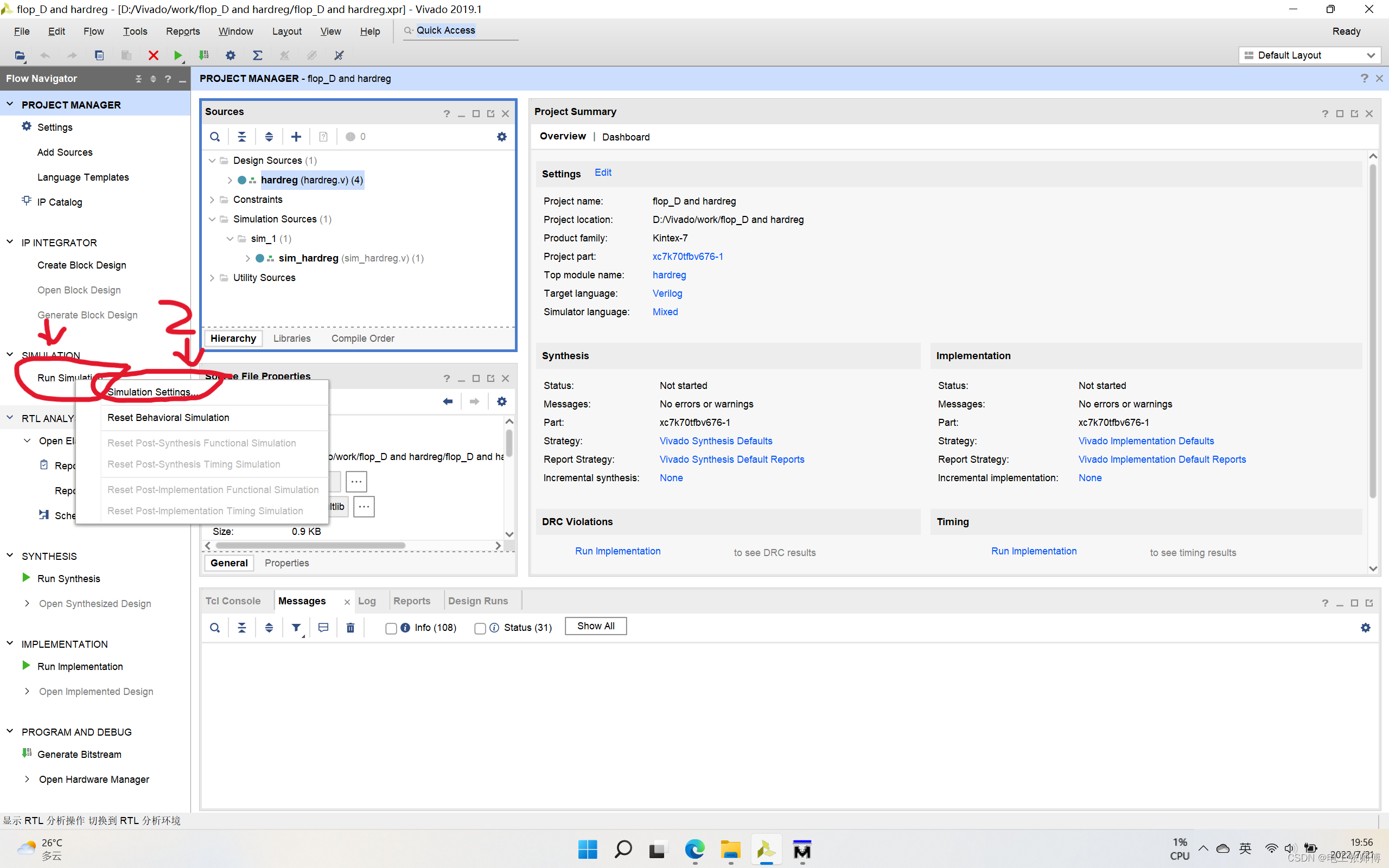

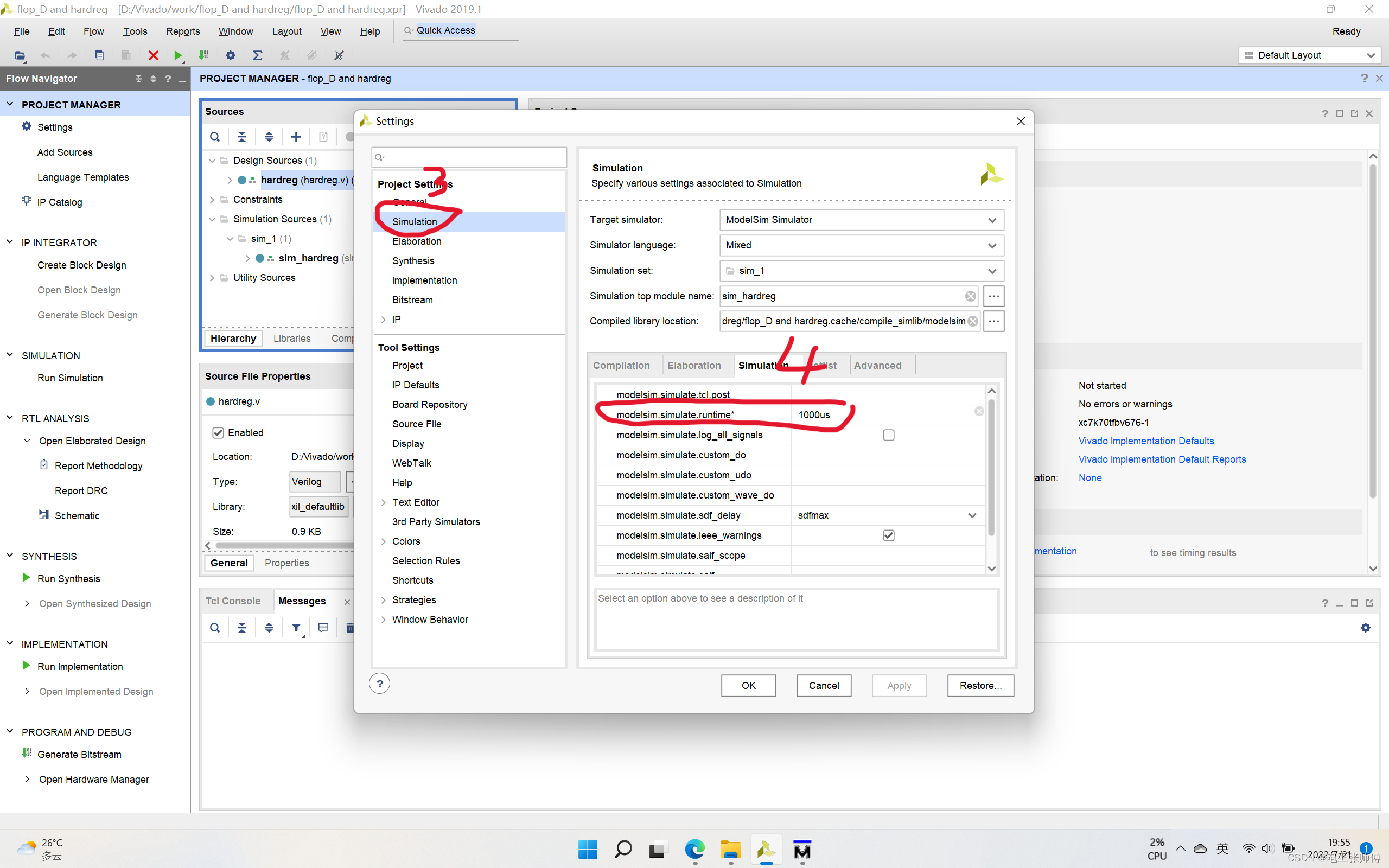

5、如何调整vivado仿真默认的1000ns?

最后

以上就是个性帽子最近收集整理的关于【Verilog学习笔记】D触发器(门级和行为级)+4位寄存器+一个完整的激励程序首先展示以下完整的程序的全部内容,更多相关【Verilog学习笔记】D触发器(门级和行为级)+4位寄存器+一个完整内容请搜索靠谱客的其他文章。

发表评论 取消回复