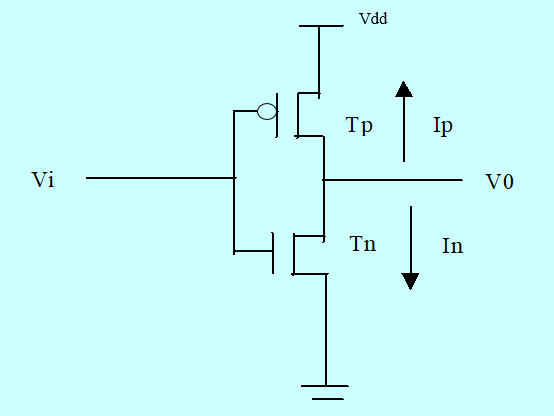

1、cmos构成反相器、或非、与非门

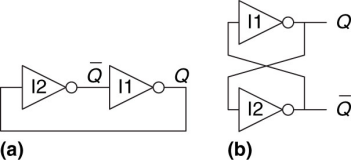

2、双稳态器件 (存储器件->双稳态器件->交叉耦合反相器)

为什么介绍双稳态器件呢?那是因为锁存器、寄存器都是双稳态器件,它们都有两个稳定状态1和0。正是因为它们有两个稳定的状态,因此才可以拿它们来存储数据,也就是说双稳态电路(比如交叉耦合反相器、锁存器和寄存器)可以存储数据。

缺点:只能使电路保持在稳定的状态,不能存储输入信号

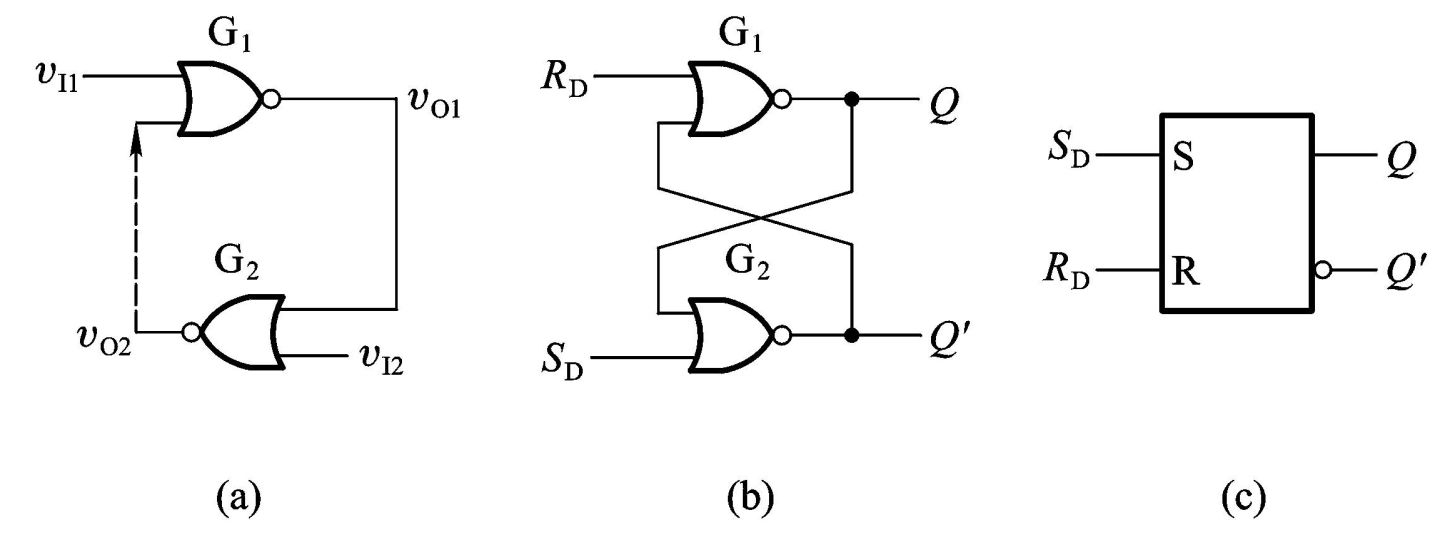

3、锁存器latch

上面的那种交叉耦合反相器没有输入,是存储不了输入的数据的,因此就需要有输入的类似“交叉耦合反相器”结构的双稳态电路,这就是锁存器。

3.1 SR 锁存器:

不需要触发信号,由输入信号直接完成置0或置1操作。

缺点:

- S,R不能同时为1;不够方便;

- 锁存的时间点不清楚,任何时刻,输入都能直接改变输出的状态。也就是不知道什么时候锁存了什么数据,没有一个参考的时刻来确切的知道电路的状态。

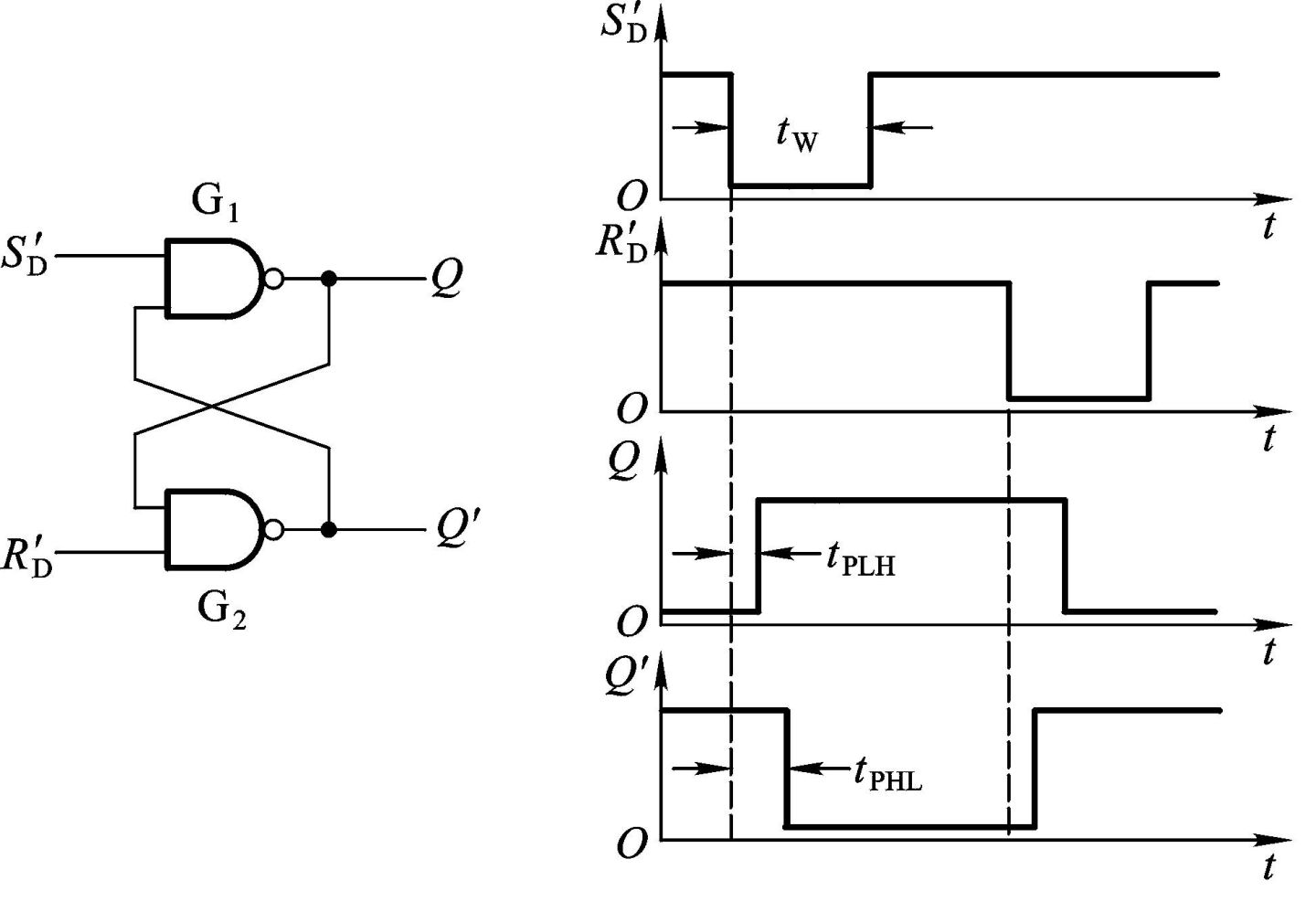

下面我们分析一下SR锁存器的传输延时:

假设SR锁存器的初始状态是Q=0, Q`=1,与非门的传输延时是tpd。输入信号波形如下图所示:

- S的下降沿到达后,经过G1的传输延迟时间tpd,Q端变为高电平;

- Q端高电平加到门G2的输入端,再经过门G2的传输延迟时间tpd, 使Q`变为低电平;

- 当Q`的低电平反馈到G1的输入端以后,即使S=0变成S=1,触发器被置成q=1状态也将保持下去。

可见,为保证触发器可靠地翻转,必须等到Q`=0的状态反馈到G1的输入端以后,S=0的信号才可以取消。

因此,S输入的低电平信号宽度tw应满足tw≥2tpd。

同理,如果从R端输入置0信号,其宽度也必须大于、等于2tpd。

所以:1、对毛刺不敏感 2、同时要求输入信号的宽度。

可见,如果S,R端输入的信号宽度很小,比如毛刺,那么输出是不会改变的。SR锁存器的结构,在门控时钟切换防毛刺中很有用。

3.2 D锁存器

为了解决SR锁存器的缺点,改进的结构就是D锁存器。

D锁存器最大的特点是,引入了一个特殊信号——时钟信号。

注意:时钟信号首先是一个信号,它只是一个特殊的信号,由于它的特殊性和重要性,所以他才有了一个名字叫做时钟信号, 同样的还有复位信号。在分析时钟的时候,请不要忘记,时钟信号首先是一个信号。在这儿可以看成是一个控制锁存器工作与否的使能信号。

引入时钟信号的作用是,作为参考和同步。因为时钟是一个特殊的,高低电平循环的信号,它的行为是确定的, 而且送给不同电路的时钟信号是同一个。所以就能以它作为参考。

比如,引入时钟信号后,D锁存器就只能在时钟有效的时候,S和R才能起作用,也就是给SR加了一个前提条件,这样对照周期性的时钟信号,就能明确知道锁存的时间点了。

1)解决了SR端同时=1

2)对输入信号的宽度没有要求,那是不是可以理解为毛刺敏感?(理解的不对,依然有要求)(不对再不对,原有理解应该是对的)毛刺敏感

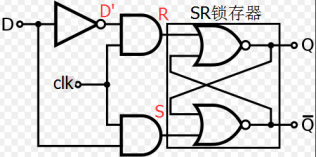

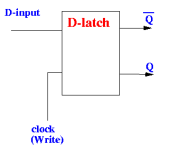

D锁存器常见结构和电路符号图如下所示:

可以看到,D锁存器可以分为前级门电路(两个与门和一个非门)和后级SR锁存器组成。

下面我们就来分析一下它的功能:

输入是Clk和D,也就是输入有四种可能:

·当clk=0时,红S红R都为0,也就是SR锁存器的输入为00,根据SR锁存器的功能,输出Q和Q’将保持原来的状态;因此clk=0时,不管D是什么,输出Q和Q’都不随D变化,只与原来的状态有关,也就是保持。

·当clk=1时,R=(1·D’)=D’;S=(1·D)=D。

也就是说,当clk=1的时候,SR锁存的输入是互补的,不会出现S和R同时有效的情况。当D=1时,S=1,置位有效,输出Q=1;当D=0时,R=1,复位有效,输出Q=0;因此就可以知道,在clk=1时,输出Q=D,也就是输出等于输入。

通过上面的分析,上面的D锁存器结构功能为:在clk=1时,数据通过D锁存器流到了Q;在Clk=0时,Q保持原来的值不变。这样的锁存器也称为透明锁存器或者电平敏感锁存器。

注意:这里说的电平敏感是指时钟电平为1的时候,输入才能引起输出变化。

4、触发器

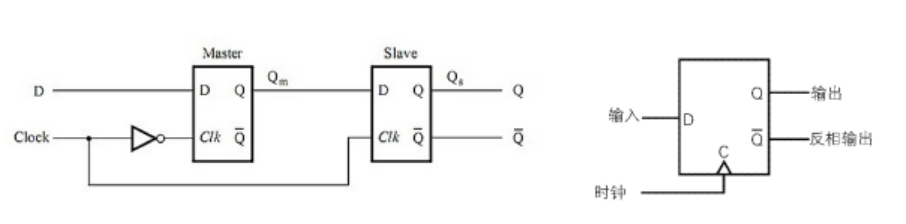

D触发器的结构和电路符号图如下所示:

D触发器可以由两个D锁存器构成,驱动时钟的相位相反,前面的D锁存器称为主锁存器,后面的D锁存器称为从锁存器,因此D触发器也可以称为主从触发器。

下面我们分析一下D触发的功能(注意主锁存器的时钟是clock取反):

假设要传输的数据D=D1:

在时钟clk=0的时候,主锁存打开进行传输数据,把输入传送到从到从锁存器的输入端,即Qm = D1。然后clk从0→1的时候,主锁存器准备关闭,保持原来的值D1,与此同时从锁存器准备打开,把Qm的值传输到输出Qs,也就是Qs=Qm=D1。

在clk=1的时候,主锁存器是关闭的,Qm保持D1不变,即Qm=D1;从锁存器是打开的,Qs=Qm=D1。接着clk从1→0的时候,主锁存器准备打开,准备传输数据;而从锁存器准备关闭。在clk=0的时候,主锁存打开进行传输数据,把输入传送到从到从锁存器的输入端,即Qm *= D2;与此同时,从锁存器关闭,由于新的Qm即Qm*还没有到达从锁存器的D端,因此在从锁存器关闭的时候,从锁存器锁存的是原来的值即D1,因此输出Qs =D1。然后接下来上升沿就传输D2....

从上面的分析可以找到,D触发器在时钟上升沿的时候锁存在时钟上升沿采到的值,并且保持一个时钟周期。这种在时钟上升沿锁存数据的触发器称为正边沿触发器,与此对应的还有负边沿触发的触发器,这里就不进行介绍了。

5、寄存器(Register)

由多个D触发器构成(一个D触发器可以看做1位的寄存器);寄存器可以看成是多位的DFF。

比如带使能的触发器:

总结:

介绍了从cmos、双稳态器件、锁存器、触发器的变化,以及各个器件的优缺点,介绍了他们更迭变化的理由。其中锁存器和触发器还有很多种分类,有空填个坑。

知其然并知其所以然 是实在是有趣。吾生也有涯,而知也无涯。

参考资料:

从CMOS到触发器(二)_简单同学的博客-CSDN博客_cmosd触发器

芯片设计进阶之路——从CMOS到建立时间和保持时间 - 知乎

最后

以上就是怕孤独月饼最近收集整理的关于从MOS管到触发器1、cmos构成反相器、或非、与非门2、双稳态器件 (存储器件->双稳态器件->交叉耦合反相器)3、锁存器latch4、触发器 5、寄存器(Register)的全部内容,更多相关从MOS管到触发器1、cmos构成反相器、或非、与非门2、双稳态器件 内容请搜索靠谱客的其他文章。

发表评论 取消回复