目录

- 源码

- 仿真文件

在电路中, 触发器的输入与输出是有一个延迟的,并不是上升沿一来,输出端马上输出数据,这是由于触发器内部电路决定的。

就算是最简单的非门,输入与输出也有延迟,更别说复杂的电路了。

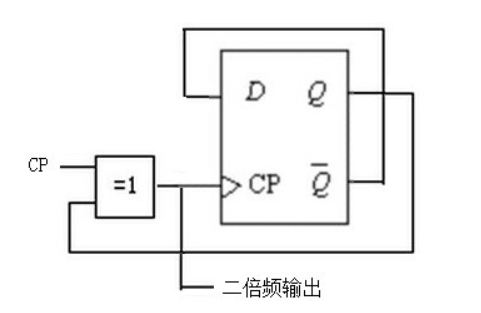

下面是具体的二倍频电路(来源网络)

图中=1是一个异或门

如果我们是理想情况下,没有任何延迟,那我们就不能利用延迟设计二倍频。

而功能(行为)仿真就是基于理想情况,信号在电路中传输没有任何延迟

所以本次设计是在时序仿真下实现的

选择的芯片型号是 Altera(Intel)公司的 cyclone 4 系列EP4CE10F17C8

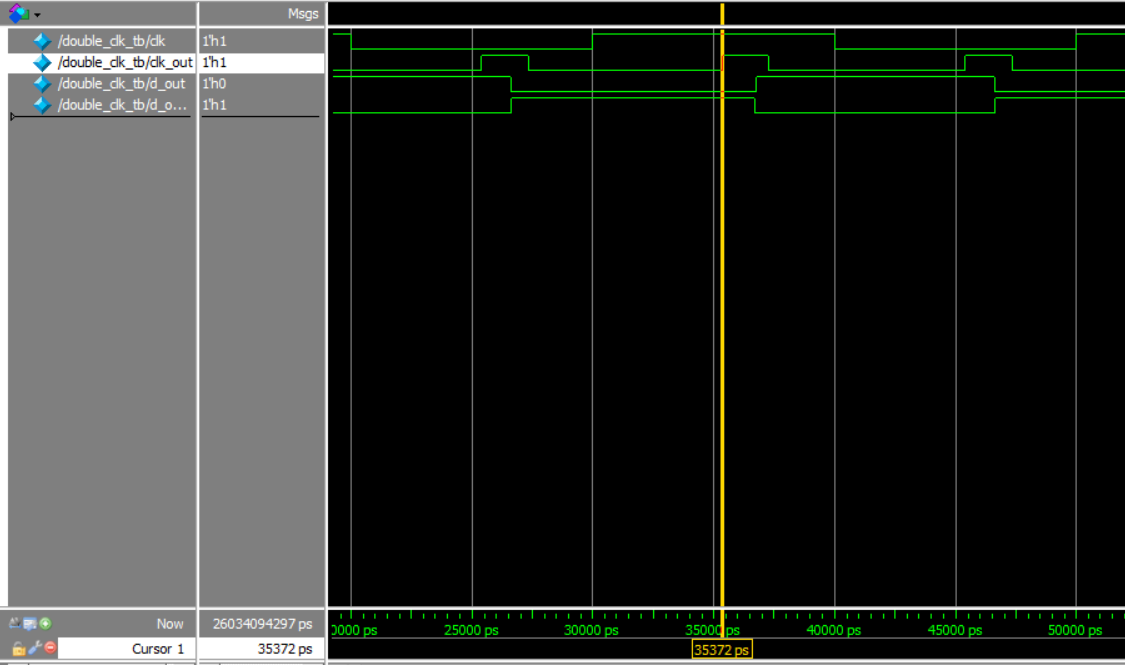

使用modelsim进行时序仿真

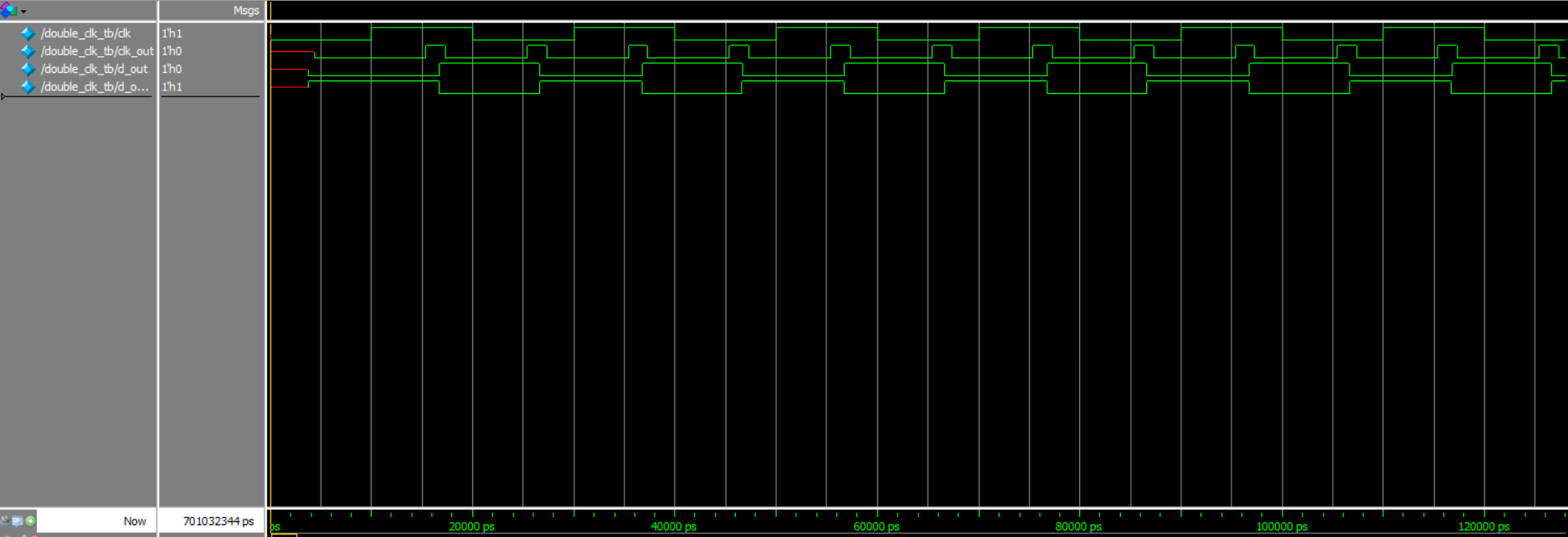

原时钟周期20ns

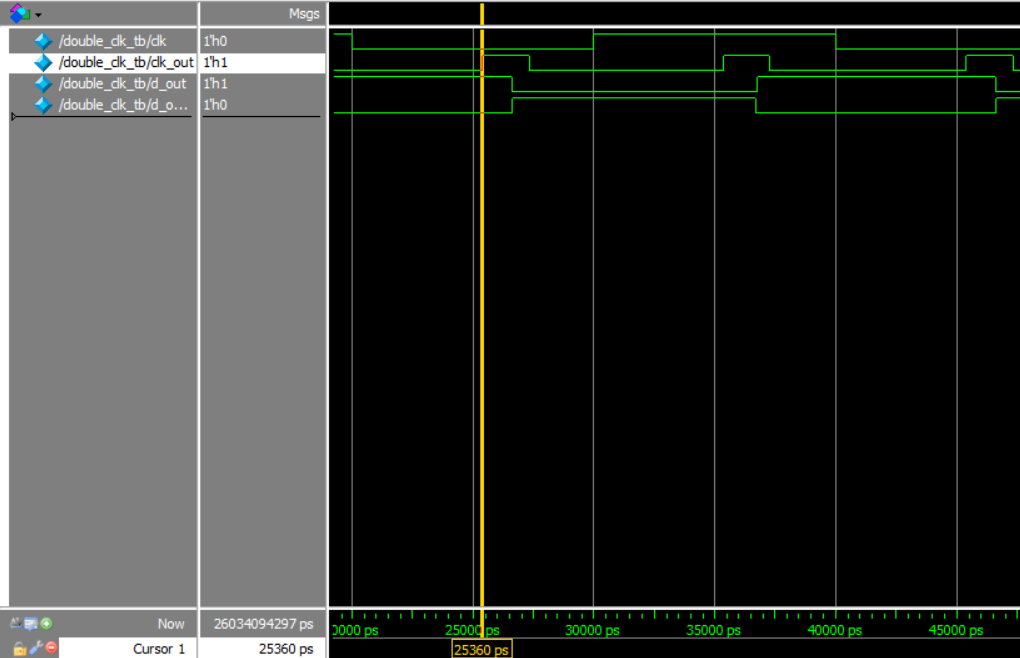

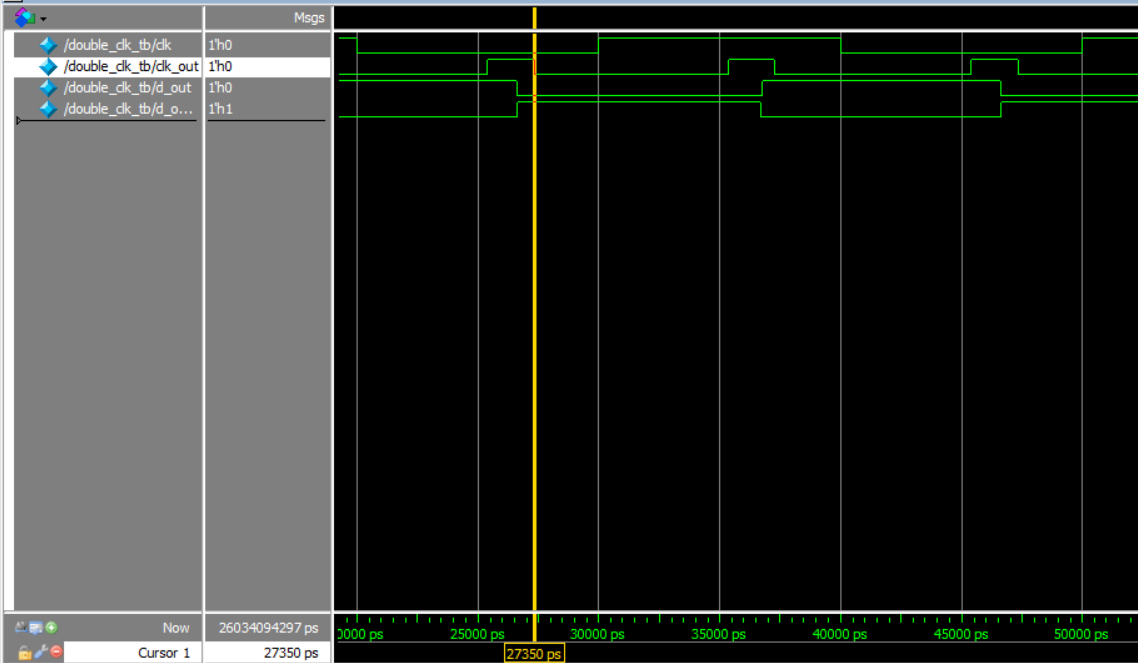

可以看到,输出时钟的高电平持续时间为27350-25360=1990ps;低电平持续时间为35372-27350=8022ps,周期为10012ps,约等于10ns,基本实现二倍频

其实非门也有延迟,时序仿真中大概10ps

每次对程序编译后,执行的时序仿真都不太一样,有些许区别,这是因为每次布局布线都不太一样,导致时序有些区别

源码

参考:https://wenku.baidu.com/view/70330be8172ded630b1cb6fd.html

// 利用D触发器的输入输出延迟来达到倍频效果

module double_clk(

input sys_clk,

output d_out_n,

output reg d_out = 0, //D触发器输出端

output clk_out // 输出倍频时钟

);

assign clk_out = sys_clk ^ d_out;

assign d_out_n = ~d_out; //D触发器取反

always@(posedge clk_out ) begin

d_out <= d_out_n;

end

endmodule

仿真文件

`timescale 1ns / 1ps

`define clk_period 20

module double_clk_tb();

reg clk;

wire clk_out;

wire d_out;

wire d_out_n;

initial clk = 0;

always #(`clk_period/2) clk = ~clk;

double_clk double_clk(

.sys_clk (clk),

.d_out_n (d_out_n),

.d_out (d_out),

.clk_out (clk_out)

);

endmodule

在进行时序仿真之前,一定要用quartus进行全编译,不能只综合,这样才能布局布线,才能进行时序仿真。

用vivado的话,原理一样

最后

以上就是听话航空最近收集整理的关于利用D触发器的输入输出延迟实现二倍频电路的全部内容,更多相关利用D触发器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复