一、D触发器

D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

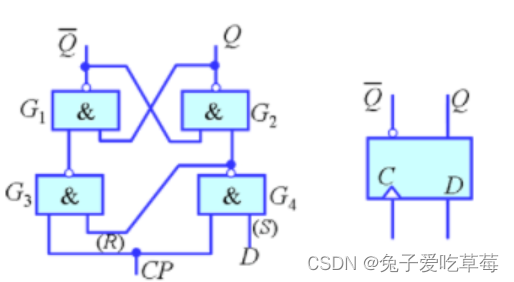

D触发器有集成触发器和门电路组成的触发器。触发方式有电平触发和边沿触发两种,前者在CP(时钟脉冲)=1时即可触发,后者多在CP的前沿(正跳变0→1)触发。

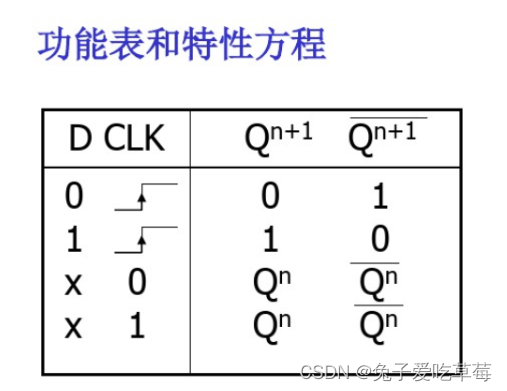

D触发器的次态取决于触发前D端的状态,即次态=D。因此,它具有置0、置1两种功能。

对于边沿D触发器,由于在CP=1期间电路具有维持阻塞作用,所以在CP=1期间,D端的数据状态变化,不会影响触发器的输出状态。

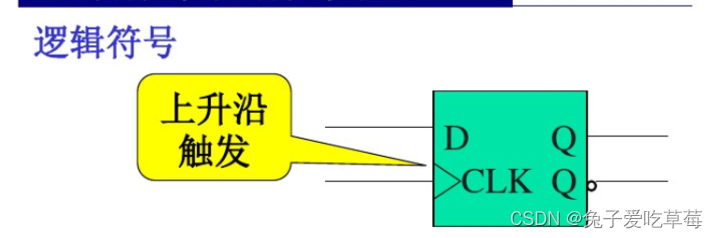

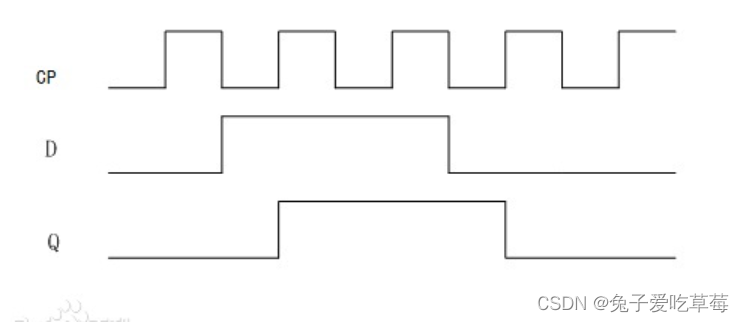

边沿触发的触发器

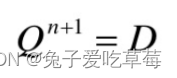

方程

时序图

二、创建D触发器并仿真

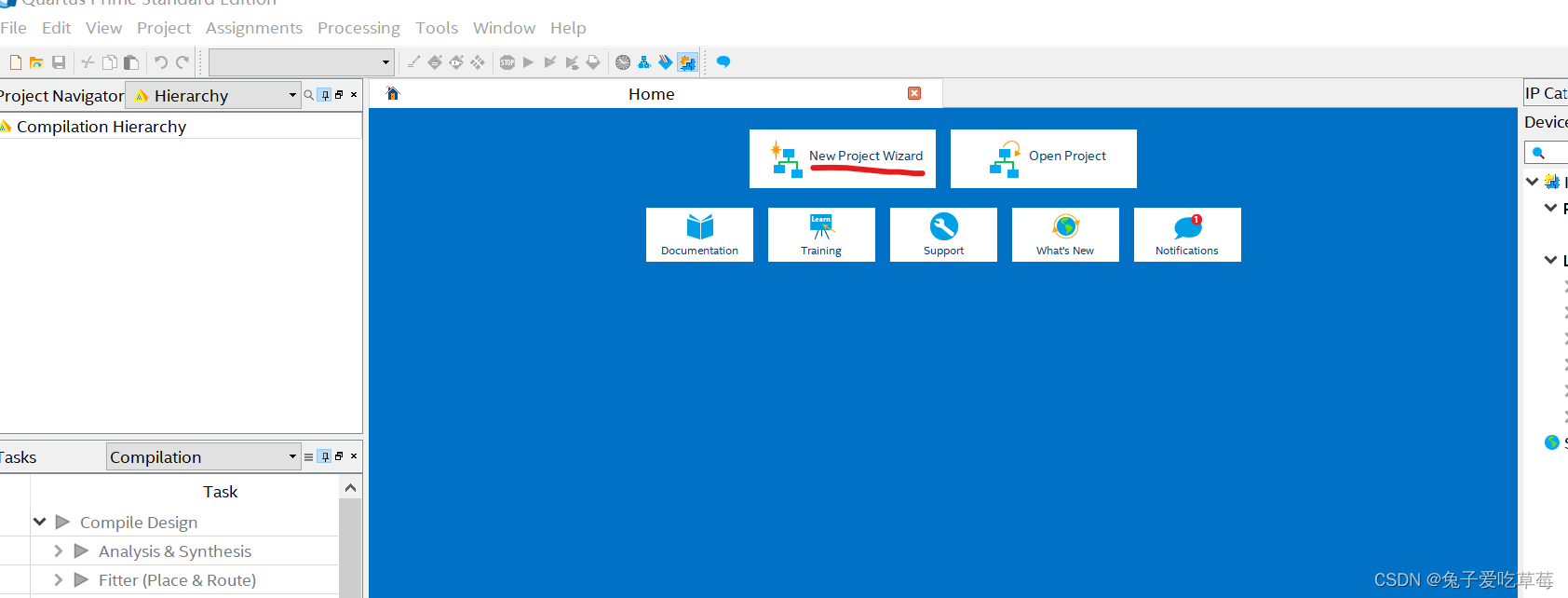

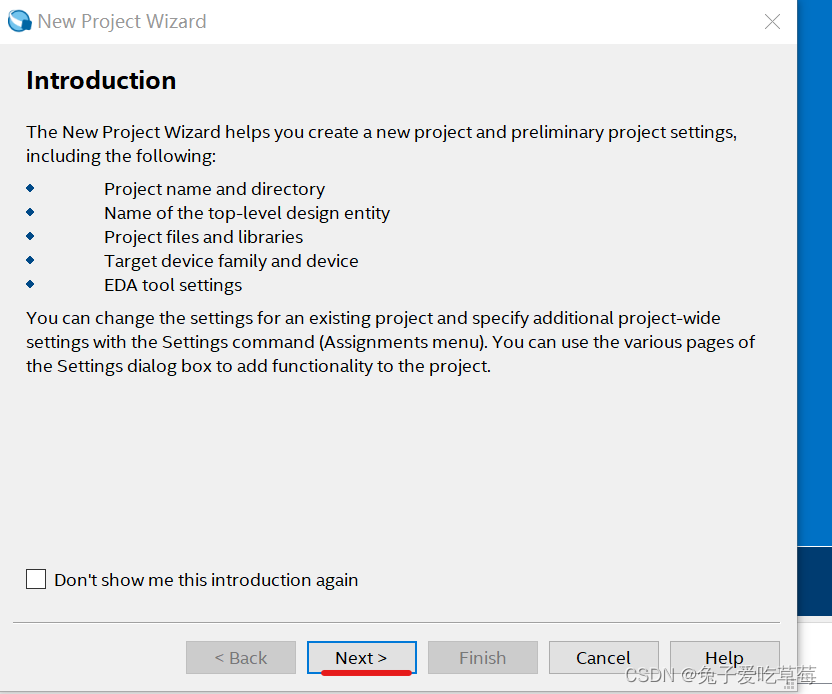

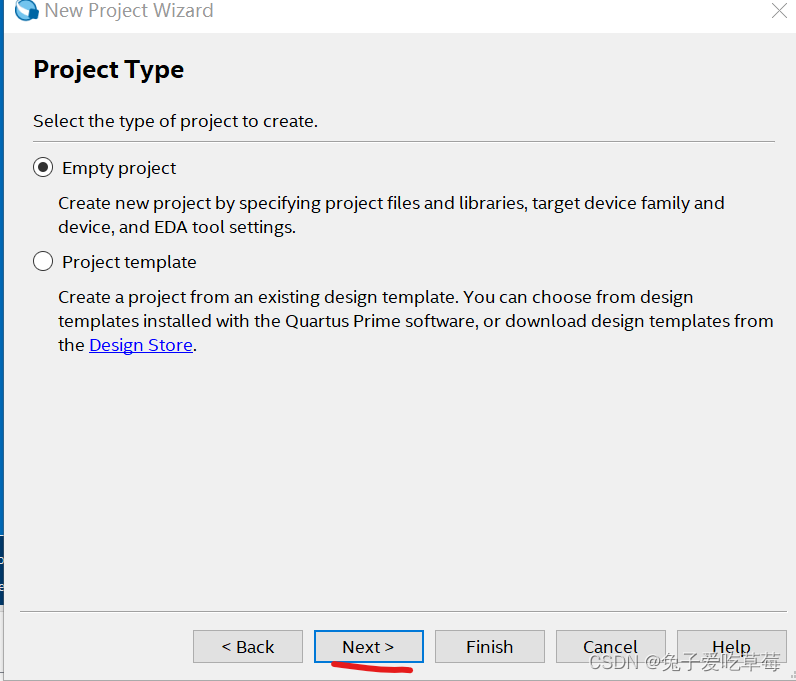

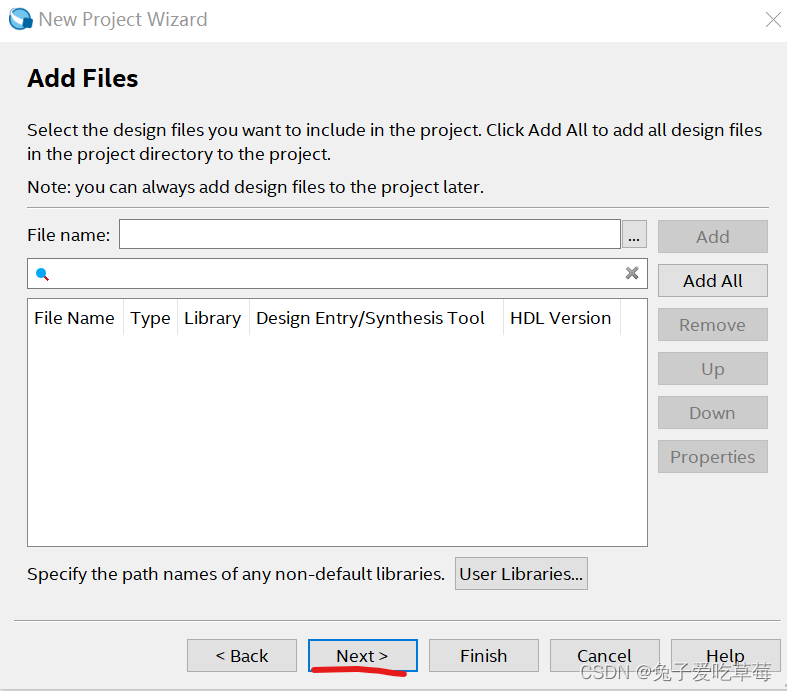

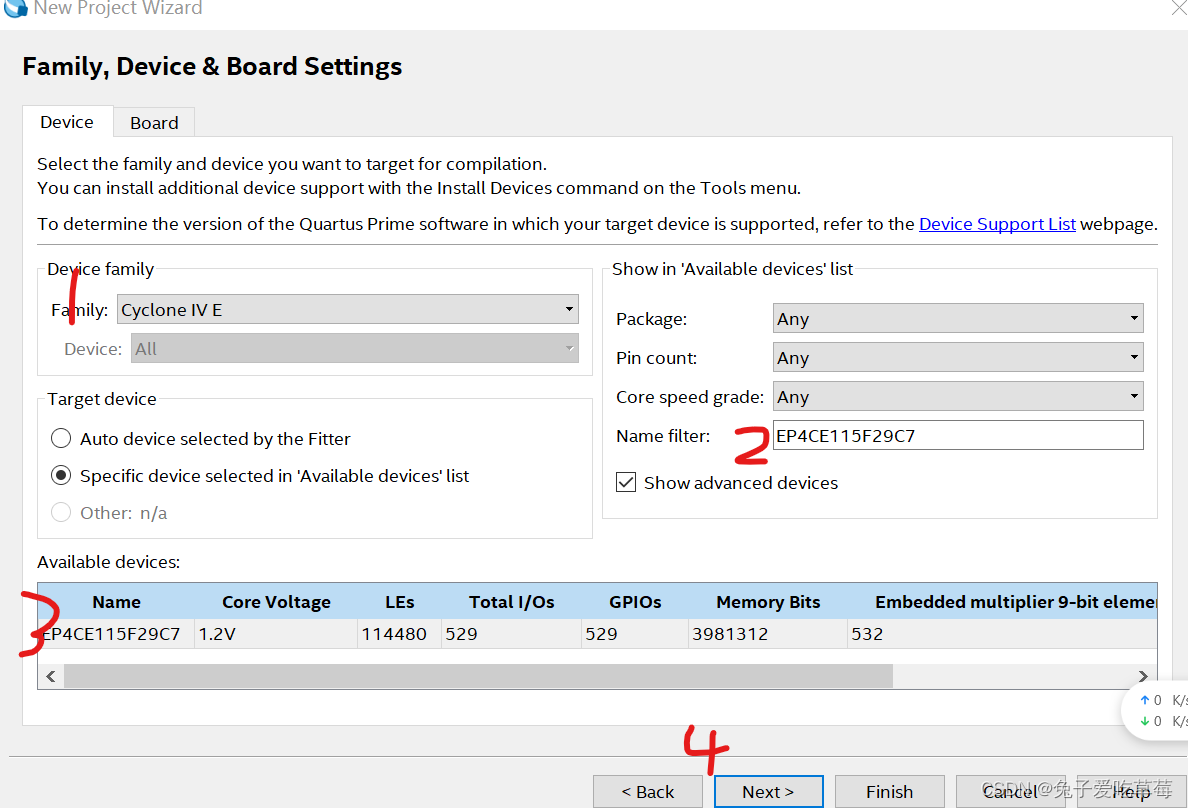

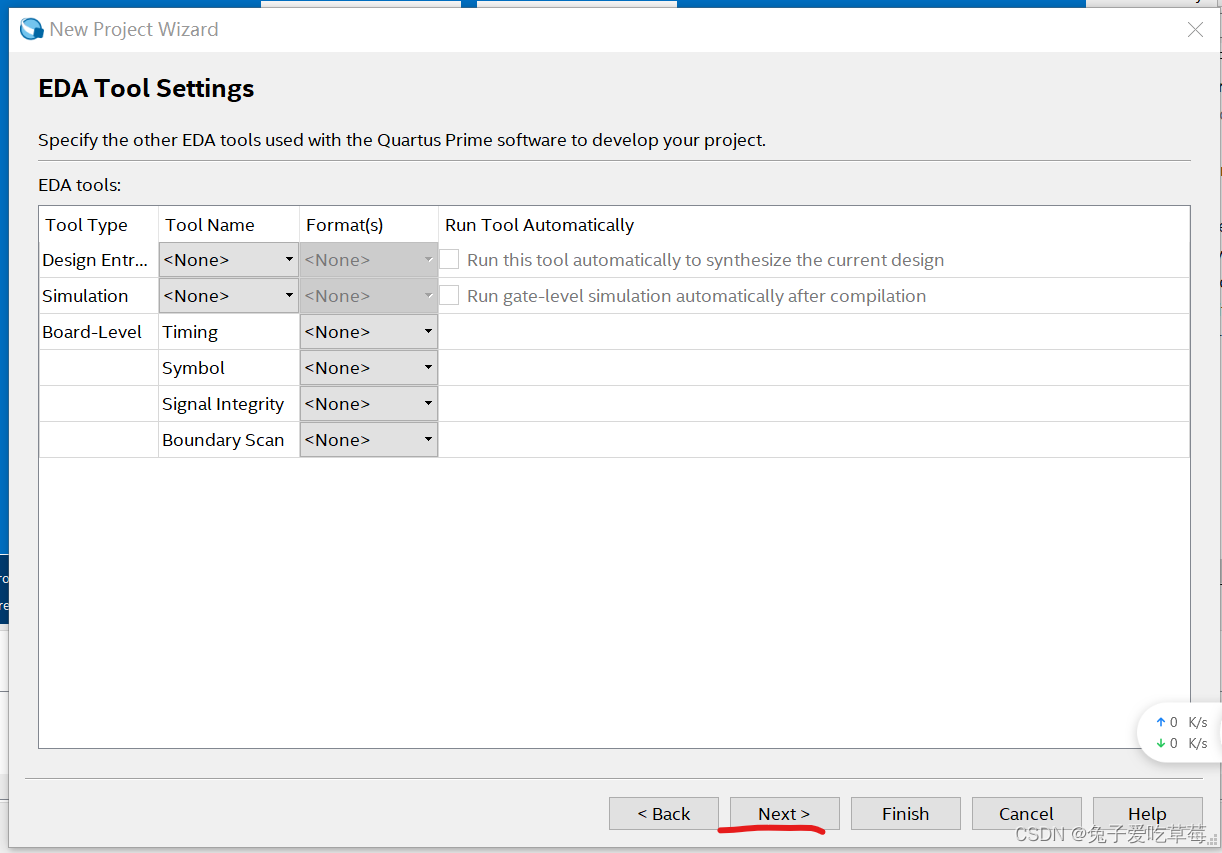

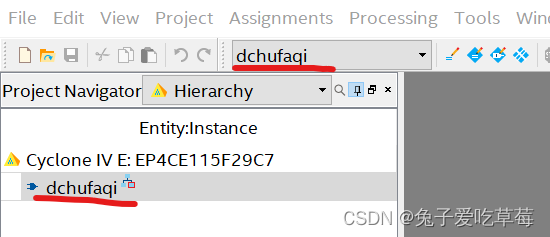

1、创建工程

或者File->New Project Wizard

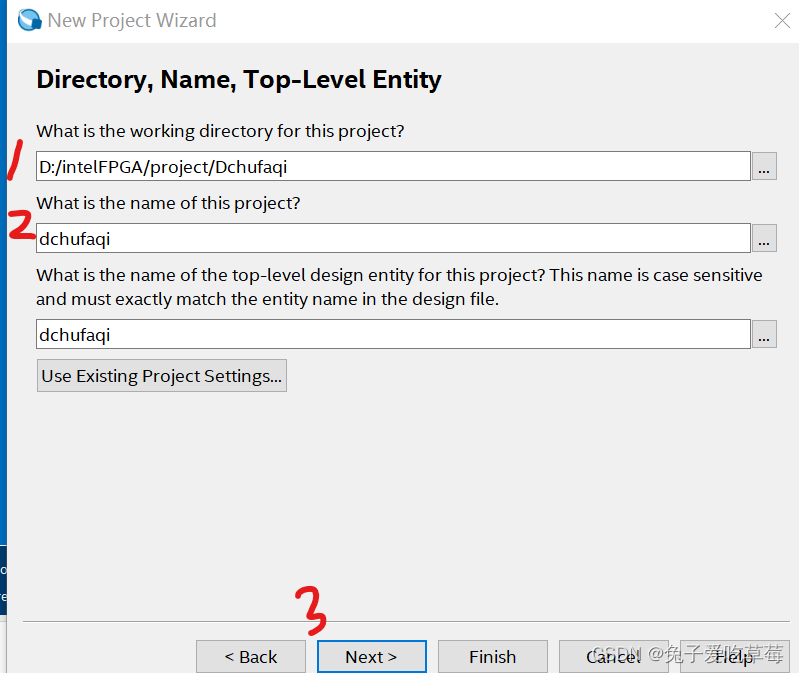

设置项目路径和项目名称

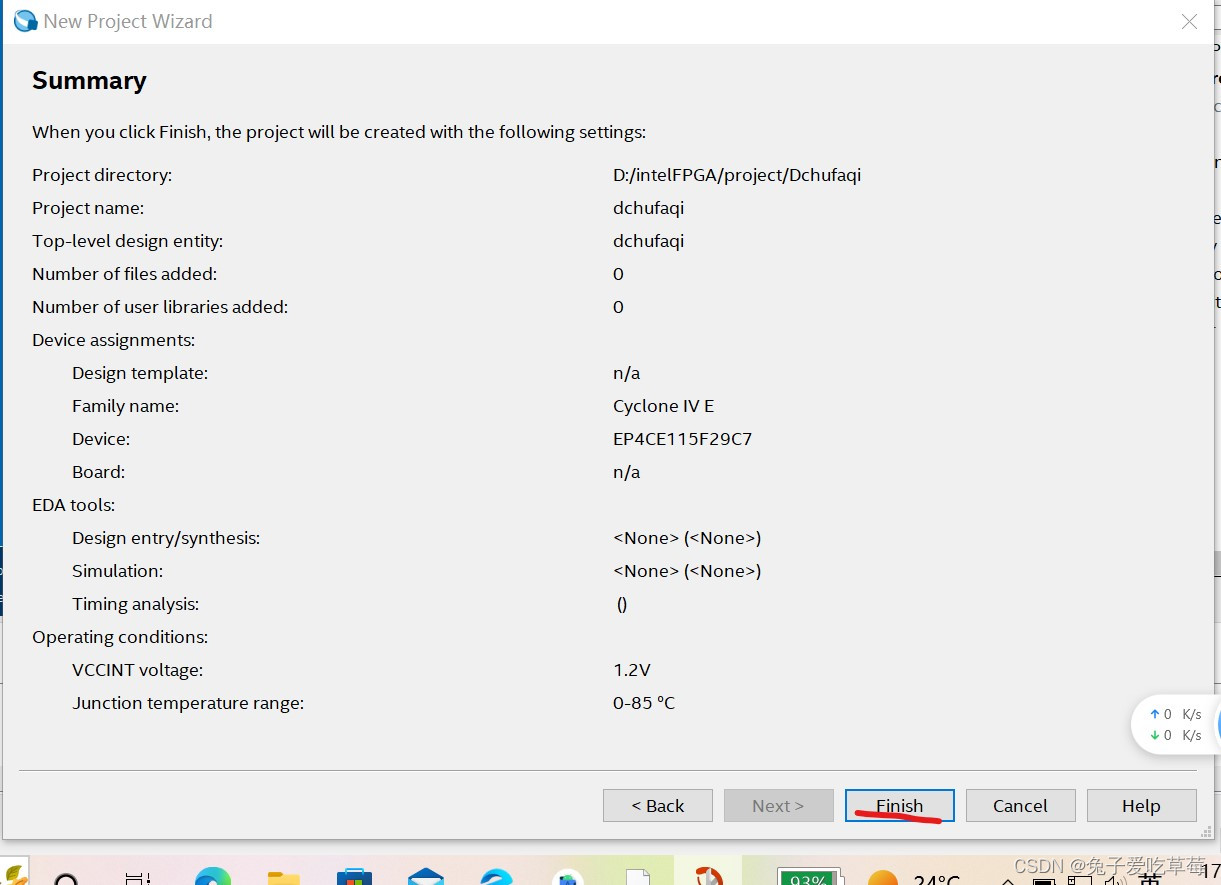

检查项目信息,点击finish

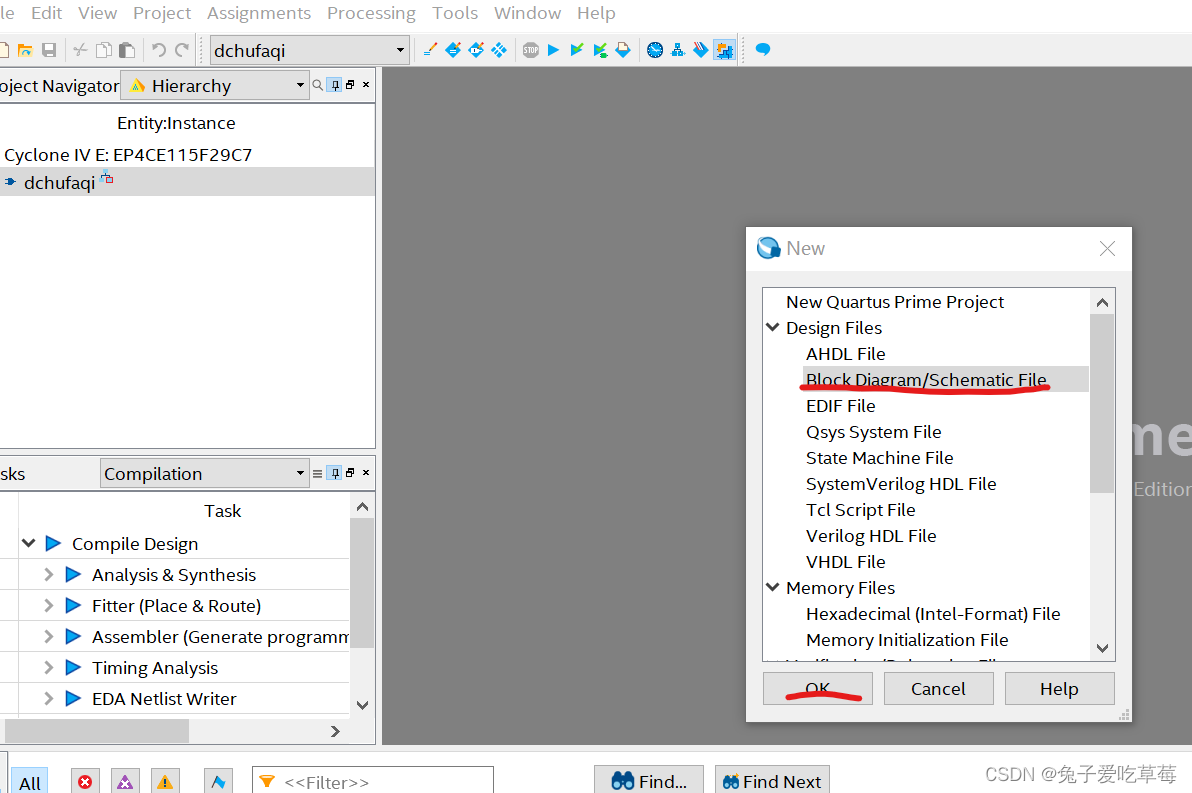

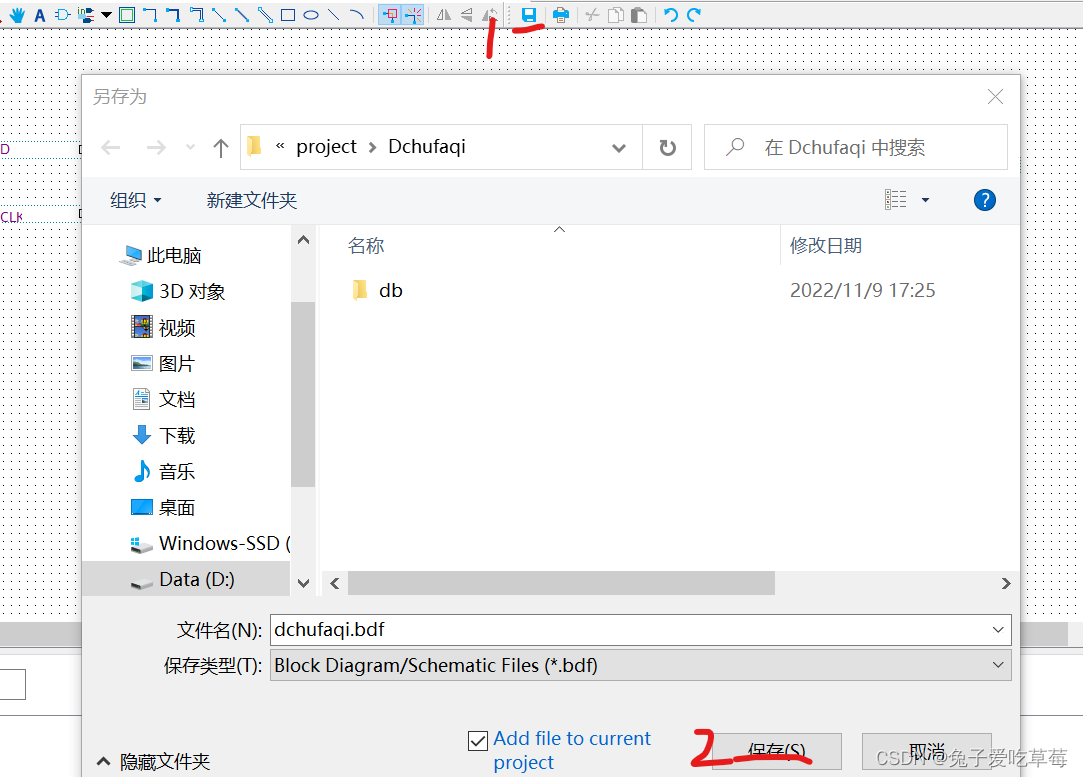

2、新建原理图文件

File->New

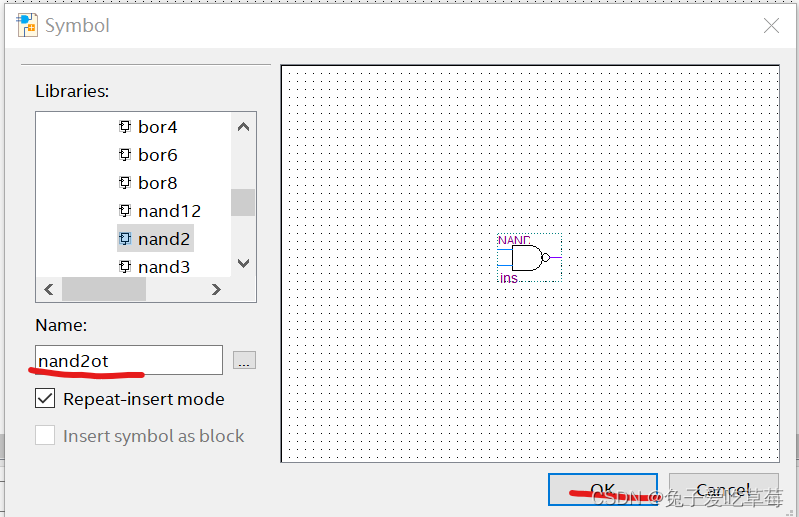

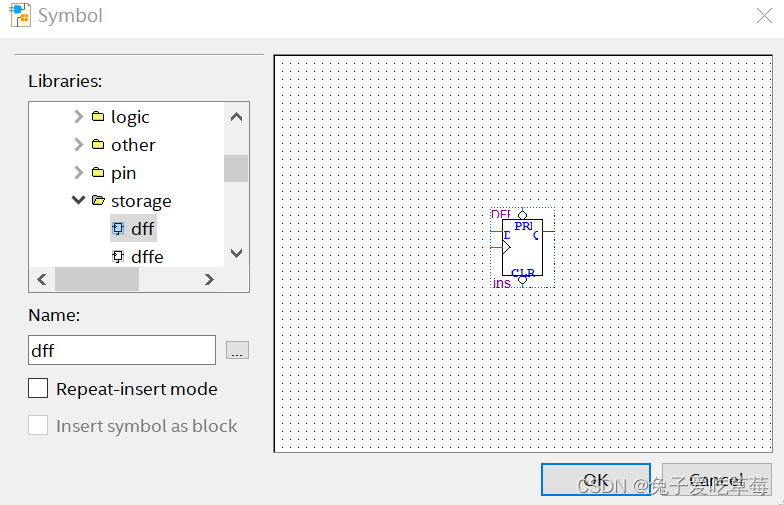

双击原理图空白处,从“ Symbol”窗中选择

需要的符号,或者直接在“name”文本框中键入元件名

4 个 nand2 与非门,1 个 not 非门,2个输入管脚和2个输出管脚,并连线,为输入输出管脚更改命名(双击名字位置就可以更改名字后面可以加几个空格以更好地显示出来)如下图:

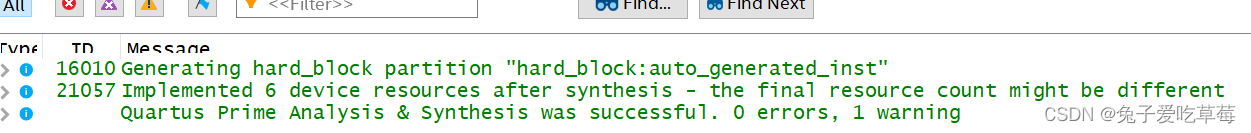

3、编译

无错则可进行下一步,有错进行原理图修改。

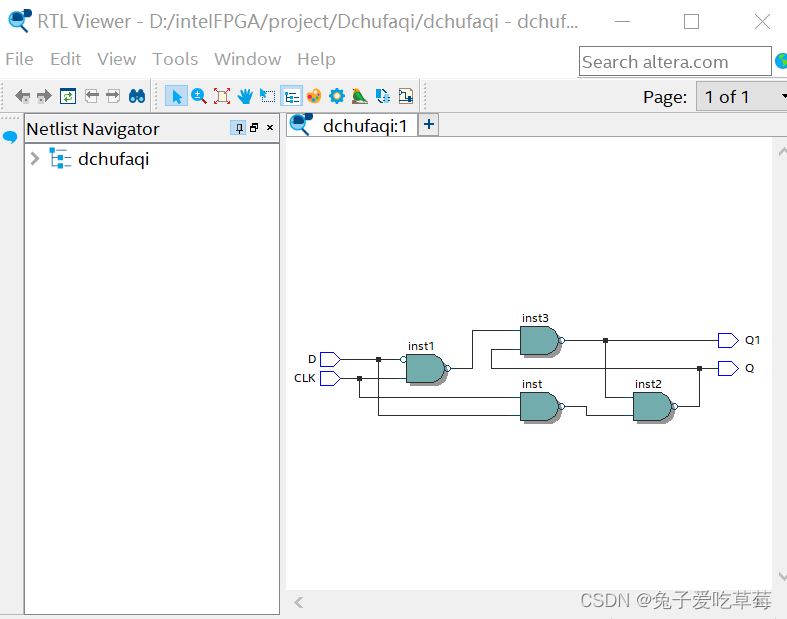

查看硬件电路图:点击【Tools】→【Netlist Viewers】→【RTL Viewer】。

4、仿真波形图

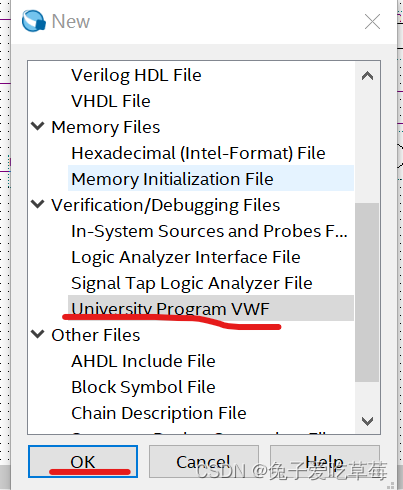

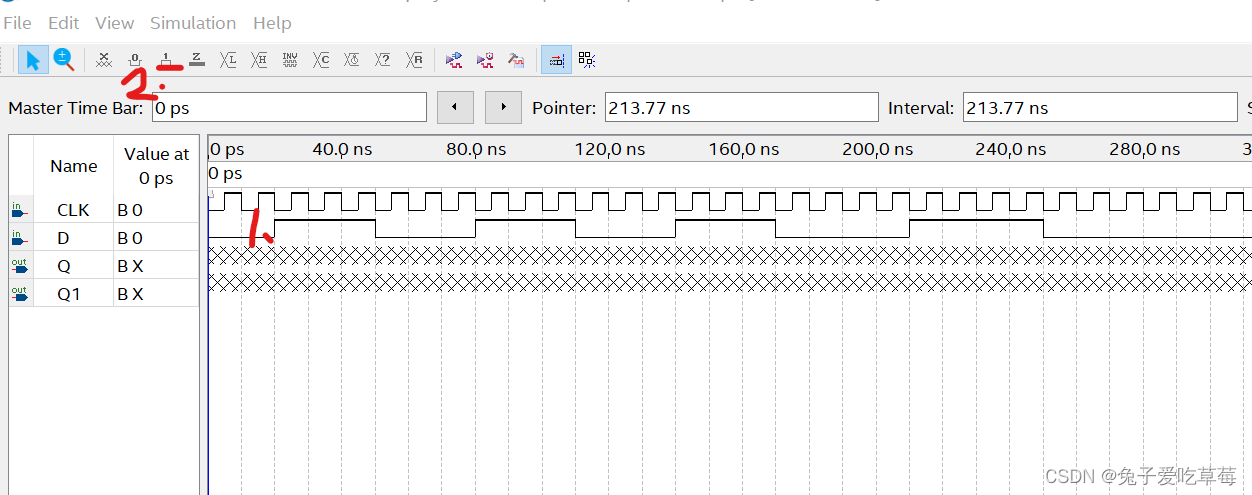

File->New->university program VWF->OK

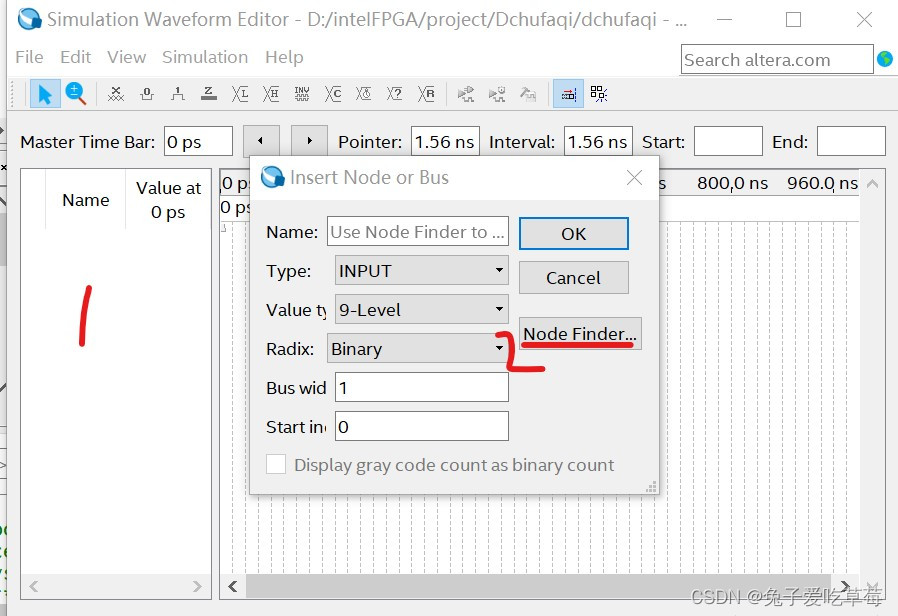

双击1位置出现“insert node or bus”对话框,点击“node finder”按钮。

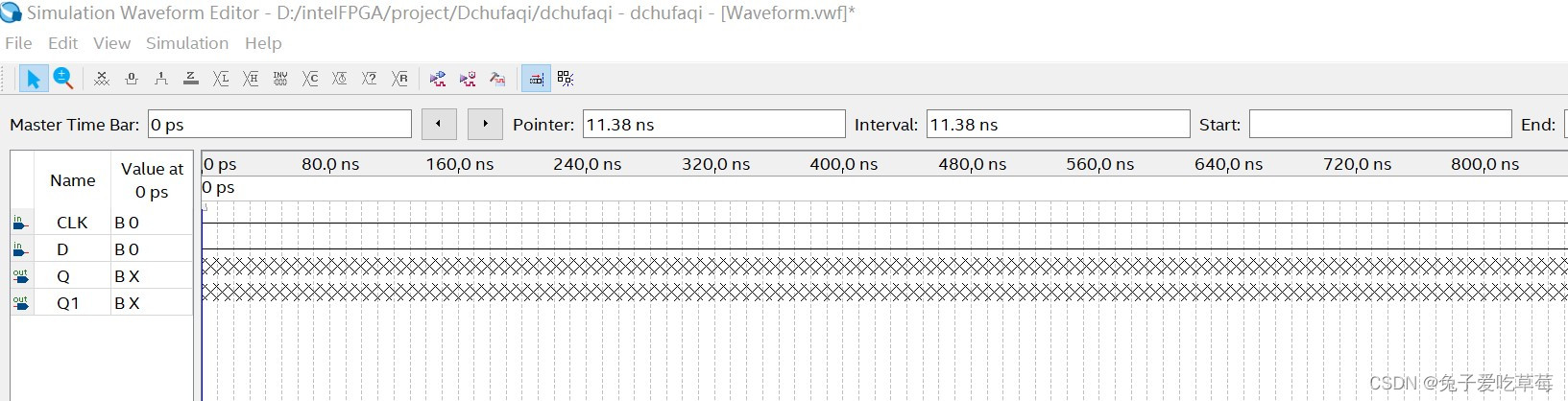

点击两次“OK”后,出现如图的波形文件

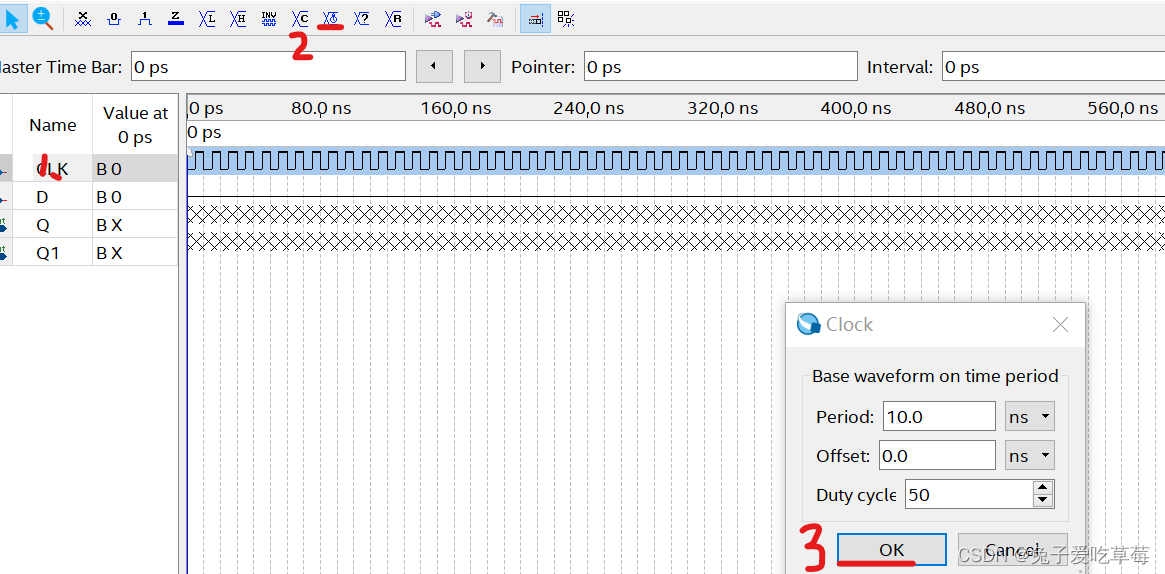

编辑输入CLK,产生时钟信号

把输入D随便设置几个低电平和高电平,随便选中几段点击2

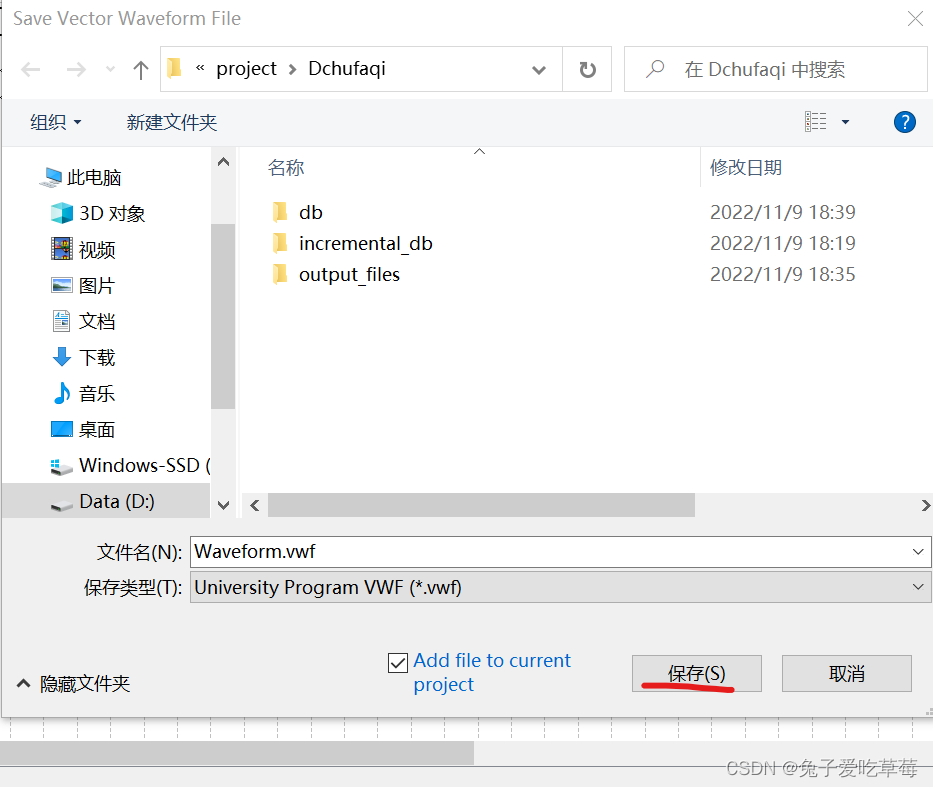

File->Save

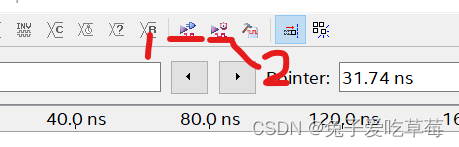

功能仿真

点击功能仿真编译按钮:

1.功能仿真

2.时序仿真

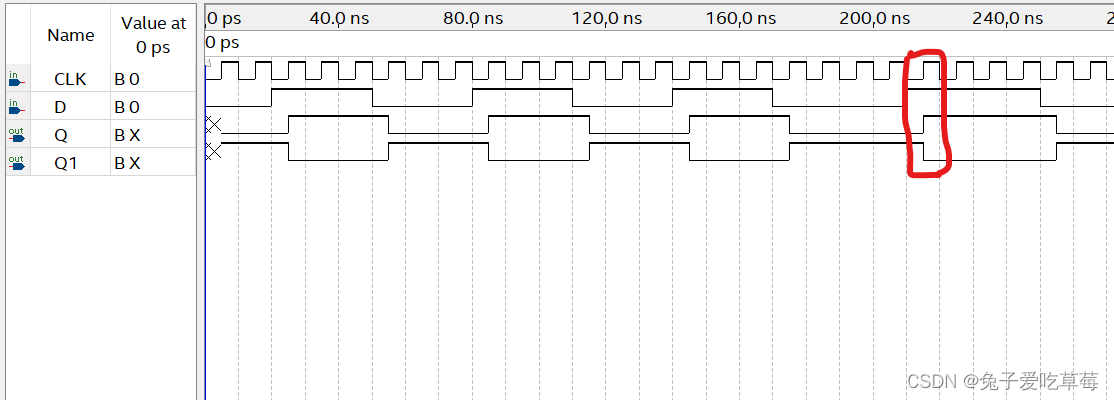

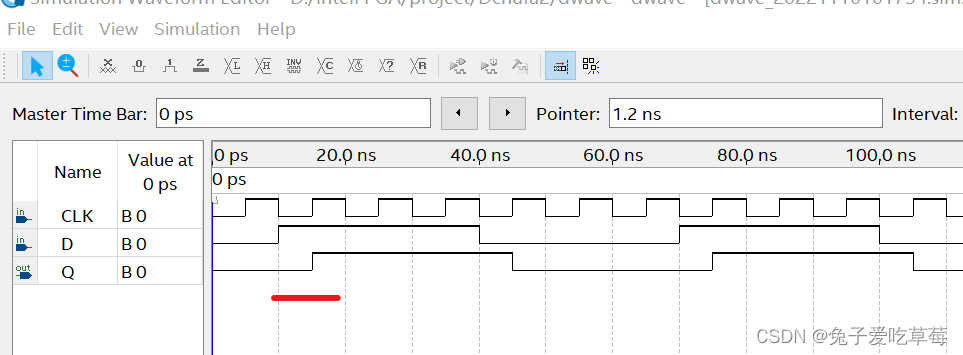

功能仿真

时序仿真

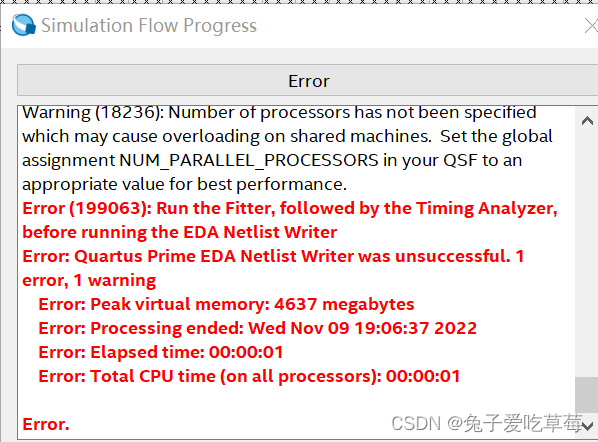

时序仿真会报错

进行相关设置:

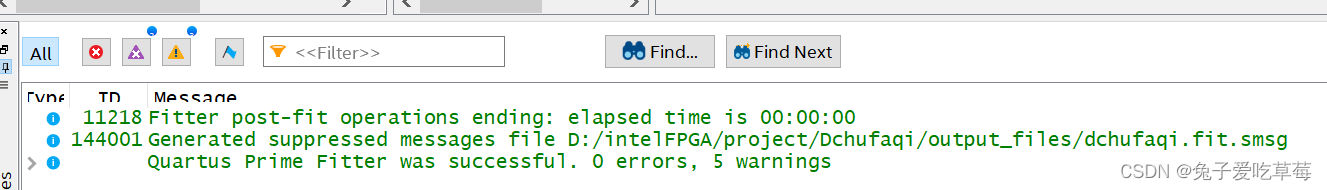

主界面【Processing】→【Start】→【Start Fitter】

没有错误

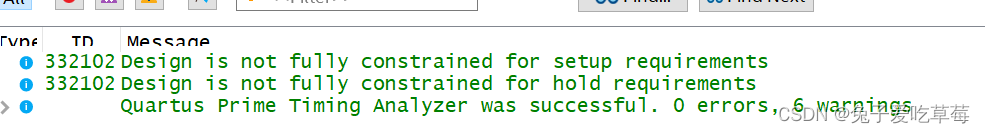

主界面【Processing】→【Start】→【Start Timing Analyzer】

返回VMF界面,再次点击时序仿真按钮就好了。

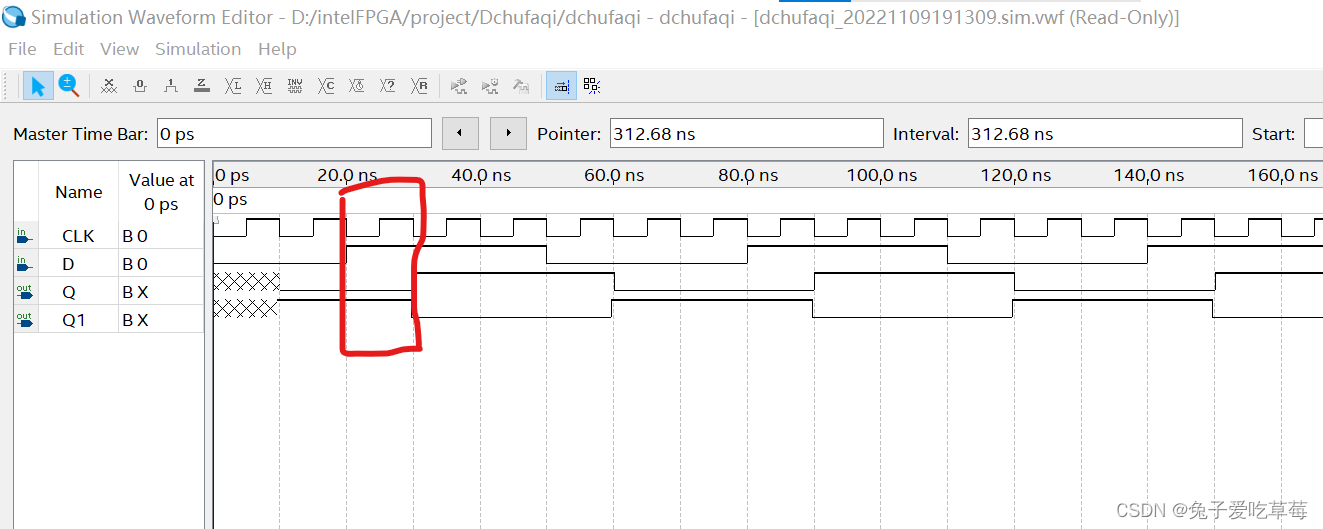

仿真结果如下(延迟了1个时钟周期):

三、调用D触发器并仿真

1.新建工程

同上述相同

2、新建原理图文件

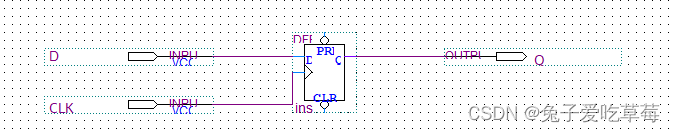

直接调用D触发器——dff

再添加输入输出管脚

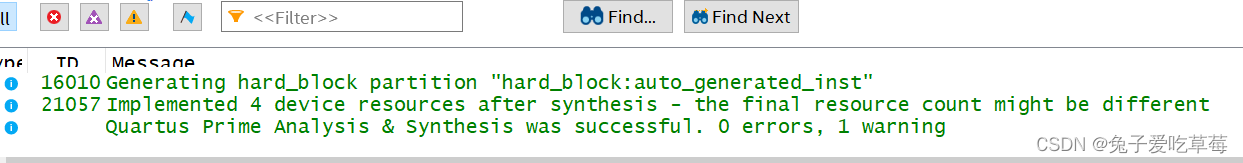

3、编译

保存编译

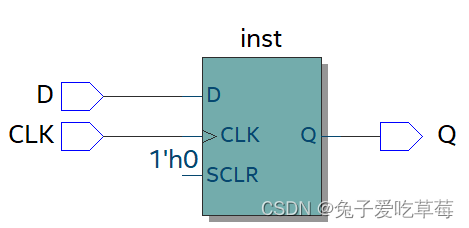

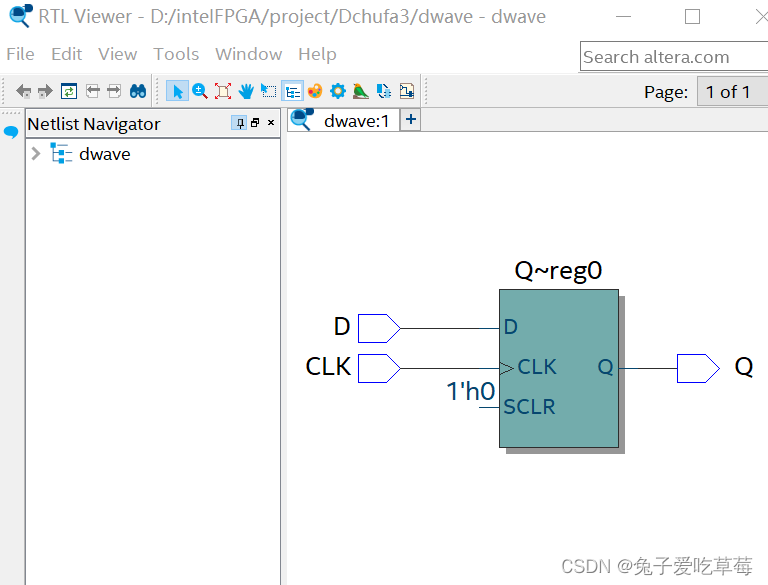

Tools→Netlist Viewers→RTL Viewer

不知道为什么它下面一直会多出来一个东西。。。。但做下来没有什么影响,但一直也去不掉。。。。。。

4、仿真波形图

功能仿真

主界面:File->New->university program VWF

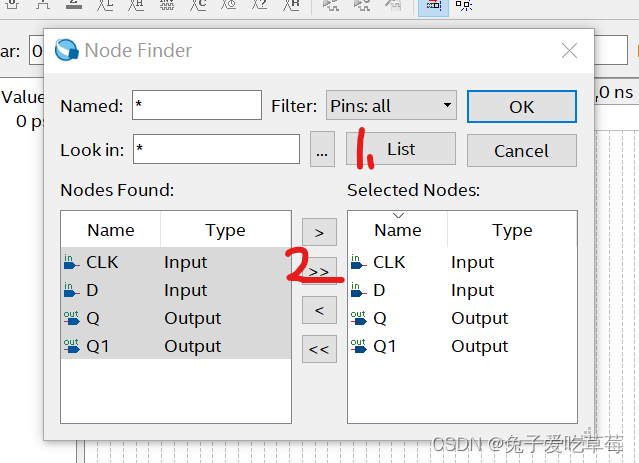

双击空白处->Node finder->List-> >> ->OK

编辑输入CLK,产生时钟信号

把输入D随便设置几个低电平和高电平

延迟了半个时钟周期

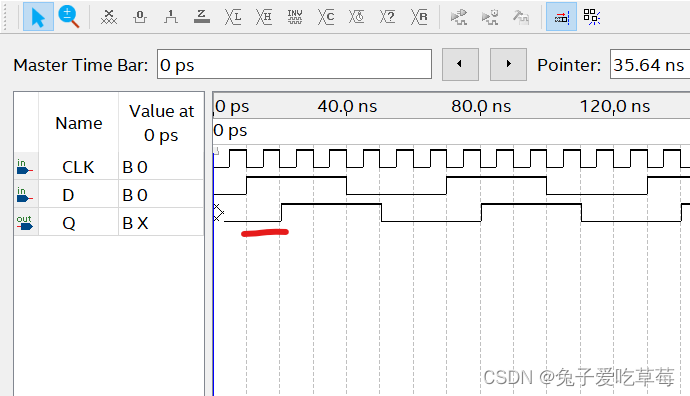

时序仿真

依然会报错,像 前面一样修改就好了

延迟了一个周期

四、用Verilog语言实现D触发器及时序仿真

1、创建工程

同上述相同

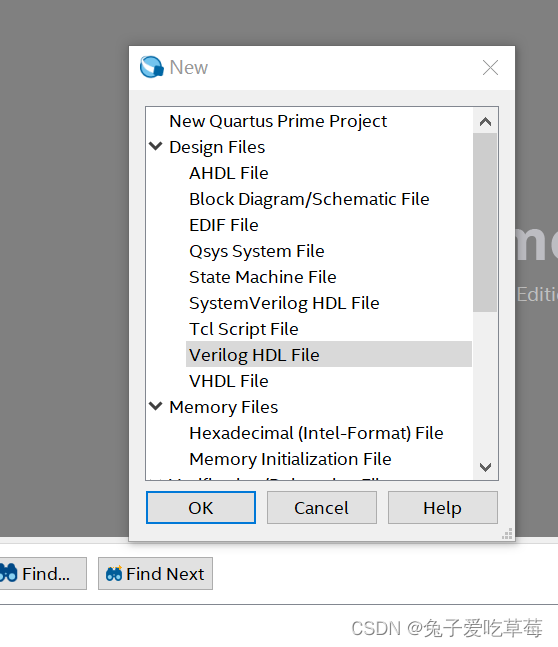

2、新建Verilog HDL 文件

File→New→Verilog HDL File

3、编写代码

//dwave是文件名

module dwave(D,CLK,Q);

input D;

input CLK;

output Q;

reg Q;

always @ (posedge CLK)

begin

Q <= D;

end

endmodule

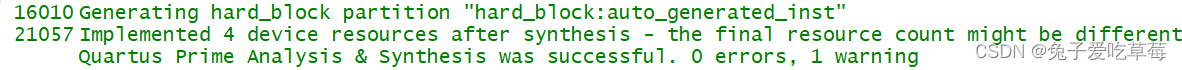

保存文件并编译

查看硬件电路图:点击Tools→Netlist Viewers→RTL Viewer

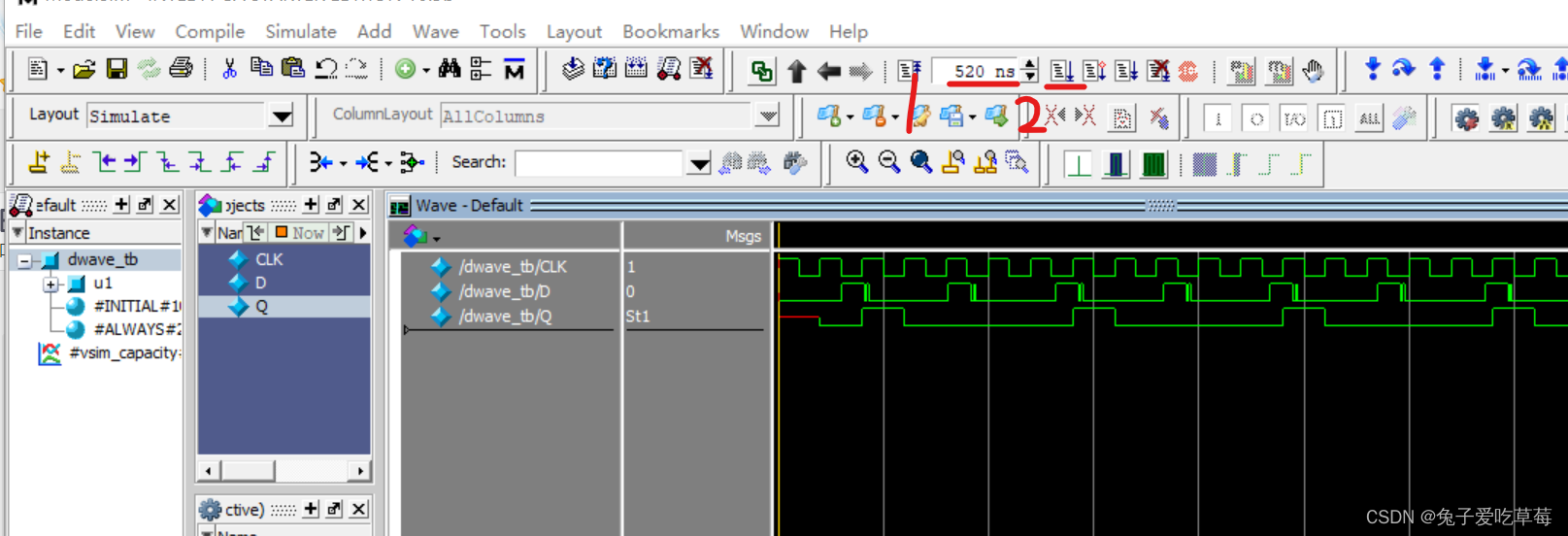

4、Modelsim仿真

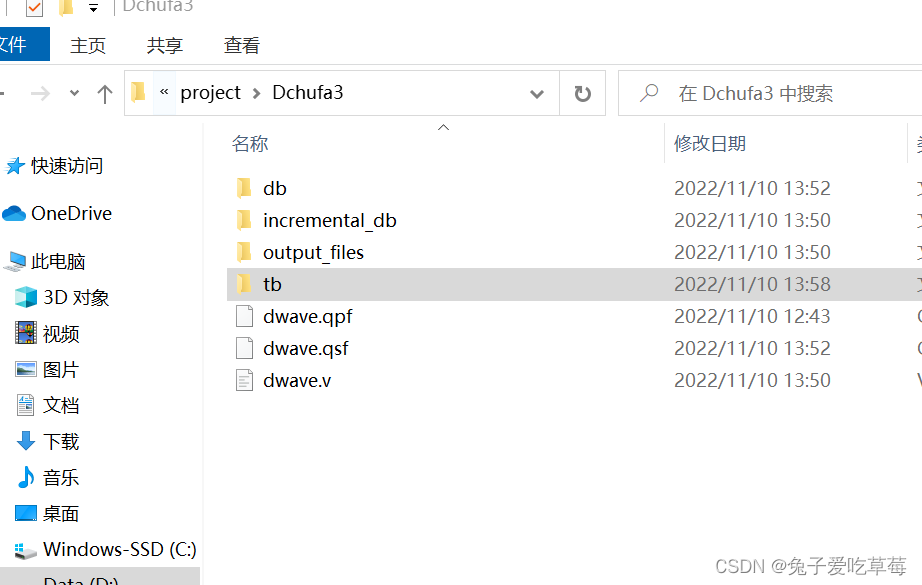

在Quartus创建的工程文件夹下新建一个 tb 文件夹;

打开ModelSim

File->Change Directory选择tb文件夹

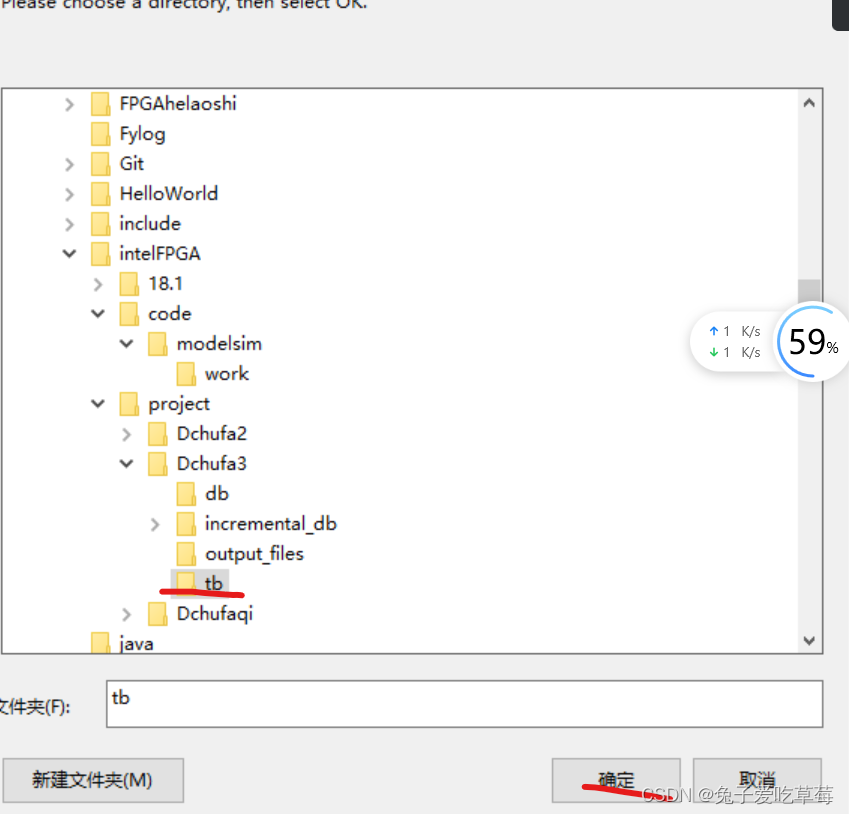

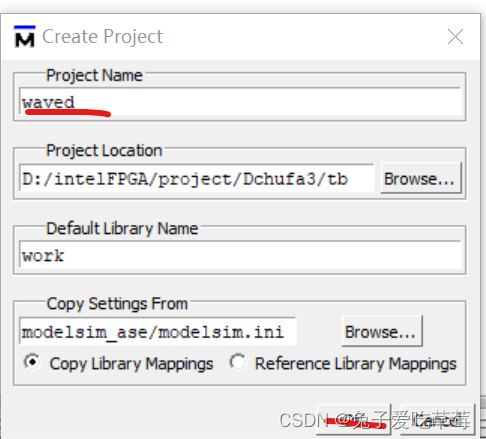

创建新项目

File->New->Project,填写工程名及选择路径

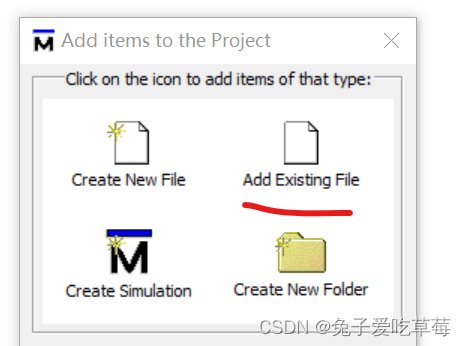

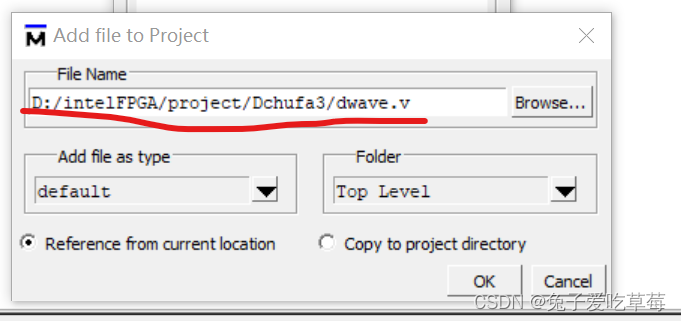

找到刚刚 Quatrus 编译生成的 .v 文件,再点击OK

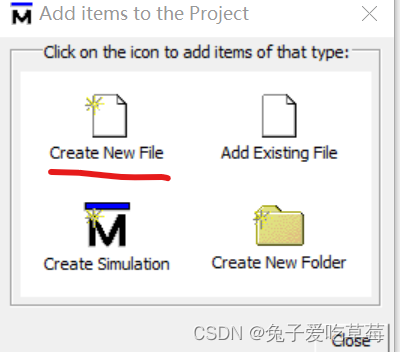

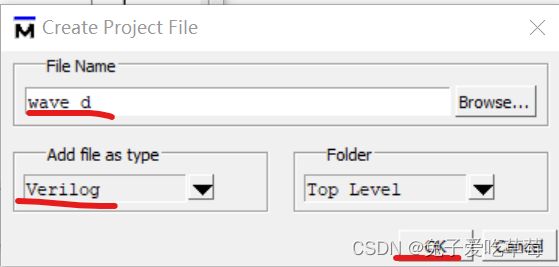

再创建一个新文件

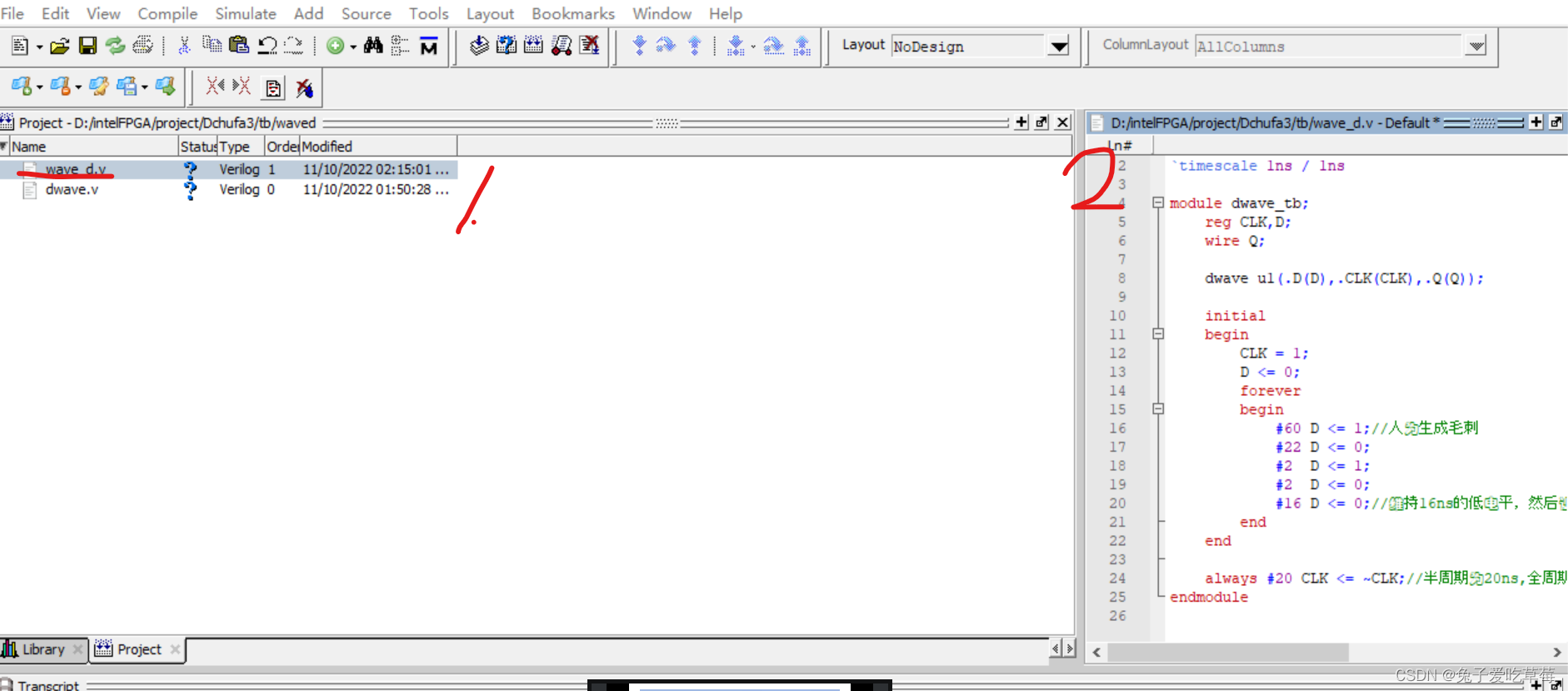

双击wave_d.v,添加测试代码

//测试代码

`timescale 1ns / 1ns

module dwave_tb;

reg CLK,D;

wire Q;

dwave u1(.D(D),.CLK(CLK),.Q(Q));

initial

begin

CLK = 1;

D <= 0;

forever

begin

#60 D <= 1;//人为生成毛刺

#22 D <= 0;

#2 D <= 1;

#2 D <= 0;

#16 D <= 0;//维持16ns的低电平,然后让它做周期性的循环

end

end

always #20 CLK <= ~CLK;//半周期为20ns,全周期为40ns的一个信号

endmodule

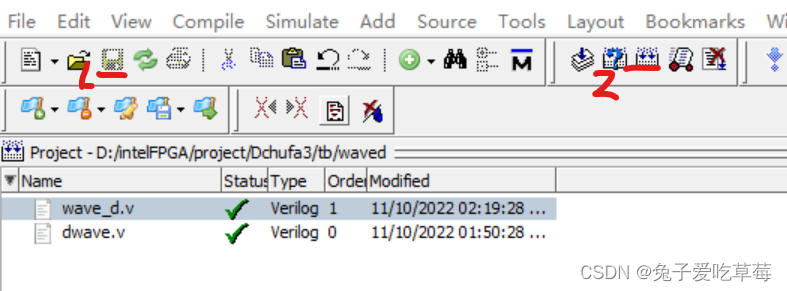

保存、编译

绿色小对勾说明编译成功

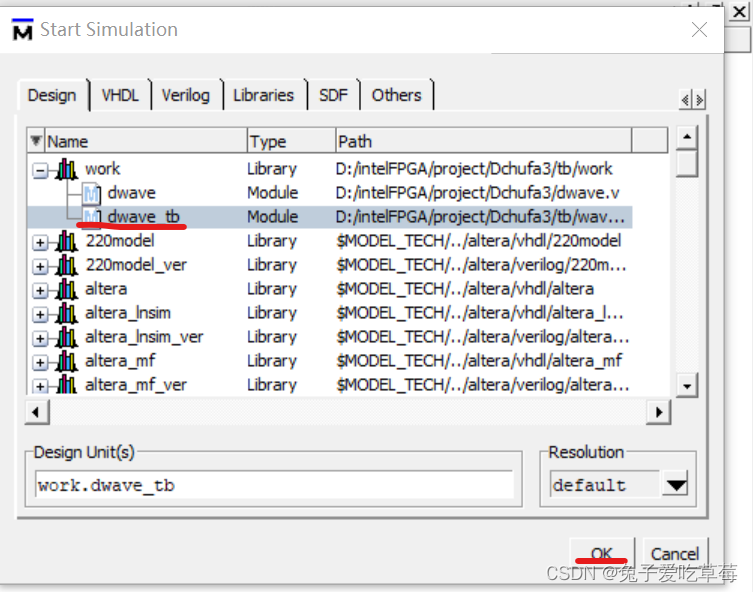

Simulate→Start Simulation…

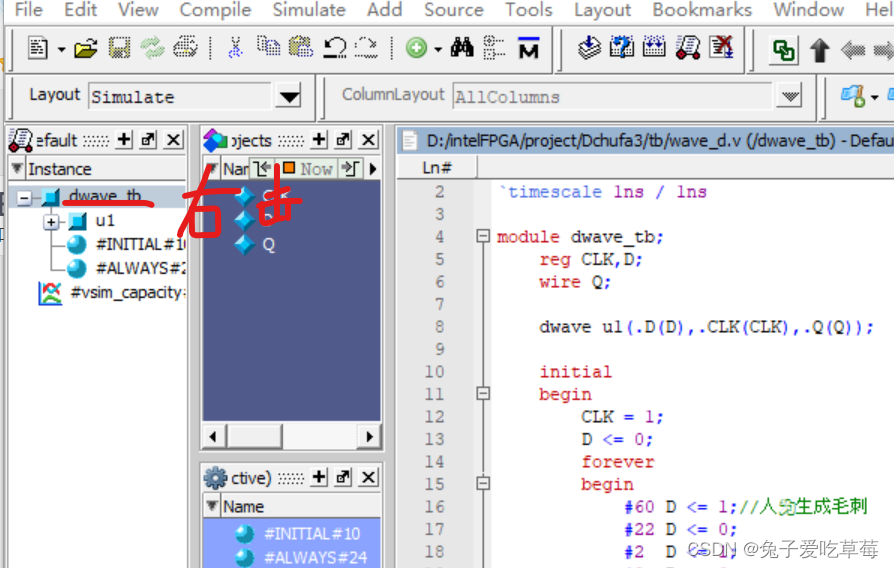

右击后点击Add Wave

总结

这三种方式的对比可以发现 当遇到复杂繁杂的电路图时,使用Verilog 语言会更加的方便。

参考资料

https://blog.csdn.net/weixin_46129506/article/details/123443865?spm=1001.2014.3001.5502

最后

以上就是超级手链最近收集整理的关于数字电路基础与Quartus入门——D触发器一、D触发器二、创建D触发器并仿真三、调用D触发器并仿真四、用Verilog语言实现D触发器及时序仿真总结参考资料的全部内容,更多相关数字电路基础与Quartus入门——D触发器一、D触发器二、创建D触发器并仿真三、调用D触发器并仿真四、用Verilog语言实现D触发器及时序仿真总结参考资料内容请搜索靠谱客的其他文章。

发表评论 取消回复