我是靠谱客的博主 鲜艳小甜瓜,这篇文章主要介绍Xilinx FPGA 笔面试问答题详解 - 第二章 Verilog HDL 语言与 Vivado第二章 Verilog HDL 语言与 Vivado,现在分享给大家,希望可以做个参考。

第二章 Verilog HDL 语言与 Vivado

笔记

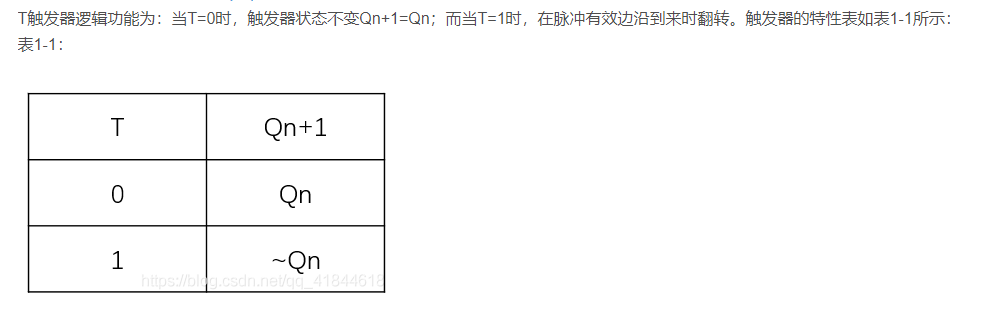

1. T触发器

- 对输入时钟信号进行2分频,等同于设计了一个T触发器;

2. wire型变量和reg型变量

- wire主要起信号间连接作用,用以构成信号的传递或者形成组合逻辑。因为没有时序限制,wire的赋值语句通常和其他块语句并行执行;

- wire不保存状态,它的值可以随时改变,不受时钟信号限制;reg型变量可以保存值,但是使用的存储设备是寄存器;

- 除了可以在模块module内声明,所有模块的输入input 和输出output默认都是wire型的;

- wire要使用assign语句进行赋值,且要在时序控制always块外进行赋值; reg型常用来表示always块内的指定信号,代表触发器,因为触发器只能在时钟的有效边沿改变值。

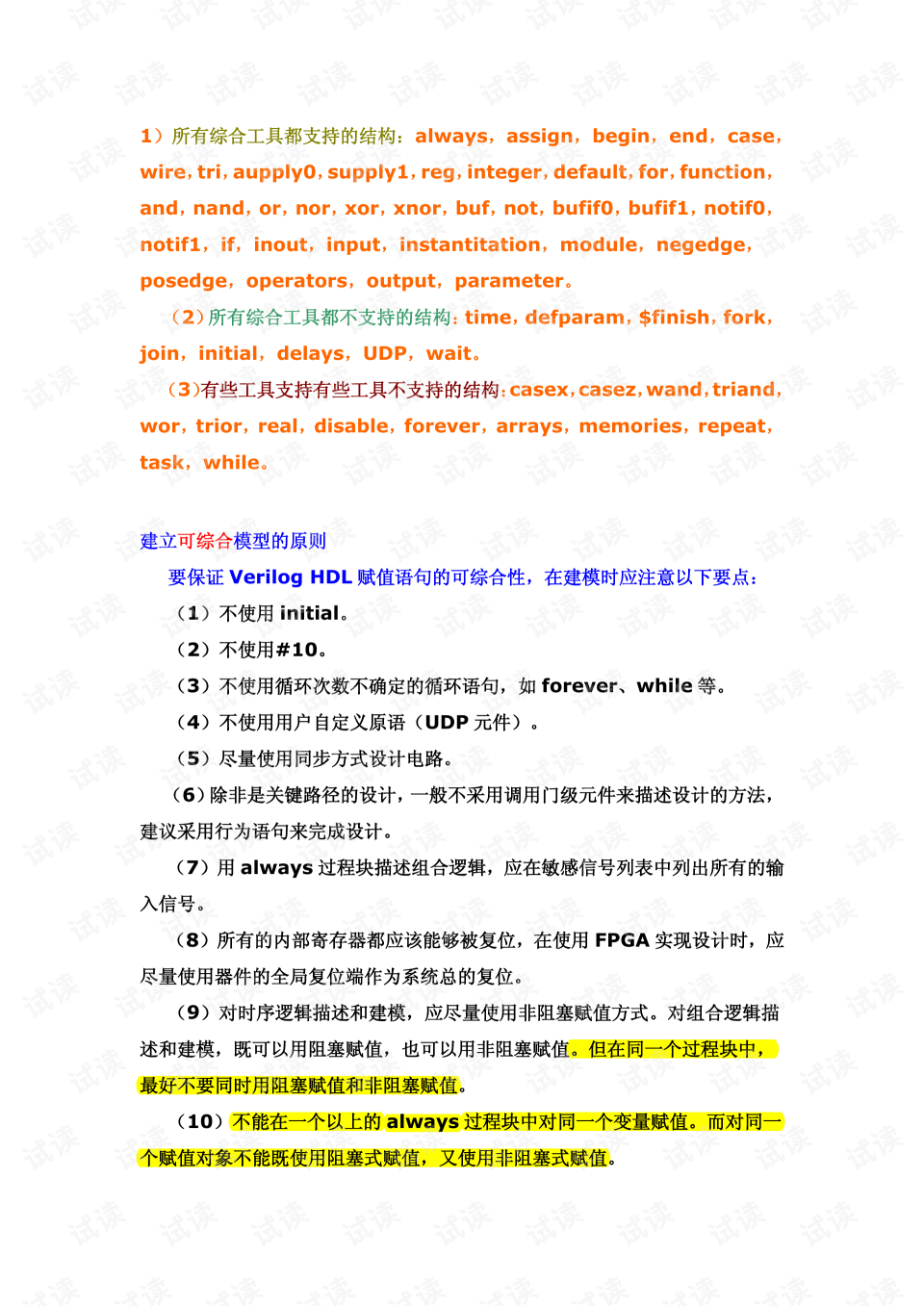

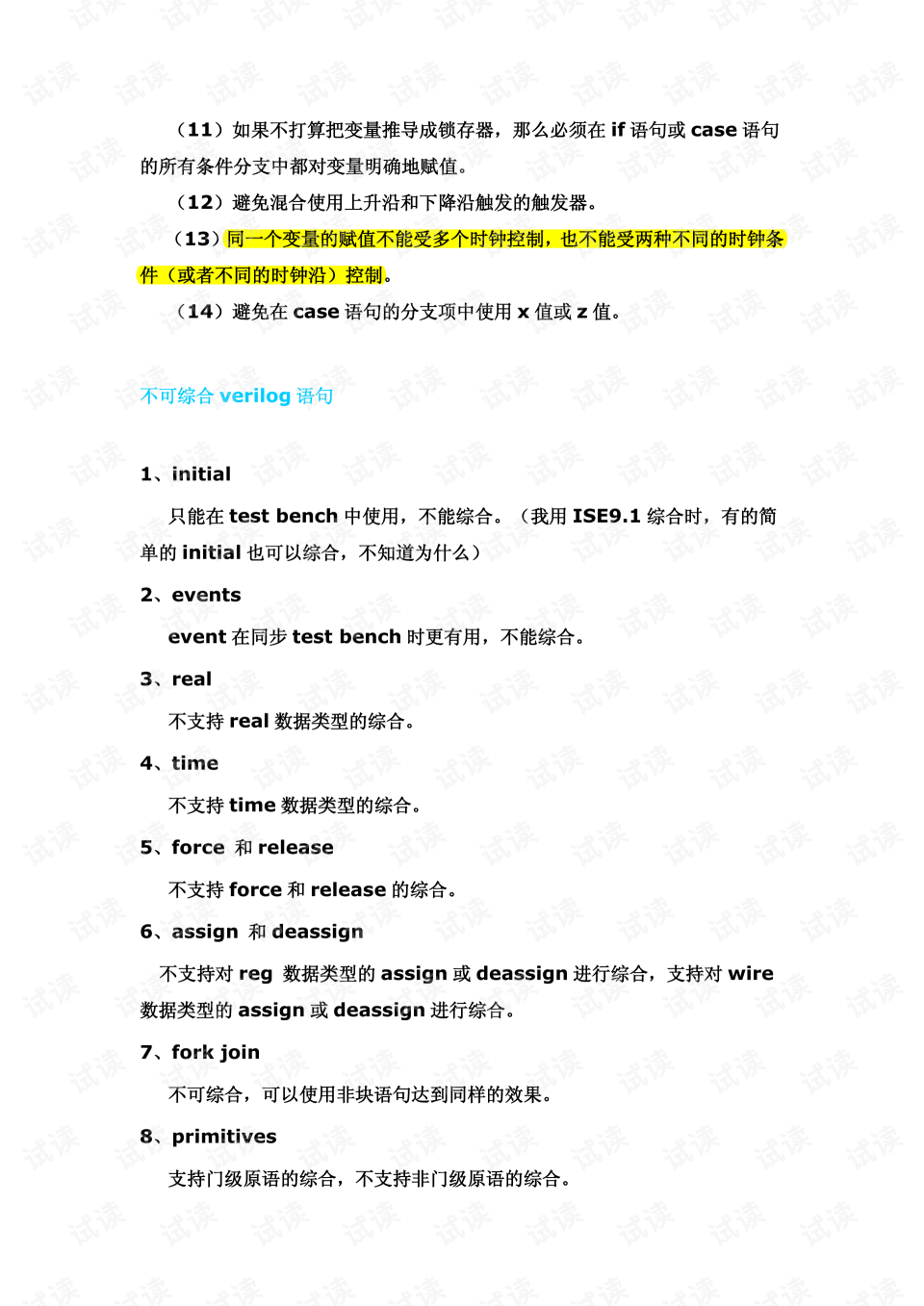

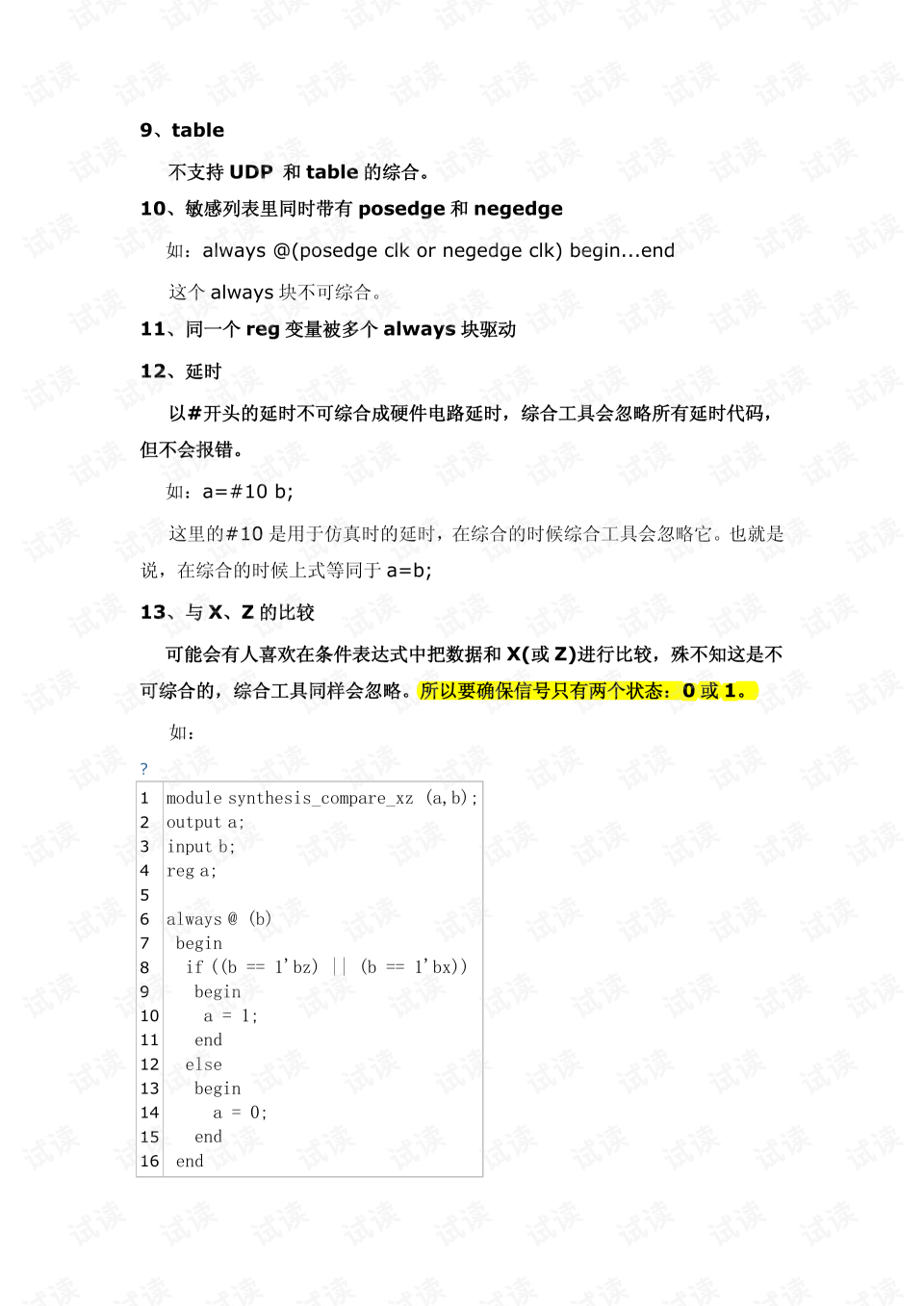

3. 可综合语句与不可综合语句

4. 可综合的变量类型

- reg

- wire

- integer

- 大多数的矢量类型(reg或者net)都被默认当做无符号数。integer和real是个例外,它们被默认为当做有符号数。

- 通常,real类型是不可综合的。

5. 如何避免引入锁存器

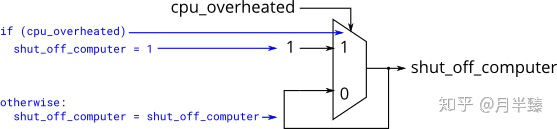

if (cpu_overheated) then shut_off_computer = 1;

if (~arrived) then keep_driving = ~gas_tank_empty

-

除了你指定的情况以外,会发生些什么,答案是什么也不会发生,输出保持不变。而这往往就导致了电路的错误,所以说语法正确的代码不一定能产生合理的电路(组合逻辑+触发器)。

-

输出保持不变,这就意味着电路需要记住当前状态,从而产生锁存器。组合逻辑(比如逻辑门)不能记住任何状态。

Warning (10240): ... inferring latch(es)

- 上述这类警告通常情况下代表错误,除非锁存器是故意生成的。

- 组合电路输出必须在所有输入的情况下都有值。这意味着必须需要else子句或着输出默认值。

错误:

always @(*) begin

if (cpu_overheated)

shut_off_computer = 1;

end

always @(*) begin

if (~arrived)

keep_driving = ~gas_tank_empty;

end

正确:

always @(*) begin

if (cpu_overheated)

shut_off_computer = 1;

else

shut_off_computer = 0;

end

always @(*) begin

if (~arrived)

keep_driving = ~gas_tank_empty;

else

keep_driving = ~arrived;

end

最后

以上就是鲜艳小甜瓜最近收集整理的关于Xilinx FPGA 笔面试问答题详解 - 第二章 Verilog HDL 语言与 Vivado第二章 Verilog HDL 语言与 Vivado的全部内容,更多相关Xilinx内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复