1、4位异步二进制加法计数器的设计:

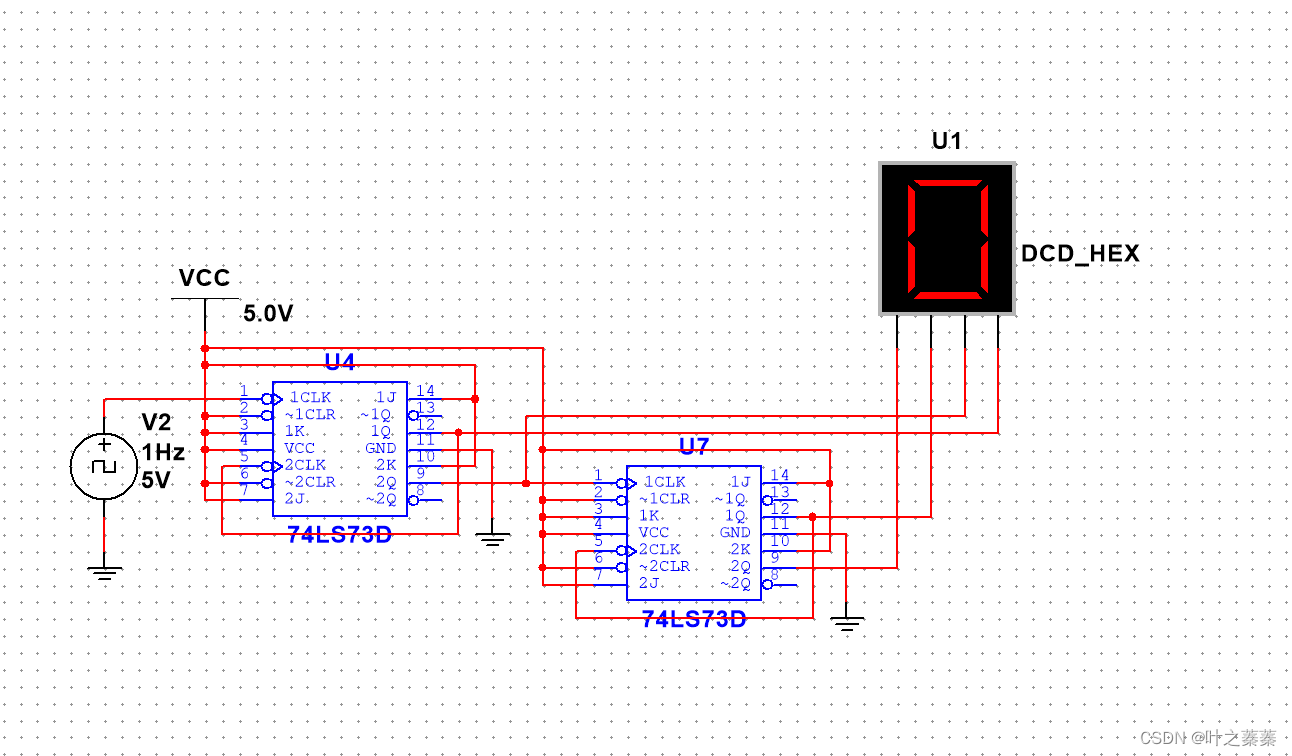

(1)用2片74LS73实现该电路,由CP端输入单脉冲,设计并画出4位异步二进制加法计数器电路图。

(2)由CP端输入单脉冲,测试并记录Q1~Q4端状态及波形。

四位二进制加法计数器状态迁移表如下:

| Q4n | Q3n | Q2n | Q1n | Q4n+1 | Q3n+1 | Q2n+1 | Q1n+1 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 |

| 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

根据该表可设计电路:(以下是本人的设计图,可以参考)

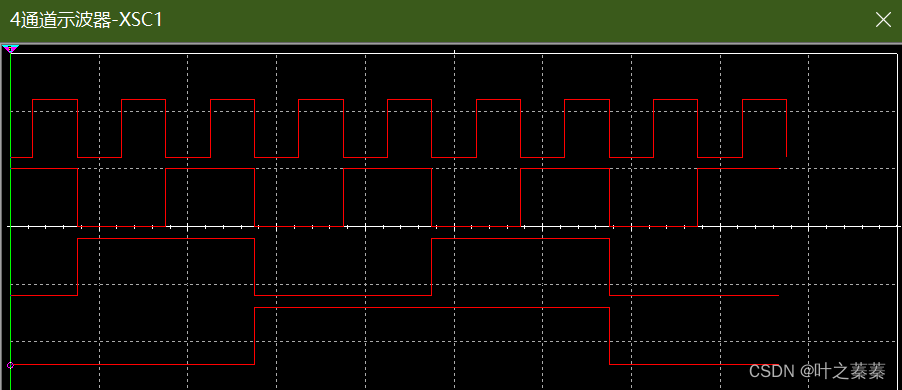

将Q1~Q4接入四通道示波器,可以得到以下结果:

如果该结果与理论结果相同,可认为设计成功。

2、异步二-十进制加法计数器的设计:

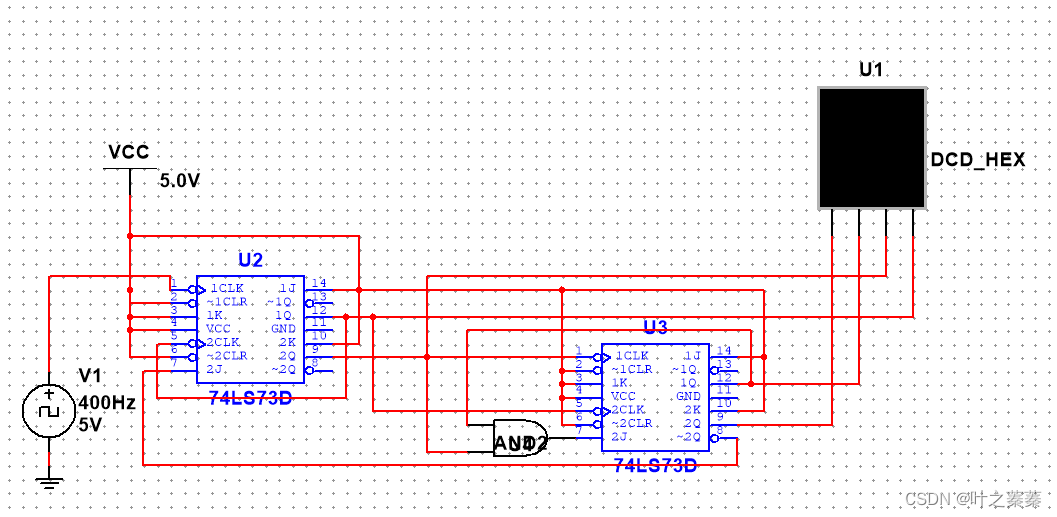

(1)设计并画出4位异步8421BCD加法计数器的电路图。

(2)用2片74LS73实现该电路,由CP端输入单脉冲,测试并记录Q1~Q4端状态及波形。

四位8421BCD码加法计数器状态迁移表如下:

| Q4n | Q3n | Q2n | Q1n | Q4n+1 | Q3n+1 | Q2n+1 | Q1n+1 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | X | X | X | X |

| 1 | 0 | 1 | 1 | X | X | X | X |

| 1 | 1 | 0 | 0 | X | X | X | X |

| 1 | 1 | 0 | 1 | X | X | X | X |

| 1 | 1 | 1 | 0 | X | X | X | X |

| 1 | 1 | 1 | 1 | X | X | X | X |

参考电路图如下:

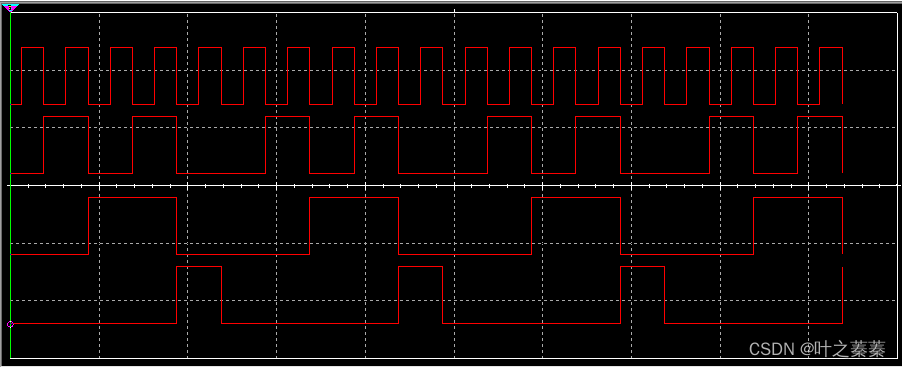

将Q1~Q4接入四通道示波器有以下结果:

以上是本人个人实验结果,如有错误欢迎指正

最后

以上就是典雅鲜花最近收集整理的关于用74LS73设计四位二进制加法计数器和8421BCD加法计数器1、4位异步二进制加法计数器的设计:2、异步二-十进制加法计数器的设计:的全部内容,更多相关用74LS73设计四位二进制加法计数器和8421BCD加法计数器1、4位异步二进制加法计数器内容请搜索靠谱客的其他文章。

发表评论 取消回复