目录

- 一、“组合”与“时序”

- 二、同步时序电路 与 异步时序电路

- 三、同步时序电路

- 四、双稳态

- 4.1 数字分析

- 4.2 模拟分析

- 4.3 亚稳态特性

- 五、锁存器(Latch)与触发器(Flip-Flop)

- 参考资料

一、“组合”与“时序”

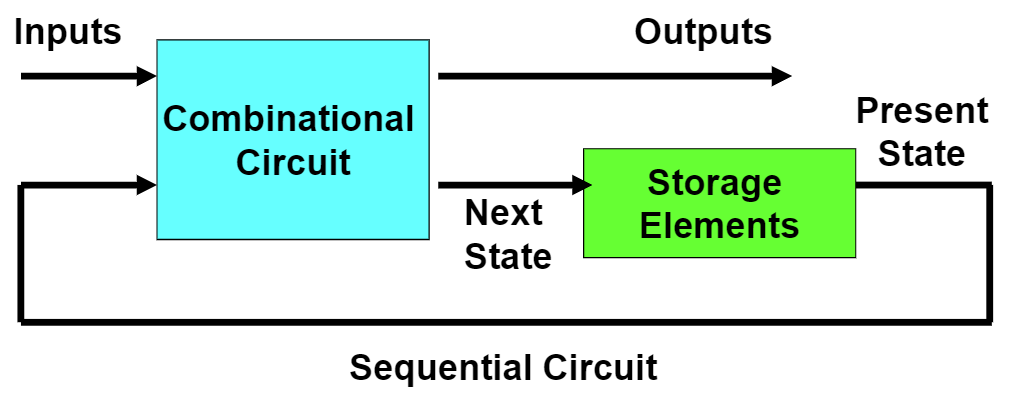

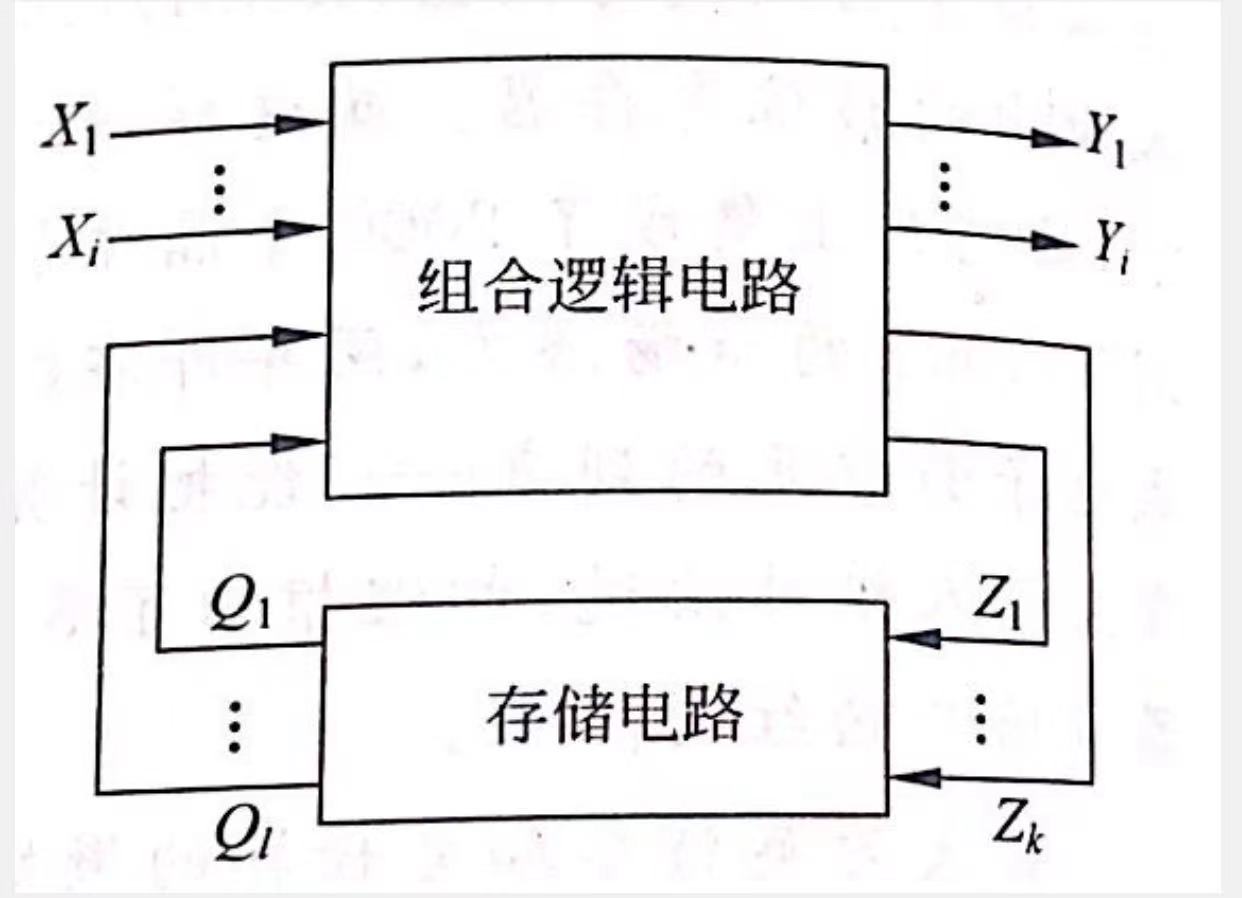

逻辑电路分为两大类:组合逻辑电路和时序逻辑电路。

组合逻辑电路的输出只取决于当前的输入;时序逻辑电路的输出不仅取决于当前的输入,而且取决于过去的输入序列。[1]

下面是我看到的时序电路的两种不同的模型画法:

图片来源[1]

图片来源[1]

二、同步时序电路 与 异步时序电路

根据触发器(flip-flop)的动作特点不同,时序电路可以进行这样的分类。

若时序电路中,所有触发器状态的变化是在同一时钟信号(clock signal)作用下同时发生的,就称为同步时序电路。

若时序电路中,没有统一的时钟信号,各触发器状态的变化不是同时发生的,而是有先有后的,这类时序电路称为异步时序电路。[1]

那么现在问题出现了,什么是触发器,什么是时钟信号?

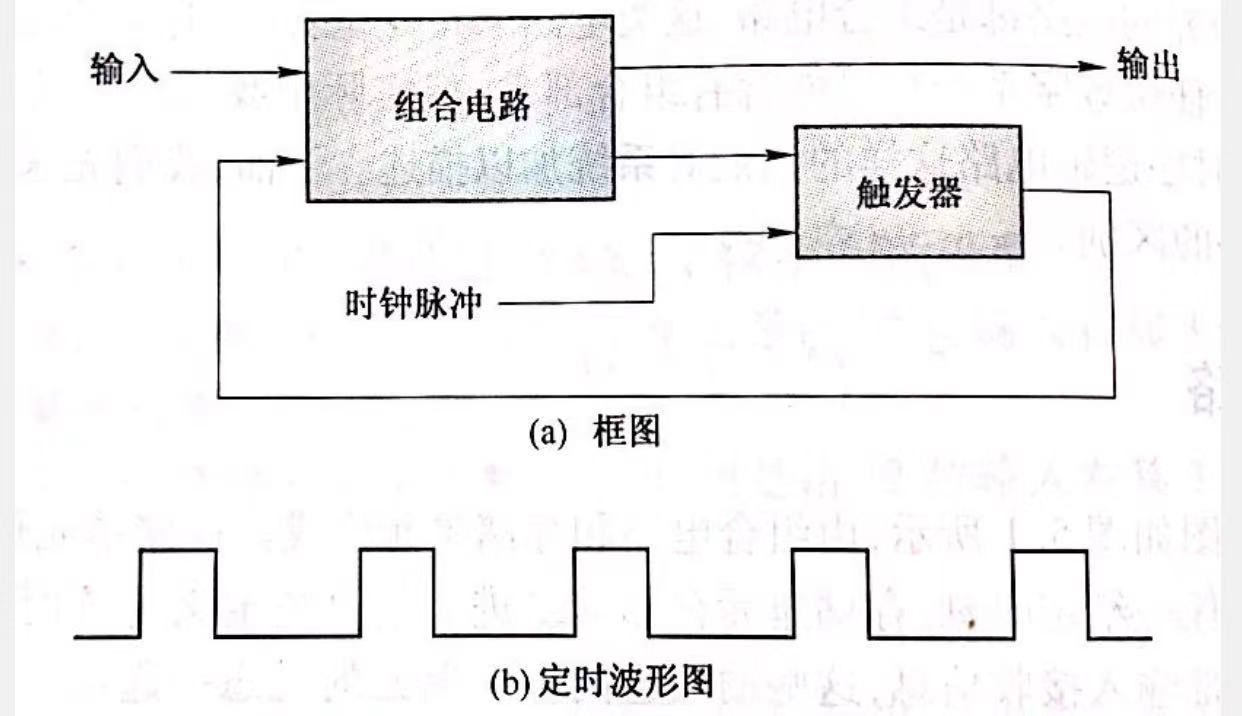

三、同步时序电路

图片来源:[2]

图片来源:[2]

触发器从组合电路接受输入信号,从时钟获得固定间隔发生的脉冲。

所以到底什么是时钟信号,用它来干什么呢?

触发器的状态只有在时钟脉冲变化(例如,当时钟脉冲从0变化为1)的时候(这种时候称作有效的时钟信号)才会改变。当时钟信号无效时,即使组合电路的输出发生变化,触发器输出也不会改变。[1]

四、双稳态

4.1 数字分析

入门推荐阅读:双稳态与单稳态

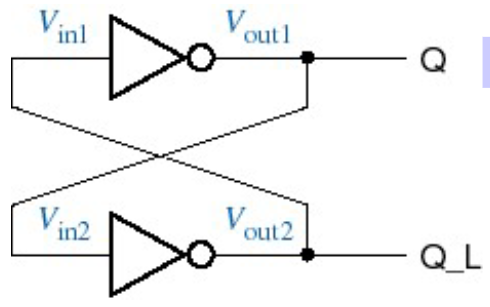

上图是最简单的时序电路,是由一对反相器(NOT)形成的一个反馈回路。这个时序电路没有输入,但却有2个输出,即Q和Q_L。

上图是最简单的时序电路,是由一对反相器(NOT)形成的一个反馈回路。这个时序电路没有输入,但却有2个输出,即Q和Q_L。

如果Q为低电平,那么下面的反相器输入低电平,输出高电平;这又迫使上面的反相器输出维持为低电平,这是一种稳定状态。如果Q为高电平,那么下面的反相器输入为高电平,输出低电平,从而迫使Q维持高电平,这是另一种稳定状态。

双稳态元件没有输入,因此也无法改变或控制它的状态。只要一接上电源,他就随机出现两种状态中的一种,并永久地保持这一状态。

4.2 模拟分析

因为没有接触过模拟电路这门课程,所以具体的分析过程就不在这里展示了。

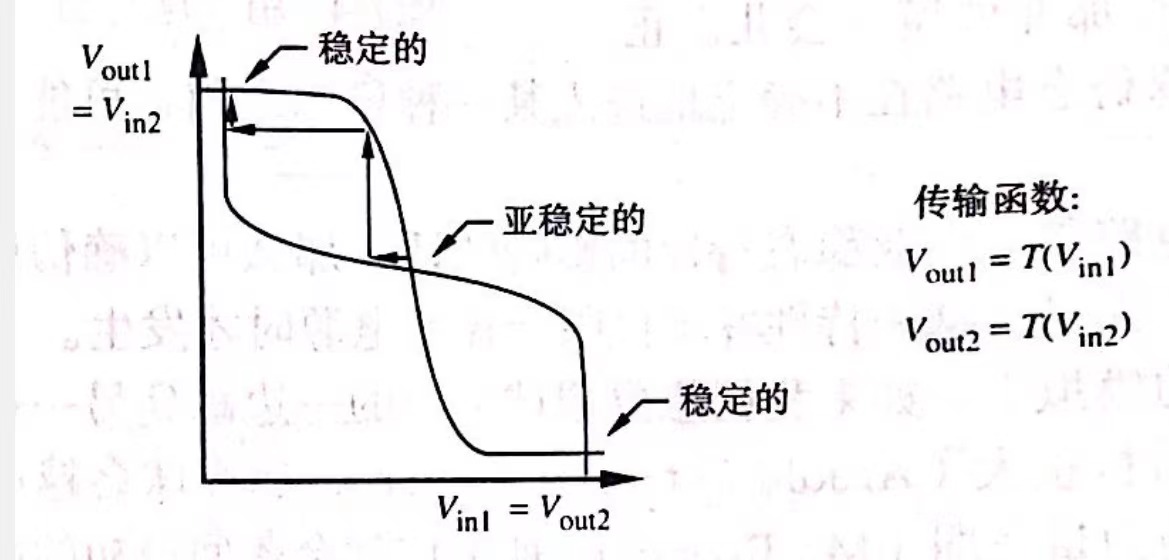

从上图中找平衡点,也就是两个传输函数曲线的相交点。令人惊讶的是,在图中找到的平衡点不是2个而是3个。其中标有“稳态(stable)”的2个平衡点对应着前面数字分析时所确定的2个状态。

图中标有“亚稳态(metastable)”的第3个平衡点,正好处在有效逻辑1电平和有效逻辑0电平的中间位置上,所以不是有效的逻辑信号。如果能够使电路工作于亚稳态点,那么从理论上说电路可以无限期地停留在该状态。

4.3 亚稳态特性

Metastable occurs at the point where both inputs are halfway between 0 and 1.

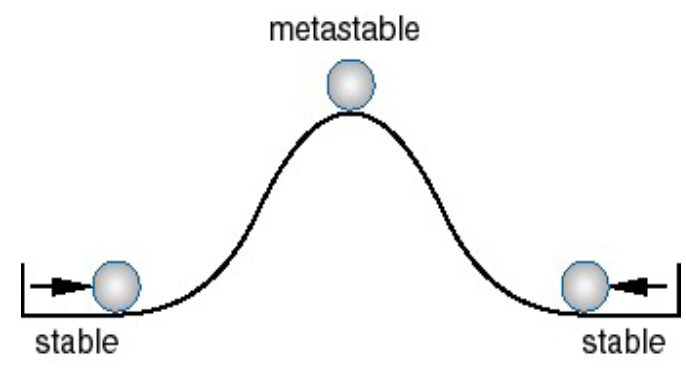

这个点并不是真正稳定的,因为随机的噪声会驱使工作于亚稳态点的电路转移到一个稳定的工作点上去。

如果在高处扔一个球,那么求就可能立即滚到山的这边或者那边。但是如果正好把球放在山顶上,在风、动物或者地震驱使它滚下去之前,它可能不稳定的在那儿停留一会。

双稳态电路在不确定地进入某一种稳态之前,可能会在也稳态状态停留一段不可预测的时间。

如果要把球从山的一边踢到另一边去,想一想如果用的力气很大、很小、或者正好的情况下,会发生什么?

将这一情况加到电路里。下面会学的S-R锁存器,加载S输入端的脉冲会使锁存器的状态从0状态变到1状态。对S输入端有一个最小脉冲宽度的限制。[3]

五、锁存器(Latch)与触发器(Flip-Flop)

锁存器和触发器是大多数时序电路的基本构件。

有些课本和数字设计者可能不会刻意地去区分锁存器和触发器。我认为,我们作为学习者,明白作者的意图,并加以记忆理解就可以了。

所有的数字设计者都把这样一种时序器件称为触发器(Flip-Flop),这种器件平时对输入进行采样,并只在时钟信号所确定的时刻改变其输出。

多数数字设计者又把另外一种时序器件称为锁存器(Latch),这种器件不断监测其所有输入,并独立于时钟信号而在任何时刻都可以改变输出。[3]

其最大的区别在于,触发器是边沿触发,锁存器则是电平触发。

锁存器:SR锁存器、带有控制输入的SR锁存器、D锁存器

SR锁存器_个人整理

触发器:主从D触发器、主从JK触发器

RS锁存器,D锁存器、D触发器简介

参考资料

[1][2][3]其实是三本不同的书,但是文章是一段时间以前写的,那时候写完,但是没加上参考资料的信息。今天看了看这文章对自己会有一些帮助,所以就决定要发出来,结果我忘记是哪三本书了呜呜呜…

dbq写书的老师们,哪天我想起来了,或者我在哪一本书里发现有文章里引用了的话语,我一定回来加到文章里。

最后

以上就是眼睛大苗条最近收集整理的关于【时序逻辑电路(sequential logic circuit)】的全部内容,更多相关【时序逻辑电路(sequential内容请搜索靠谱客的其他文章。

发表评论 取消回复