前言

《数字电子技术基础》第6.4节学习笔记,本人在编写Verilog时序逻辑代码时,关于这一部分的状态图需要好好学一下。

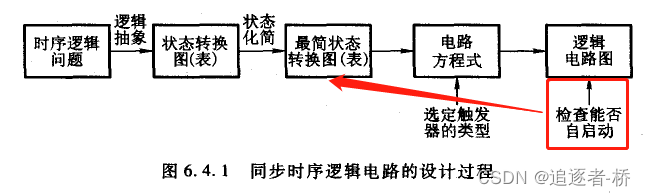

6.4.1 同步时序逻辑电路的设计方法

一般步骤

一、逻辑抽象,求出状态转换图或状态转换表

- 确定输入输出变量、电路状态数。

- 定义输入输出逻辑状态以及每个电路状态的含义,并对电路状态进行编号。

- 按设计要求列出状态转换表,或画出状态转换图。

二、状态化简

若两个状态在相同的输入下有相同的输出,并转换到同一次态,则称为等价状态;等价状态可以合并。

是否合并需要看状态的个数,如果8个状态时,需要3位二进制编码,此时则不需要进行状态合并;如果9个状态时,则需要4位二进制编码,如果此时进行状态化简,可以将其化简为3位二进制编码,此时通过简单化简就可以实现触发器和门电路的减少。

三、状态分配(编码)

- 确定触发器数目。

- 给每个状态规定一个代码(通常编码的取法、排列顺序都按照一定的规律)

四、选定触发器类型

求出状态方程,驱动方程,输出方程

五、画出逻辑图

六、检查自启动

将检查自启动提前,在化简状态表时,就将无效态的次态设为初态,无论输入是什么。

有限状态机(FSM)设计举例

例:设计一个串行数据检测器(密码锁),设计要求:连续输入3个或者3个以上的1时输出1,其他输入情况狂输出为0。

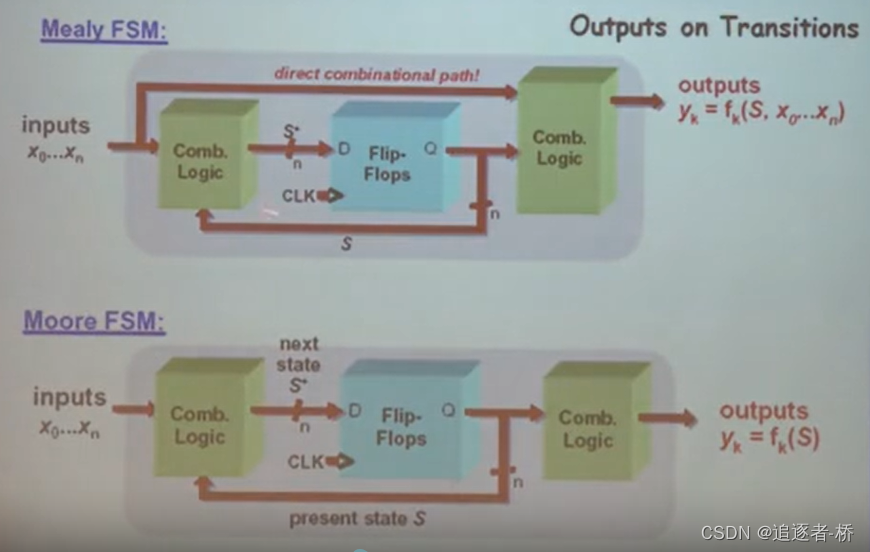

1、逻辑抽象——画出状态转换图(Mealy型电路)

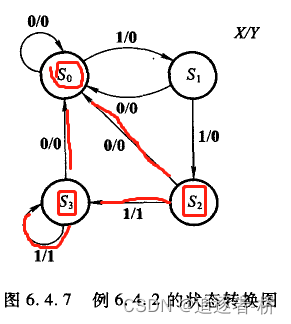

X表示输入,Y表示输出,没有输入的初始状态为S0,输入1个1后状态为S1,输入2个1后状态为S2,输入3个1后状态为S3。次态可以使用S*表示。状态转换图如下:

2、状态化简及分配

由于有4个状态编码时仅仅需要两位二进制码,此时不化简也没有问题,反而化简也不会出现一位二进制编码就可以实现,也无法省触发器。反而会带来化简麻烦,出现有效和无效的概念。但是为了熟悉步骤这里进行化简如下。

由上图可知S2当输入为0时输出为0,次态为S0;当输入为1时输出为1,次态为S3。

S3当输入为0时输出为0,次态为S0;当输入为1时输出为1,次态为S3。

根据当两个状态具有同样的输入时,具有相同的输出和相同的次态时,可以合并。

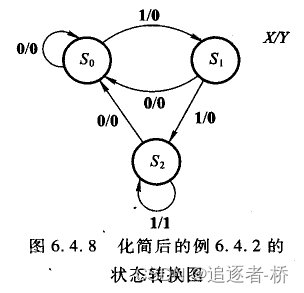

因此可以合并S2和S3,合并后如图所示:

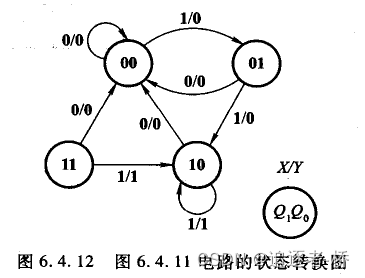

电路状态M=3,因此触发器的位数n=2。假设触发器状态Q1Q0的状态00、01、10分别代表S0、S1、S2。

3、选定触发器写出方程

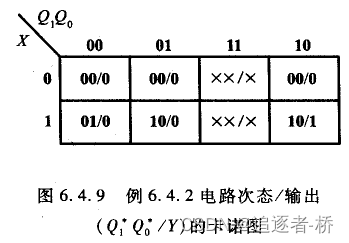

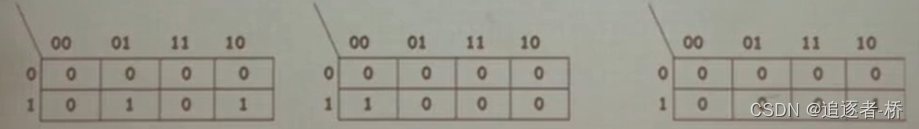

状态转换图不方便方程的书写,这里可以使用类卡诺图方式表示:

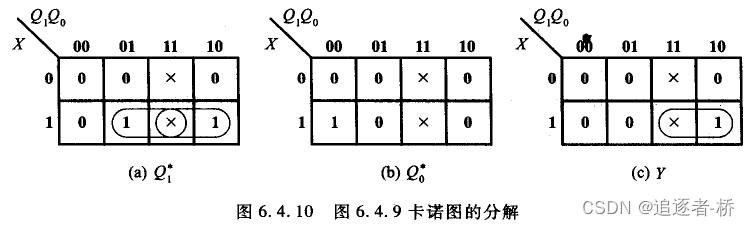

为方便写出Q1*、Q2*和Y的方程,这里可以分解称相应的卡诺图:

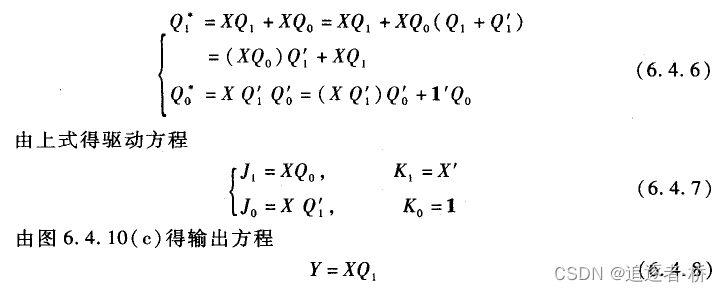

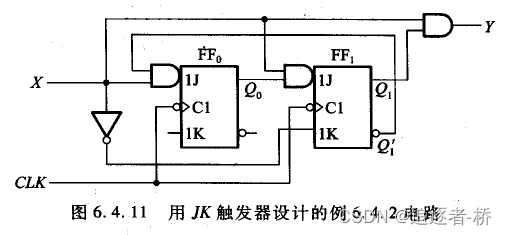

如果选择JK触发器组成电路,这里需要清楚的理解触发器的类型。

Q* = JQ'+JQ

本人关于触发器学习笔记链接,博客后期会更新

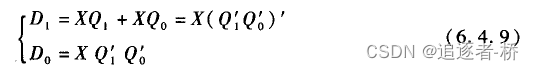

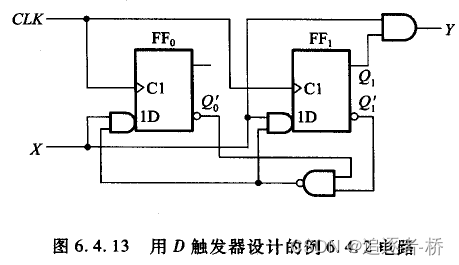

如果选择D触发器,则方程为:

4、画出逻辑图

5、检查自启动

当电路进入无效状态Q1Q0为11后,X=1则次态为10;若X=0此次态为00,因此可知电路为自启动的。

6.4.2 时序逻辑电路的自启动设计

当状态为11时,直接输入1则变换到最终态10,不合适。

这里直接将无效态的下一个状态(次态)设置称初态。

P36

最后

以上就是清秀小天鹅最近收集整理的关于《数字电子技术基础》6.4 时序逻辑电路——设计方法(FSM)有限状态机前言6.4.1 同步时序逻辑电路的设计方法6.4.2 时序逻辑电路的自启动设计的全部内容,更多相关《数字电子技术基础》6.4内容请搜索靠谱客的其他文章。

发表评论 取消回复