FPGA的实际开发中可以使用两种方法来进行逻辑设计,分别为:组合逻辑和时序逻辑。差异、缺点、有点、用途

一、组合逻辑与时序逻辑的对比

1、组合逻辑的输出与输入直接相关,时序逻辑的输出是由时钟的边沿触发的;

2、组合逻辑容易出现竞争、冒险问题,时序逻辑一般不会出现竞争、冒险现象;

3、组合逻辑的时序难以保证,时序逻辑更容易达到时序收敛、时序逻辑时序更可控;

4、组合逻辑只适合简单的电路,时序逻辑可以胜任大规模的逻辑电路。

二、组合逻辑的实现

方式一:

always @(电平敏感信号列表) begin

end

- 在always块中可以使用if…else等语句

- 组合逻辑一般建议使用阻塞赋值“=”

- always 块中的信号必须定义为reg型,但实际意义与wire型相同,这是语法中的规定,没有实际意义。

方式二:

用assign描述的赋值语句实现 - 信号只能定义为wire型

三、时序逻辑的实现

always @(posedge clk) begin

end

- 时序逻辑always 块定义的reg型信号都会被综合成register(寄存器);

- 时序逻辑一般推荐使用非阻塞赋值“<=”;

- 敏感列表中只要有时钟沿的变化即可,即每次触发输出变化都是时钟沿引入的。

- 在时序逻辑中只要出现在always@(posedge *)之后的就会被综合成系统时钟,

Example1:分别用组合逻辑和时序逻辑设计一个异或电路。

1、异或逻辑的真值表:

| a | b |a^b

| 0 | 0 |0

| 0 | 1 |1

| 1 | 0 |1

| 1 | 1 |0

(同为0,异为1)

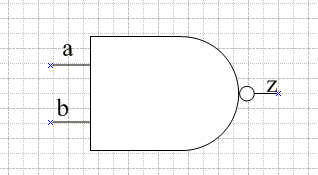

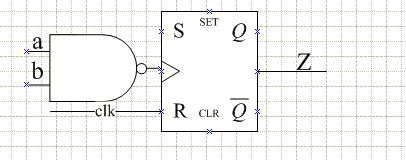

2、原理图:

图1-1 组合逻辑图 图1-2 时序逻辑图

从原理图可以看出,时序逻辑比组合逻辑多了一个触发器,触发器的输出变化发生的时钟clk的上升或下降沿。

3、verilog代码设计

组合逻辑代码设计:

module xor1(

input a,b,

output reg z

);

always @(a or b) begin

z = a^b;

end

(assign z = a^b;)

endmodule

时序逻辑代码设计:

module xor2(

input clk,

input rst_n,

input a,

input b,

output reg z

);

always @(poedge clk or negedge rst_n) begin//异步复位

if(!rst_n)

z <= 1’b0;

else

z <= a^b;

end

endmodule

4、仿真测试与时序分析

testbench:

module testbench_fifo();

//--------------------------------------------------------

//参数定义

//----------------------------------------------------------

`define CLK_PERIORD 10 //时钟周期设置为10ns(100MHz)

//-----------------------------------------------------------

//接口申明

//-----------------------------------------------------------

reg clk;

reg rst_n;

reg a;

reg b;

wire z1;

wire z2;

//----------------------------------------------------------

//对被测试的设计进行例化

//------------------------------------------------------------

xor1 uut_xor1(

.a(a),

.b(b),

.c(z1)

);

xor2 uut_xor2(

.clk(clk),

.rst_n(rst_n),

.a(a),

.b(b),

.c(z2)

);

//----------------------------------------------------------------

//复位和时钟产生

//---------------------------------------------------------------

//时钟和复位初始化、复位产生

initial begin

clk <= 0;

rst_n <= 0;

#1000;

rst_n <= 1;

end

//时钟产生

always #(`CLK_PERIORD/2) clk = ~clk;

//---------------------------------------------------------------

//测试激励产生

//--------------------------------------------------------------

initial begin

a <= 0;

b <= 0;

@(posedge rst_n); //等待复位完成

repeat(10) begin

@(posedge clk);

end

//a和b同步变化

@(posedge clk);

#2;

a <= 0;

b <= 1;

@(posedge clk);

#2;

a <= 1;

b <= 0;

@(posedge clk);

#2;

a <= 1;

b <= 1;

//a和b变化有延时

@(posedge clk);

#2;

a <= 0;

#1;

b <= 1;

@(posedge clk);

#2;

a <= 1;

#1;

b <= 0;

@(posedge clk);

#2;

a <= 1;

#1;

b <= 1;

@(posedge clk);

#2;

a <= 0;

#1;

b <= 0;

repeat(10) begin

@(posedge clk);

end

$stop;

end

endmodule

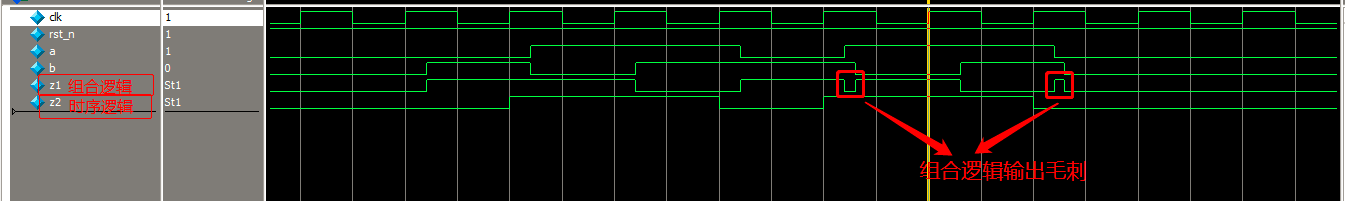

5、仿真波形图

由上图可以看出,时序逻辑的输出变化只发生在时钟的上升沿,而组合逻辑的输出变化是随着输入信号变化的,因此如果输入信号出现变化不同步的情况,就会导致图中的毛刺信号产生,因此在实际开发中如果使用组合逻辑需要考虑竞争、冒险的问题,会产生信号毛刺,影响功能。

最后

以上就是大方向日葵最近收集整理的关于组合逻辑与时序逻辑的全部内容,更多相关组合逻辑与时序逻辑内容请搜索靠谱客的其他文章。

发表评论 取消回复