7. 分频器设计(分频输出:1Hz或2Hz的信号)

要求:实验开发板上有一个50MHz的时钟脉冲(此频率过高,接到开发板的LED灯后,无法观察到LED灯一 亮一灭的过程),设计一个分频器,使得分频后的时钟脉冲接到开发板上的LED灯后,肉眼可以观察到LED灯 闪烁。

8. 设计一个十进制加法计数器

使用设计的分频器的输出信号作为计数器的时钟输入,再利用第二次实验中设计的七段显示译码器显示 计数值。

9. 巴克码发生器设计和巴克码检测器设计。

实验任务一:分频器设计

【实验代码】

library ieee;

use ieee.std_logic_1164.all;

entity shiyan7 is

port (

clkin:in std_logic;

clkout:out std_logic);

end shiyan7;

architecture behave of shiyan7 is

signal data:integer range 0 to 10000;

signal i:integer range 0 to 5000;

signal Q:std_logic;

begin

process(clkin)

begin

if rising_edge(clkin)then

if(data=10000)then

data<=0;

Q<=NOT Q;

else

if(i=2000)then

i<=0;

data<=data+1;

else i<=i+1;

end if;

end if;

end if;

clkout<=Q;

end process;

end behave;

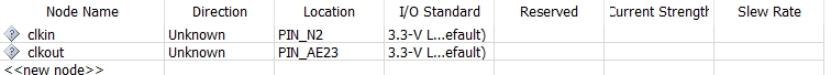

【引脚配置】

实验任务二:十进制计数器设计

【实验代码】

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity ex9 is

port(

reset:in std_logic;

clk:in bit;

dout2:out bit;

dout1:out std_logic_vector(6 downto 0));

end ex9;

architecture behave of ex9 is

signal count7:integer range 0 to 6;

signal clk1:bit;

begin

process(clk)

variable c:integer range 0 to 50000000;

begin

if(clk'event and clk='1') then

c:=c+1;

if(c<25000000)then clk1<='1';

else clk1<='0';

end if;

end if;

end process;

process(clk1,reset)

begin

if reset='1' then count7<=0;

elsif clk1'event and clk1='1' then

if count7<6 then

count7<=count7+1;

else count7<=0;

end if;

end if;

dout2<=clk1;

end process;

process(count7)

begin

case count7 is

when 0=>dout1<="1000000";

when 1=>dout1<="1100000";

when 2=>dout1<="1110000";

when 3=>dout1<="1110000";

when 4=>dout1<="1110000";

when 5=>dout1<="1110010";

when 6=>dout1<="1110010";

when others=>null;

end case;

end process;

end behave;

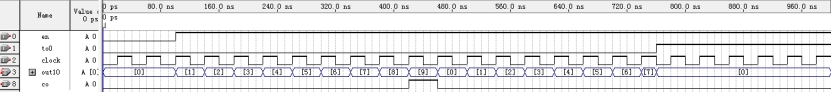

【仿真波形】

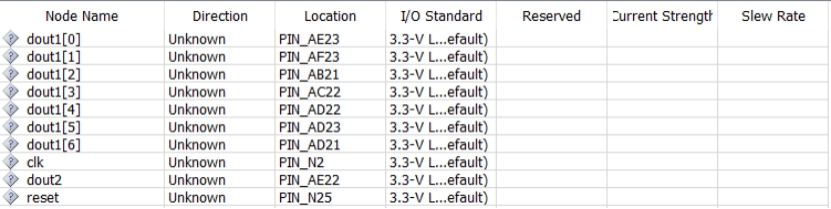

【引脚配置】

实验任务三:巴克码发生器和检测器

【实验代码】

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity barkker_2 is

port(clk:in std_logic;

bark:out std_logic_vector(6 downto 0);

tap_out:out std_logic);

end entity;

architecture behave of barkker_2 is

component barkker

port(clk_in:in std_logic;out:out std_logic_vector(3 downto 0);tap:out std_logic);

end component;

component led_7

port( b: in std_logic_vector(3 downto 0);led: out std_logic_vector(6 downto 0));

end component;

signal i:std_logic_vector(3 downto 0);

begin

u1:barkker port map (clk,i,tap_out);

u2:led_7 port map(i,bark);

end behave;

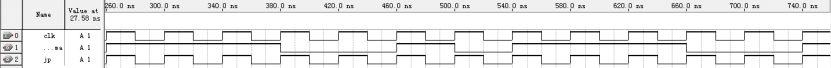

【仿真波形】

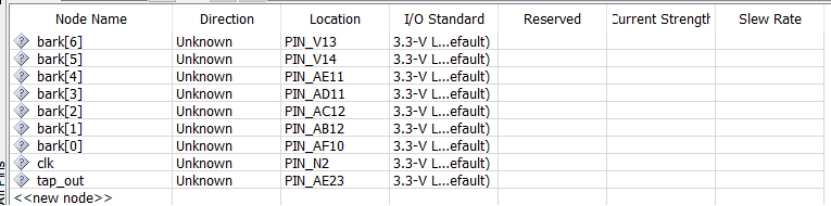

【引脚配置】

最后

以上就是自信电话最近收集整理的关于EDA第三次实验(VHDL)--时序电路设计的全部内容,更多相关EDA第三次实验(VHDL)--时序电路设计内容请搜索靠谱客的其他文章。

发表评论 取消回复