一、实验步骤与实验结果

第一步:创建一个工程项目。首先实现连续节拍脉冲发生器电路。

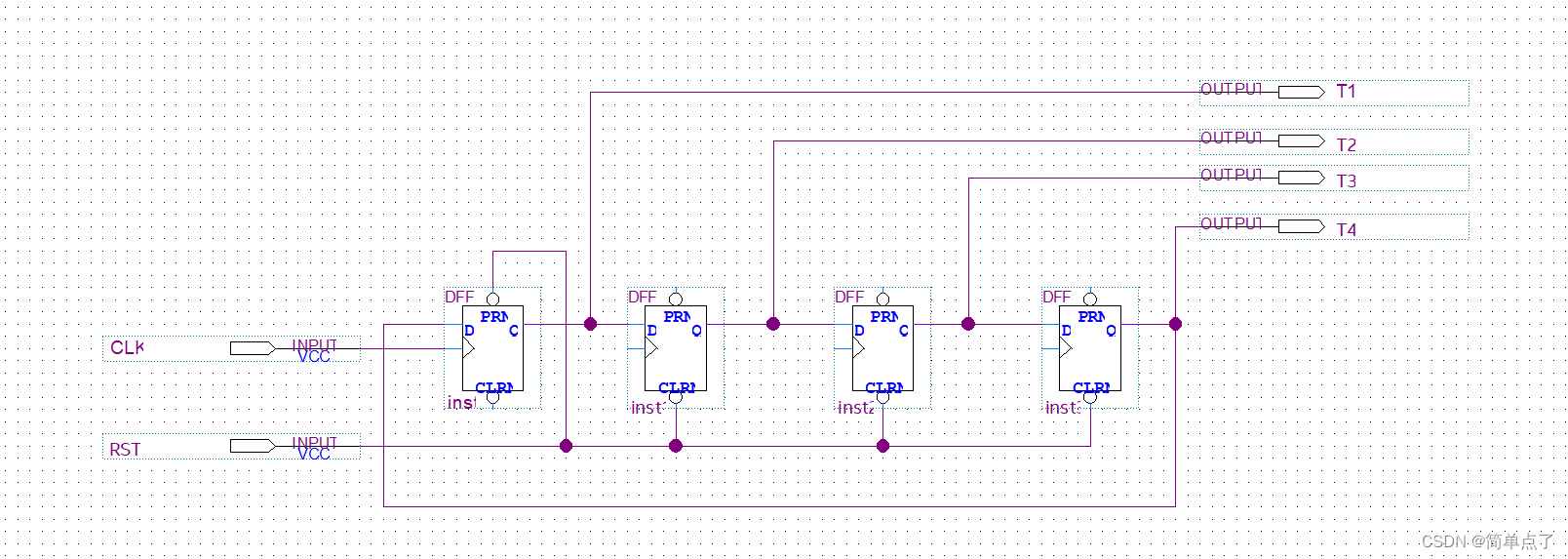

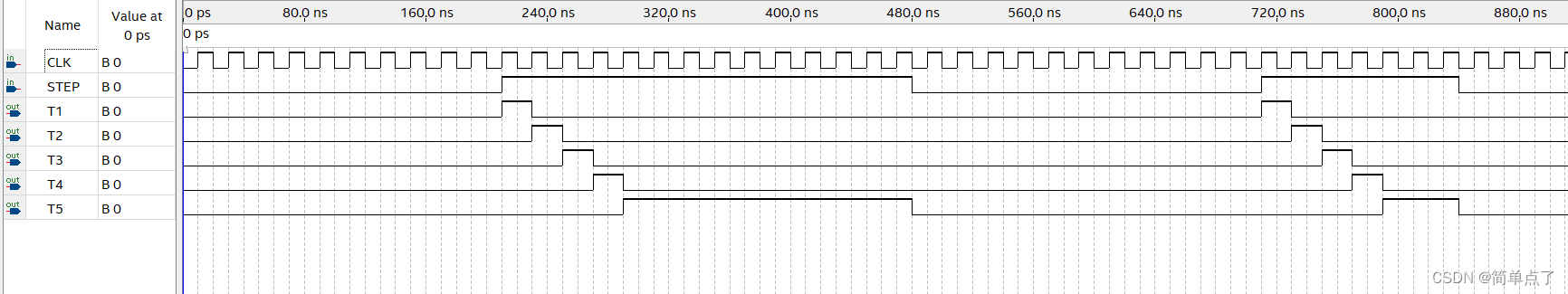

电路图如下:

图1.1 连续节拍脉冲发生器电路

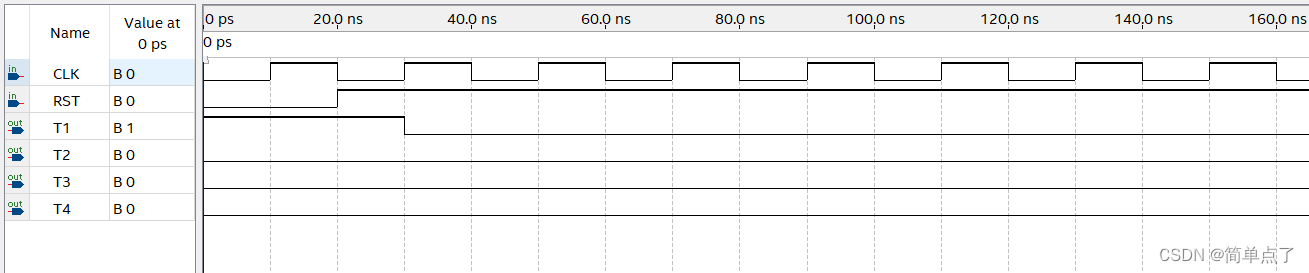

仿真图如下:

图1.2 节拍脉冲发生器工作波形

分析此仿真图:当RST复位端给低电平,不论什么时钟信号,T1恒为高电平,T2,T3,T4恒低电平;当RST复位端给高电平,此时T1为高电平,T2,T3,T4低电平,当遇到CLK时钟信号为上升沿的时候,实现节拍的循环。

第二步:接下来实现单步节拍发生电路设计。

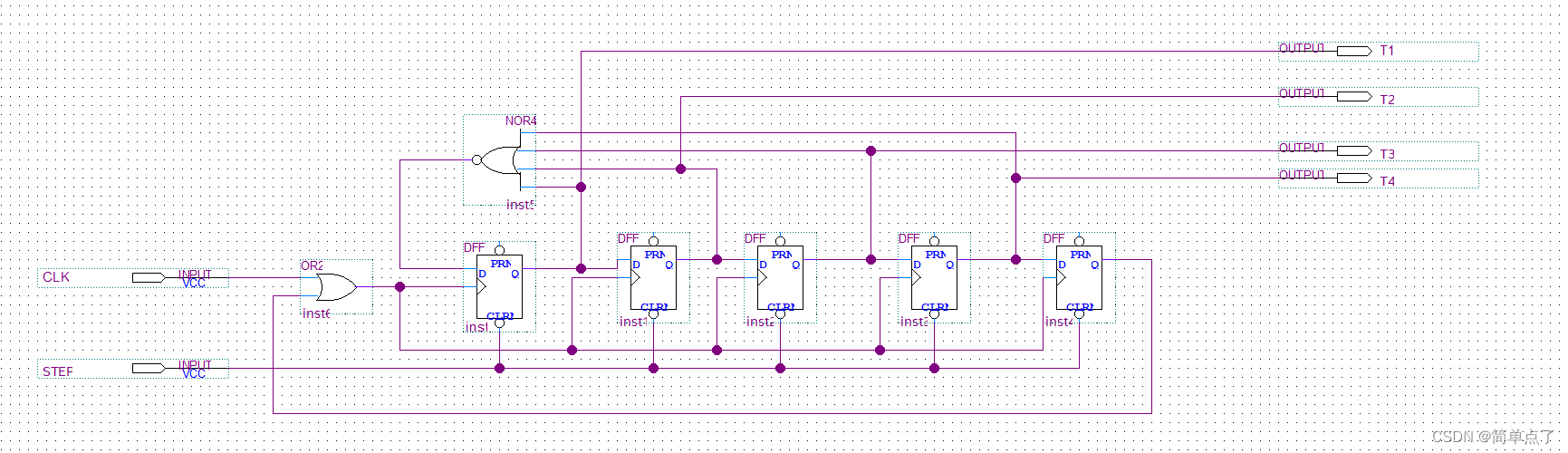

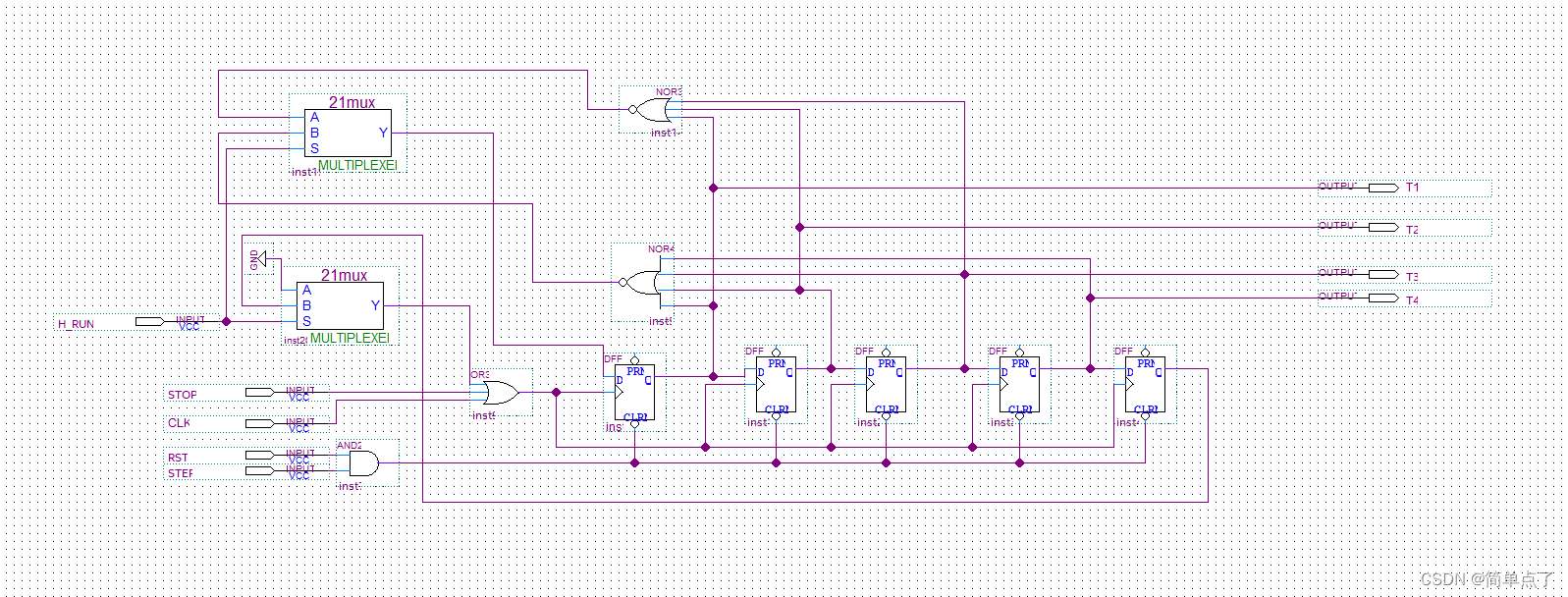

电路图如下:

图1.3 单步节拍发生电路

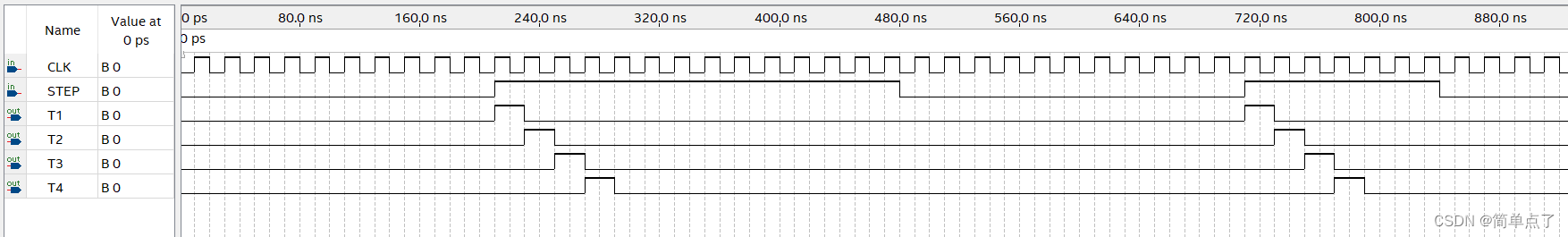

图1.4 单步节拍脉冲发生器工作波形

仿真分析:当SETP置0的时候T1、T2、T3、T4节拍信号恒为0。只有当SETP置1的时候,CLK为上升沿,逐步输出T1=1,T2=1,T3=1,T4=1,最后当T5=1的时候,CLK|T5恒为1,时钟就不起作用了。见下图可以更好的理解。

图1.5 单步节拍发生电路仿真图

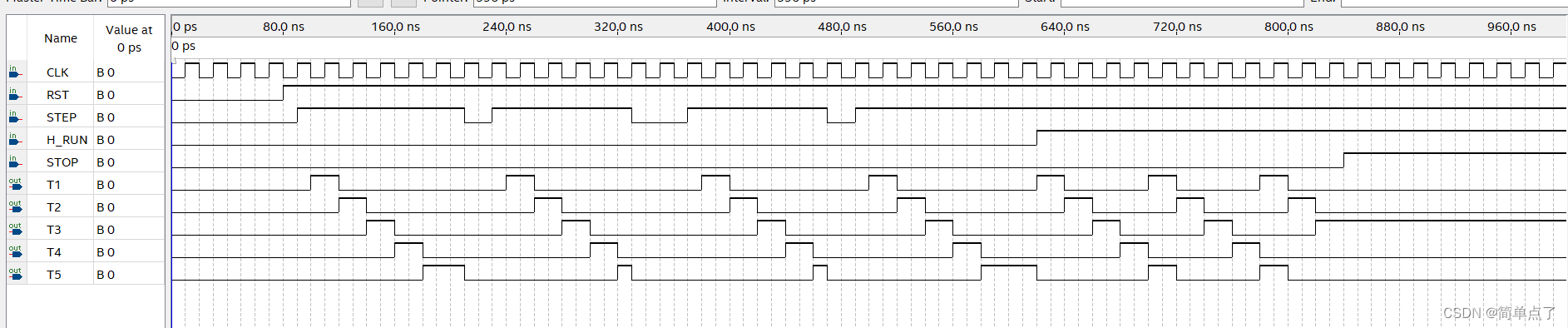

第三步:设计单步/连续节拍发生电路。

电路图如下:

图1.6 单步/连续节拍发生器电路

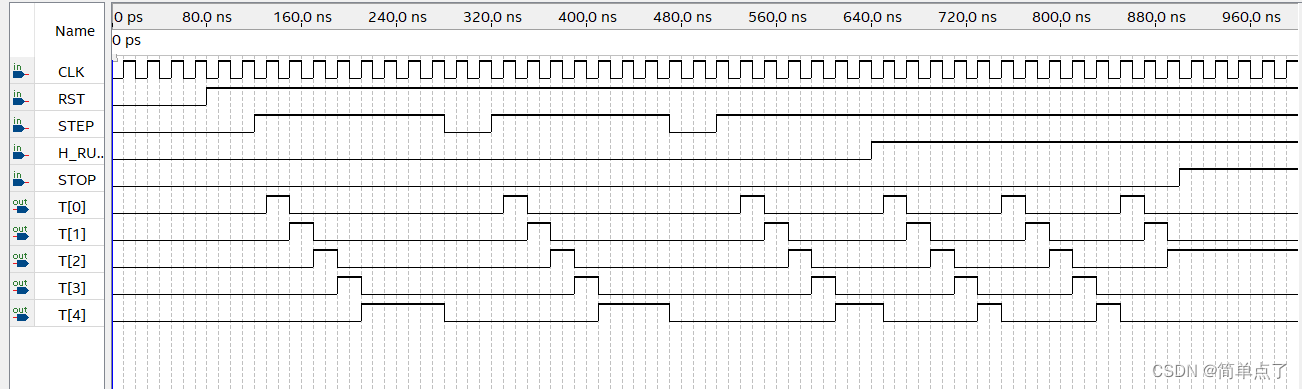

仿真图如下:

图1.7 单步/连续节拍电路运行仿真波形

仿真图分析如下:当RST为0时,T1-T5均输出0,是复位键。当RST为1时,STEP为0和RST的作用是相似的,当STEP和RST均为1的时候开始执行单步或连续节拍发生器,此时H_RUN是选择是单步还是连续节拍的选择位,当H_RUN为0说明是单步节拍发生器,当H_RUN为1说明是连续节拍发生器,当STOP端为1时起到停止电路的作用。

二、实验讨论与总结

1、单步运行与连续运行有何区别,它们各自的使用环境怎样?

解答:区别:单步运行只在复位后T1-T4依次产生一个脉冲,对应与计算机中执行一条指令,而连续运行复位后T1-T4将依次产生脉冲不断循环下去。使用环境:单步运行用于调试器对单步指令运行的控制,连续运行用于程序的正常运行和连续运行控制连续指令执行。

2、如何实现单步/连续运行工作方式的切换?

解答:通过S控制21MUX的2选1控制端。当S为低电平时,Y=A,即实现了连续方式;当S为高电平时,Y=B,即切换到单步方式。

3、用Verilog HDL设计实现节拍控制电路,并通过实验台验证其功能。

解答:代码详见实验报告底部附件一:程序源代码

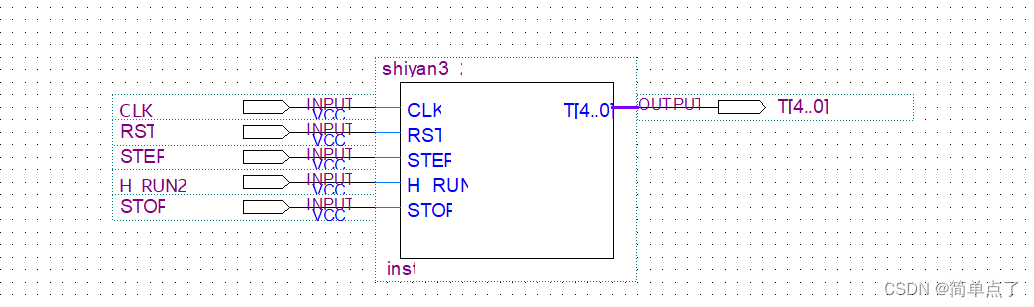

该程序的电路图如下:

图2.1 verilog实现的单步/连续节拍电路

该程序的仿真图如下:

图2.2 verilog实现的单步/连续节拍电路运行仿真波形

附件一:程序源代码

1、用Verilog HDL设计实现节拍控制电路代码清单如下:

module shiyan3_2 ( CLK,RST,STEP,H_RUN,STOP,T);

input CLK,RST,STEP,H_RUN,STOP;

output [4:0]T;

reg [4:0]T;

//临时变量

reg [4:0]t1=5'b00000;

//reg t[3:0];

always @ (posedge CLK or negedge RST or negedge STEP )

begin

if(!RST)

begin

T<=5'b0000;

t1<=5'b0000;

end

else if(!STEP)

begin

T<=5'b0000;

t1<=5'b0000;

end

//保持状态不变

else if(STOP)

begin

T<=T;

t1<=T;

end

else

begin

if(!H_RUN)

begin

//单脉冲

case(t1)

5'b00000:begin t1<=5'b00001; T<=5'b00001; end

5'b00001:begin t1<=5'b00010; T<=5'b00010; end

5'b00010:begin t1<=5'b00100; T<=5'b00100; end

5'b00100:begin t1<=5'b01000; T<=5'b01000; end

5'b01000:begin t1<=5'b10000; T<=5'b10000; end

//其余输出

default:begin t1<=5'b10000; T<=5'b10000; end

endcase

end

else

begin

//连续脉冲

case(t1)

5'b00000:begin t1<=5'b00001; T<=5'b00001; end

5'b00001:begin t1<=5'b00010; T<=5'b00010; end

5'b00010:begin t1<=5'b00100; T<=5'b00100; end

5'b00100:begin t1<=5'b01000; T<=5'b01000; end

5'b01000:begin t1<=5'b10000; T<=5'b10000; end

5'b10000:begin t1<=5'b00001; T<=5'b00001; end

//其余输出

default:begin t1<=5'b00000; T<=5'b00000 ;end

endcase

end

end

end

endmodule最后

以上就是称心小馒头最近收集整理的关于实验三 时序电路实验的全部内容,更多相关实验三内容请搜索靠谱客的其他文章。

发表评论 取消回复