文章目录

- 一、计数器

- 1. 计数器概念和分类

- 2. 双时钟可逆十六进制计数器74LS193

- (1) 74LS193的引脚示意图和逻辑功能图

- (2) 74LS193 的逻辑功能表

- 3. 用集成计数器实现任意进制计数

- (1) 反馈清零法和反馈置数法 (M < N)

- a. 反馈清零法

- b. 反馈置数法

- (2) 多个芯片级联(M>N)

- a. 分解法

- b. 扩展法

- 二、寄存器

- 1. 寄存器概念和分类

- 2. 基本寄存器结构和功能

- 3. 集成的基本寄存器

- (1) 由多个边沿D触发器组成的集成寄存器

- (2) 具有输入使能功能的锁存型寄存器

- (3) 具有输出缓冲功能的寄存器

- 4. 移位寄存器

- (1) 单向移位寄存器

- (2) 双向移位寄存器

- (3) 4位双向移位寄存器74LS194

- (4) 移位寄存器的应用——实现数码串/并转换

- 三、多谐震荡电路(补充)

- 1. 多谐振荡器

- 2. 555定时器

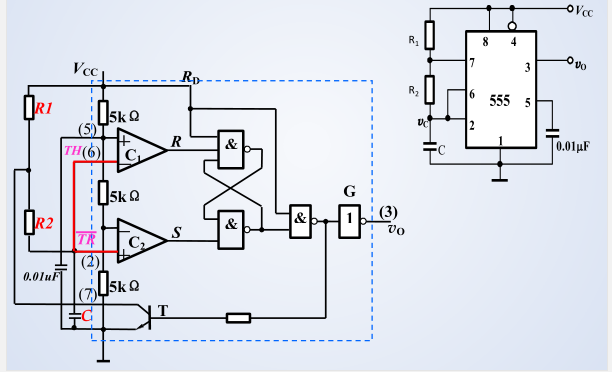

- (1) 电路结构

- (2) 工作原理

- (3) 工作原理

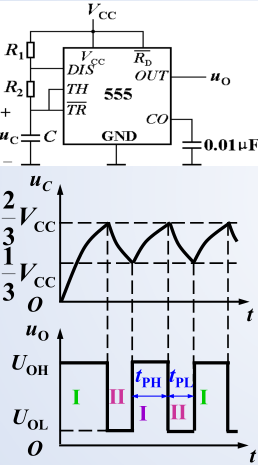

- 3. 用555定时器构成多谐振荡器

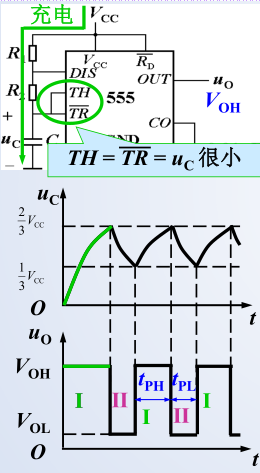

- (1) 电路结构

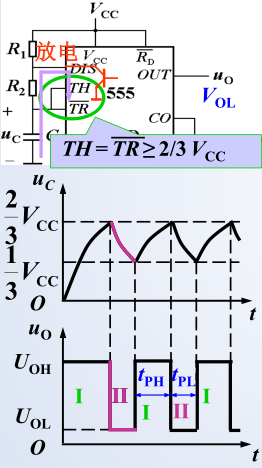

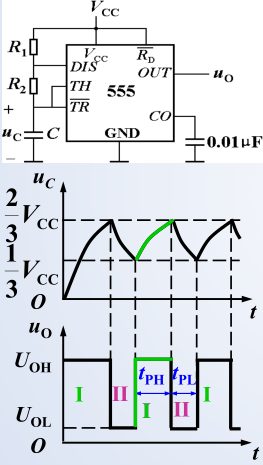

- (2) 工作原理

- (3) 振荡频率计算

一、计数器

1. 计数器概念和分类

计数: 累计输入脉冲的个数构成:

- 1 1 1 个触发器有 2 2 2 个状态,可计 2 2 2 个数( 1 1 1 位二进制数)

- n n n 个触发器有 2 n 2^n 2n 个状态,可计 2 n 2^n 2n 个数( n n n 位二进制数)

应用:分频、定时、产生节拍脉冲和脉冲序列、进行数字运算等.

分类如下:

按数制分:

- 二进制计数器

- 十进制计数器

- N N N 进制(任意进制)

计数器按计数方式分:

- 加法计数器

- 减法计数器

- 可逆计数 (

Up-Down Counter,既能够做加法也能够做减法)

按时钟控制分:

- 同步计数器 (

Synchronous) - 异步计数器 (

Asynchronous)

我们的重点在于同步集成计数器。同步计数器的特点:在同步计数器内部, 各个触发器都受同一时钟脉冲——输入计数脉冲(计数就是统计累计输入脉冲的个数)的控制, 因此, 它们状态的更新几乎是同时的, 故被称为 “同步计数器”。

下面就将介绍常用的同步计数器。

2. 双时钟可逆十六进制计数器74LS193

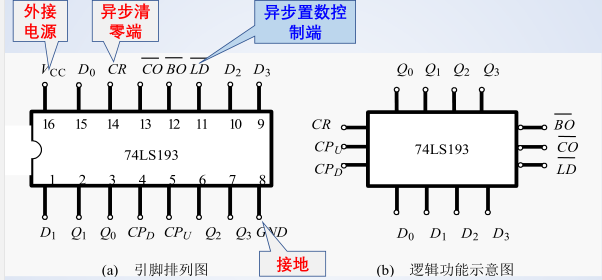

(1) 74LS193的引脚示意图和逻辑功能图

双时钟是指存在两个时钟信号,可逆指的是既可以做加法计数,也可以做减法计数。

为了使用74LS193,我们必须掌握其引脚的功能:

Vcc:外接电源;GND:接地;- C P D CP_D CPD :减法(down)脉冲输入信号;

- C P U CP_U CPU :加法(up)脉冲输入信号;

- C O ‾ overline {CO} CO :进位输出端,carry output,多个74LS193级联的时候有用处;

- B O ‾ overline {BO} BO :借位输出端,borrow output,多个74LS193级联的时候有用处;

- D 3 D 2 D 1 D 0 D_3D_2D_1D_0 D3D2D1D0 :外部输入数据,用于异步置数;

- Q 3 Q 2 Q 1 Q 0 Q_3Q_2Q_1Q_0 Q3Q2Q1Q0 :计数器输出数据;

- C R CR CR :异步清零端;

- L D ‾ overline {LD} LD :异步置数控制端;

(2) 74LS193 的逻辑功能表

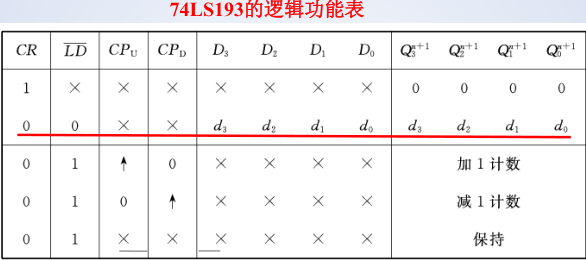

- C R = 1 CR=1 CR=1 时,异步清零,计数器输出数据 Q 3 Q 2 Q 1 Q 0 Q_3Q_2Q_1Q_0 Q3Q2Q1Q0 为 0000 0000 0000;

- C R = 0 , L D ‾ = 0 CR=0,overline {LD}=0 CR=0,LD=0时,异步置数 Q 3 Q 2 Q 1 Q 0 Q_3Q_2Q_1Q_0 Q3Q2Q1Q0 为 D 3 D 2 D 1 D 0 D_3D_2D_1D_0 D3D2D1D0 ;

-

C

R

=

0

,

L

D

‾

=

1

CR=0,overline {LD}=1

CR=0,LD=1,既不清零也不置数,此时如果

C

P

U

↑

CP_{U} uparrow

CPU↑ 且

C

P

D

=

0

CP_D = 0

CPD=0 时,加

1

1

1 计数;当加法计数到达

1111时,进位输出 C O ‾ overline {CO} CO 输出一个脉宽等于 C P U CP_{U} CPU 的低电平部分的低电平脉冲;当下一个 C P U CP_{U} CPU 上升沿到来时, C O ‾ overline {CO} CO 变为高电平,由此产生一个 C O ‾ overline {CO} CO 的上升沿;多个74LS193级联时,正好将低位的 C O ‾ overline {CO} CO 端与高位的 C P U CP_{U} CPU 端连接起来; -

C

R

=

0

,

L

D

‾

=

1

CR=0,overline {LD}=1

CR=0,LD=1,既不清零也不置数,此时如果

C

P

D

↑

CP_D uparrow

CPD↑ 且

C

P

U

=

0

CP_U = 0

CPU=0 时,减

1

1

1 计数;当减法计数到达

0000时,借位输出 B O ‾ overline {BO} BO 输出一个脉宽等于 C P U CP_{U} CPU 的低电平部分的低电平脉冲;当下一个 C P D CP_{D} CPD 上升沿到来时, B O ‾ overline {BO} BO 变为高电平,由此产生一个 B O ‾ overline {BO} BO 的上升沿;多个74LS193级联时,正好将低位的 B O ‾ overline {BO} BO 端与高位的 C P D CP_{D} CPD 端连接起来; - C R = 0 , L D ‾ = 1 CR=0,overline {LD}=1 CR=0,LD=1,且 C P D , C P U CP_D,CP_U CPD,CPU 均无变化时,状态保持。

3. 用集成计数器实现任意进制计数

若已有 N N N 进制计数器,现在要实现 M M M 进制计数器:

M < N:反馈清零法或反馈置数法M > N:多个芯片级联

(1) 反馈清零法和反馈置数法 (M < N)

在

N

N

N 进制计数器的顺序计数过程中, 若设法使之跳过

N

−

M

N - M

N−M 个状态 , 就可以得

到

M

M

M 进制计数器 , 其方法有清零法(复位法)和置数法(置位法)。注意,两种方法的使用是有条件的。

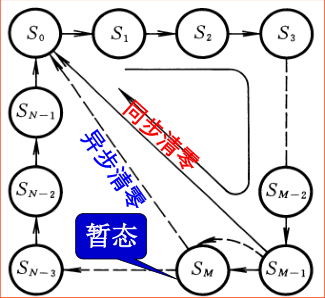

a. 反馈清零法

清零法 适用于有清零输入端(异步 或 同步)的计数器。例如74LS193。

异步清零法和同步清零法存在一些差异,但基本思想都是:计数器从全

0

0

0 状态

S

0

S_0

S0 开始计数,计满

M

M

M 个状态后产生清零信号,使计数器恢复到初态

S

0

S_0

S0 ,然后再重复上述过程。

反馈清零法-异步清零:

S

M

S_M

SM 状态进行译码产生置零信号并反馈到异步清零端,74LS193中是

C

R

CR

CR ,使计数器立即返回

S

0

S_0

S0 状态。

S

M

S_M

SM 状态只在极短的瞬间出现,通常称它为“暂态”。

步骤:

(1) 写出状态

S

M

S_M

SM 的二进制代码;

(2) 求归零逻辑:

S

M

S_M

SM 中所有

1

1

1 对应的端口求与(异步清0端高电平有效)或者是求与-非(低电平有效);

(1) 画出电路连线图。

反馈清零法-同步清零:当计数器处于

S

M

−

1

S_{M-1}

SM−1 状态时,产生同步清零信号,在下一个时钟脉冲使芯片转换到零状态。

步骤:

(1) 写出状态

S

M

−

1

S_{M-1}

SM−1 的二进制代码;

(2) 求归零逻辑:

S

M

−

1

S_{M-1}

SM−1 中所有

1

1

1 对应的端口求与(同步清0端高电平有效)或者是求与-非(低电平有效);

(3) 画出电路连线图

例. 用74LS193构成一个十二进制计数器。

答:74LS193是十六进制计数器,要构成十二进制计数器,可采用反馈清零法。利用异步清零端即可。

步骤:

(1) 写出S M 的二进制编码:

S

M

=

S

12

=

1100

S_M = S_{12} =1100

SM=S12=1100

(2) 求归零逻辑:

C

R

=

Q

3

n

Q

2

n

CR = Q^n_3Q^n_2

CR=Q3nQ2n

(3) 画出电路图:

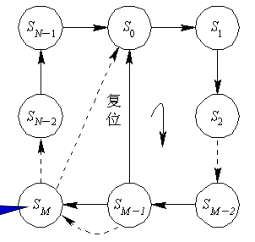

b. 反馈置数法

清

0

0

0 法中,计数器每次都是从全

0

0

0 状态

S

0

S_0

S0 开始计数;

置数法可以通过预置功能使计数器从某个预置状态

S

i

S_i

Si 开始计数, 计满

M

M

M 个状态后产生置数信号,使计数器又进入预置状态

S

i

S_i

Si , 然后再重复上述过程。

反馈置数法-异步置数:在暂态

S

i

+

M

S_{i+M}

Si+M 产生置数信号,并马上将预置数——

i

i

i 的二进制代码,通过异步置数端置于计数器;适合74LS193;

反馈置数法-同步置数:在状态

S

i

+

M

−

1

S_{i+M-1}

Si+M−1 产生置数信号,要等下一个 CP 到来时,才将预置数置入计数器,故无暂态。置数完成后,计数器从被置入的状态重新开始计数。

例. 采用反馈置数法,用74LS193构成一个十进制计数器。

分析:74LS193是异步置数计数器,共有16个状态,要构成十进制计数器,可从中选取10个连续的状态。选定十个状态

Q

3

Q

2

Q

1

Q

0

Q_3 Q_2 Q_1 Q_0

Q3Q2Q1Q0 为:

0011

→

1100

0011→1100

0011→1100 。

- 写出反馈态 S i + M S_{i+M} Si+M 的二进制代码, 即 S i + M = 1101 S_{i+M} =1101 Si+M=1101;

- 求置数逻辑: L D ‾ = Q 3 Q 2 Q 0 ‾ overline {LD} = overline {Q_3 Q_2 Q_0} LD=Q3Q2Q0;

- 预置态

S

i

=

0011

S_i =0011

Si=0011, 画出电路图:

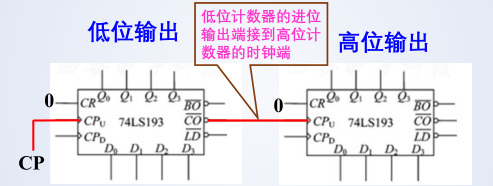

(2) 多个芯片级联(M>N)

若要求实现的计数器计数值 M M M 超过单片计数器的计数范围, 则必须将多片计数器级联。

a. 分解法

若

M

M

M 可分解为

M

=

M

1

×

M

2

×

…

M

n

M = M_1 × M_2 × … M_n

M=M1×M2×…Mn , 则用

n

n

n 片计数器分别组

成

M

1

M_1

M1,

M

2

M_2

M2 …

M

n

M_n

Mn 进制计数器 , 然后再将它们 级联 而成。

级联方法:

- 并行进位法:所有芯片共用一个时钟信号,低位芯片的进位输出控制相邻高位芯片的使能端(同步方式);

- 串行进位法:低位芯片的进位输出作为相邻高位芯片的

CP(异步方式);适合74LS193.

b. 扩展法

先将 n n n 片计数器 级联 组成最大计数值 N > M N>M N>M的计数器 , 然后采用 整体清0 或 整体置数 的方法实现模 M M M 计数器 。

例. 用74LS193设计一个

256

256

256 进制的计数器。

分析:74LS193是

16

16

16 进制计数器,两片74LS193级联可以实现

256

256

256 进制计数器。

当低位计数器计数为

1111

1111

1111 时,低位计数器的进位输出端产生一个低电平脉冲信号;当下一个时钟脉冲上升沿到来时,低位计数器的进位输出端变为高电平值,相当于高位计数器的时钟端有一个上升沿,高位计数器计数增加

1

1

1 。

二、寄存器

1. 寄存器概念和分类

和计数器一样,寄存器也是时序逻辑电路的最常见的应用之一。

寄存:把二进制数据或代码暂时存储;

功能特点:暂存数据或代码,一般不对存储内容进行处理;

结构特点:通常由

D

D

D 触发器构成;

分类:

- 基本寄存器(数码寄存器)

- 移位寄存器

输入输出方式:

- 并行方式:每一位数据对应一个输入端/输出端,在 C P CP CP 作用下,各位同时输入/输出;

- 串行方式:只有一个输入端/输出端, C P CP CP 作用下,各数码逐位输入/输出。

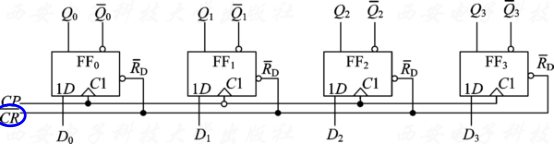

2. 基本寄存器结构和功能

右图是具有异步清零端的基本寄存器。

功能说明:

- 当 C R ‾ = 0 overline {CR} = 0 CR=0 时,寄存器清零: Q 3 n + 1 Q 2 n + 1 Q 1 n + 1 Q 0 n + 1 = 0000 Q^{n+1}_3Q^{n+1}_2Q^{n+1}_1Q^{n+1}_0 = 0000 Q3n+1Q2n+1Q1n+1Q0n+1=0000;

- 当

C

R

‾

=

1

overline {CR} = 1

CR=1 时,时钟脉冲

CP上升沿到来,寄存器置数。加在并行数据输入端的数据 D 3 D_3 D3 ~ D 0 D_0 D0 ,就立即被送到触发器输出端, Q 3 n + 1 Q 2 n + 1 Q 1 n + 1 Q 0 n + 1 = D 3 D 2 D 1 D 0 Q^{n+1}_3Q^{n+1}_2Q^{n+1}_1Q^{n+1}_0 = D_3D_2D_1D_0 Q3n+1Q2n+1Q1n+1Q0n+1=D3D2D1D0 ; - 当 C R ‾ = 1 overline {CR} = 1 CR=1 时,除了时钟上升沿之外的其他时间,寄存器的状态保持不变。

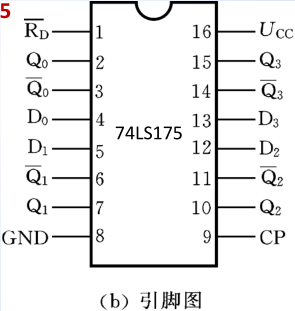

3. 集成的基本寄存器

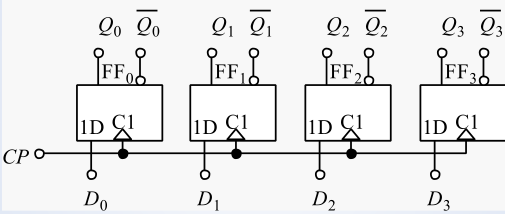

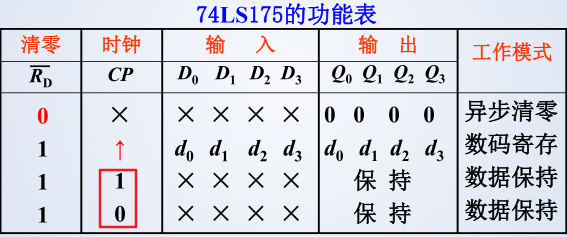

(1) 由多个边沿D触发器组成的集成寄存器

下图是

4

4

4 位上升沿集成触发器74LS175:

引脚说明:

- D 0 D_0 D0~ D 3 D_3 D3 :并行数据输入端

- Q 0 Q_0 Q0~ Q 3 Q_3 Q3 :并行数据输出端

- R D ‾ overline {R_D} RD :异步清零控制端

74LS175集成触发器,上升沿时送数,异步清零:

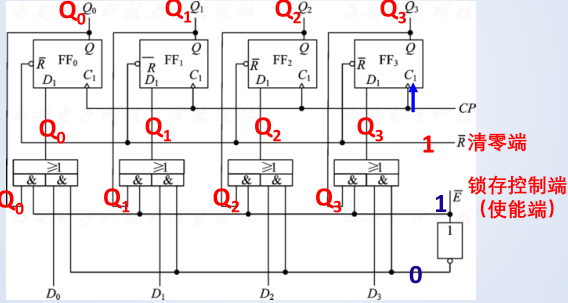

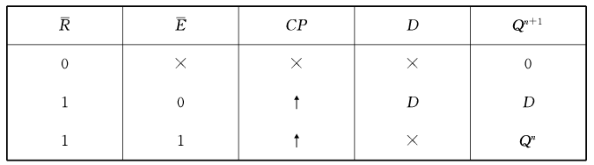

(2) 具有输入使能功能的锁存型寄存器

上图的集成寄存器在时钟上升沿锁存数据,其他时间保存数据;可以异步清零,可以使能。功能表如下:

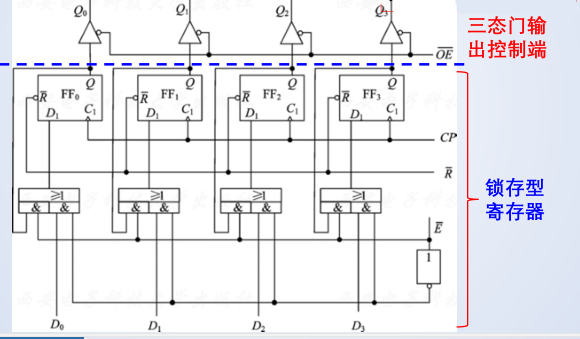

(3) 具有输出缓冲功能的寄存器

当 O E ‾ = 0 overline {OE}=0 OE=0 时,锁存在触发器的数据才会传到输出端。

4. 移位寄存器

移位: 将寄存器所存储的各位数据,在每个移位脉冲的作用下, 向左或向右移动一位。根据移位的方向,分成:左移、右移和双向移位。

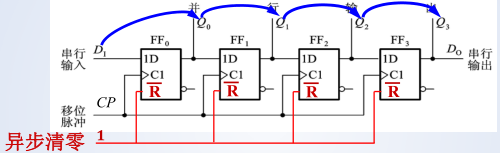

(1) 单向移位寄存器

- D I D_I DI :串行数据输入端;

- D O D_O DO :串行数据输出端;

- C P CP CP :时钟端;

- Q 0 Q_0 Q0 ~ Q 3 Q_3 Q3 :并行数据输出端;

- R ‾ overline R R :异步清零端

触发器的驱动方程:

D

0

=

D

I

,

D

1

=

Q

0

n

,

D

2

=

Q

1

n

,

D

3

=

Q

2

n

D_0=D_I,D_1 =Q_0^n,D_2 =Q_1^n,D_3 =Q_2^n

D0=DI,D1=Q0n,D2=Q1n,D3=Q2n;

代入

D

D

D 触发器的特征方程:

Q

n

+

1

=

D

Q^{n+1} = D

Qn+1=D ;

得到:

Q

0

n

+

1

=

D

I

,

Q

1

n

+

1

=

Q

0

n

,

Q

2

n

+

1

=

Q

1

n

,

Q

3

n

+

1

=

Q

2

n

Q_0^{n+1} =D_I,Q_1 ^{n+1} =Q_0^n,Q_2^{n+1} =Q_1^{n} ,Q_3^{n+1} =Q_2^n

Q0n+1=DI,Q1n+1=Q0n,Q2n+1=Q1n,Q3n+1=Q2n

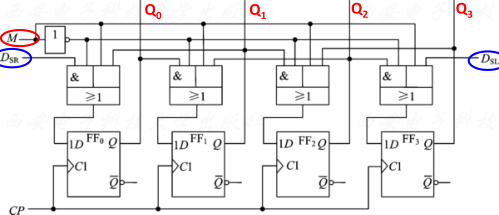

(2) 双向移位寄存器

- 移位控制端: M M M

- 左移串行输入端: D S L D_{SL} DSL

- 右移串行输入端: D S R D_{SR} DSR

次态方程:

{

Q

0

n

+

1

=

M

‾

D

S

R

+

M

Q

1

n

Q

1

n

+

1

=

M

‾

Q

0

n

+

M

Q

2

n

Q

2

n

+

1

=

M

‾

Q

1

n

+

M

Q

3

n

Q

3

n

+

1

=

M

‾

Q

2

n

+

M

D

S

L

left { begin{aligned} &Q^{n+1}_0 = overline {M}D_{SR} + MQ^n_1\ &Q^{n+1}_1 = overline MQ^n_0 + MQ^n_2\ &Q^{n+1}_2 = overline MQ^n_1 + MQ^n_3\ &Q^{n+1}_3 = overline MQ^n_2 + MD_{SL} end{aligned} right.

⎩⎪⎪⎪⎪⎨⎪⎪⎪⎪⎧Q0n+1=MDSR+MQ1nQ1n+1=MQ0n+MQ2nQ2n+1=MQ1n+MQ3nQ3n+1=MQ2n+MDSL

M

=

0

M=0

M=0 时,右移,

Q

0

n

+

1

=

D

S

R

,

Q

1

n

+

1

=

Q

0

n

,

Q

2

n

+

1

=

Q

1

n

,

Q

3

n

+

1

=

Q

2

n

Q_0^{n+1} = D_{SR},Q_1 ^{n+1} =Q_0^n,Q_2^{n+1} =Q_1^{n} ,Q_3^{n+1} =Q_2^n

Q0n+1=DSR,Q1n+1=Q0n,Q2n+1=Q1n,Q3n+1=Q2n;

M

=

1

M=1

M=1 时,左移,

Q

0

n

+

1

=

Q

1

n

,

Q

1

n

+

1

=

Q

2

n

,

Q

2

n

+

1

=

Q

3

n

,

Q

3

n

+

1

=

D

S

L

Q_0^{n+1} = Q^{n}_1,Q_1^{n+1} = Q_2^n,Q_2^{n+1} =Q_3^n,Q_3^{n+1} = D_{SL}

Q0n+1=Q1n,Q1n+1=Q2n,Q2n+1=Q3n,Q3n+1=DSL;

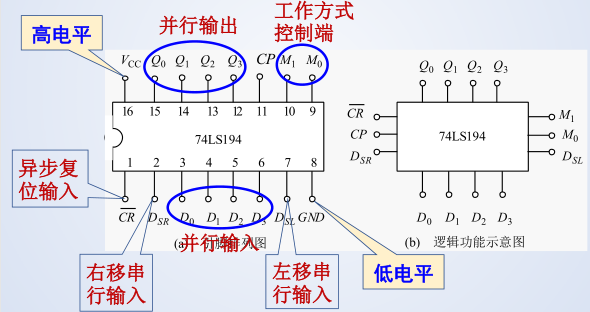

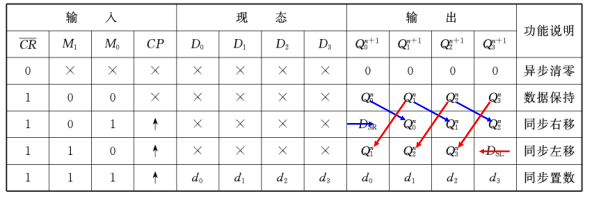

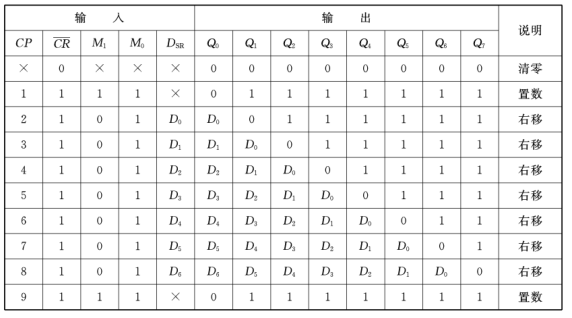

(3) 4位双向移位寄存器74LS194

74LS194的逻辑功能表如下:

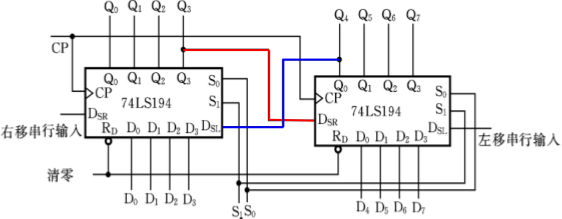

例. 利用两片集成移位寄存器74LS194扩展成一个

8

8

8 位移位寄存器

分析如下:

- 74LS194受统一的时钟脉冲控制, 8 8 8 位移位寄存器也应该同步运行;

- 74LS194的清零端应该一起接受控制;

- 工作方式控制段也应该统一被控制;

- 为了左移,必须将右边那片74LS194的

Q

4

Q_4

Q4 指向左边74LS194的

D

S

L

D_{SL}

DSL 输入端;同理可以右移:

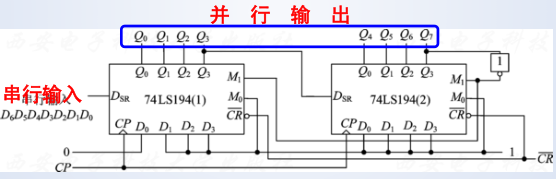

(4) 移位寄存器的应用——实现数码串/并转换

串/并转换是指将串行输入的数据,经转换电路之后变成并行输出,常用于计算机通信中的数据接收方。

Step1:

C

R

‾

overline {CR}

CR 端加低电平,异步清零,

Q

7

=

0

,

M

1

M

0

=

11

Q_7 = 0,M_1M_0 = 11

Q7=0,M1M0=11 ,寄存器处于置数工作状态;

Step2:

C

R

‾

overline {CR}

CR 端加高电平,当第一个 CP 上升沿到来时,输出端:

Q

0

Q

1

Q

2

Q

3

Q

4

Q

5

Q

6

Q

7

=

01111111

Q_0Q_1 Q _2 Q_3 Q_4 Q_5 Q_6 Q_7 =01111111

Q0Q1Q2Q3Q4Q5Q6Q7=01111111 ,

Q

7

=

1

,

M

1

M

0

=

01

Q_7 =1,M_1 M_0 =01

Q7=1,M1M0=01 ,寄存器处于串行右移工作方式;

Step3:当第二个 CP 上升沿到来时,输出端数据右移

1

1

1 位:

Q

0

Q

1

Q

2

Q

3

Q

4

Q

5

Q

6

Q

7

=

D

0

0111111

Q_0 Q_1 Q_2 Q_3 Q_4 Q_5 Q_6 Q_7 =D_0 0111111

Q0Q1Q2Q3Q4Q5Q6Q7=D00111111 ,

Q

7

=

1

,

M

1

M

0

=

01

Q_7 =1,M_1 M_0 =01

Q7=1,M1M0=01 ,寄存器处于串行右移工作方式;

Step4:在后续的

6

6

6 个 CP 上升沿到来时,输出端数据依次右移

1

1

1 位:

Q

0

Q

1

Q

2

Q

3

Q

4

Q

5

Q

6

Q

7

=

D

6

D

5

D

4

D

3

D

2

D

1

D

0

0

Q_0 Q _1 Q_2 Q_3 Q_4 Q_5 Q_6 Q_7 =D_6 D_5 D_4 D_3 D_2 D_1 D_0 0

Q0Q1Q2Q3Q4Q5Q6Q7=D6D5D4D3D2D1D00 ,此时,串行输入的数据已被转换成并行输出。

数据串/ 并转换电路的逻辑功能表:

三、多谐震荡电路(补充)

1. 多谐振荡器

多谐振荡器是一种自激振荡器,在接通电源后,不需要外加触发信号,便能自动产生矩形脉冲。多谐振荡器在工作过程中没有稳定状态,故称为无稳态电路。

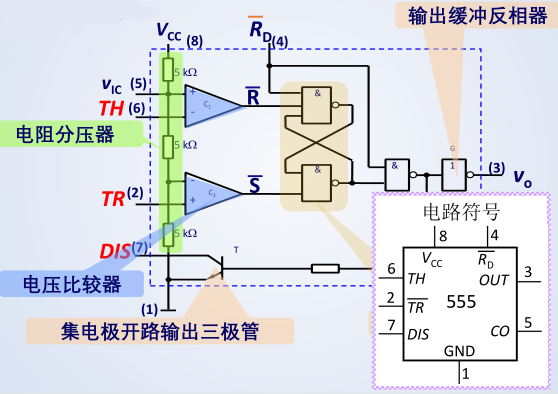

2. 555定时器

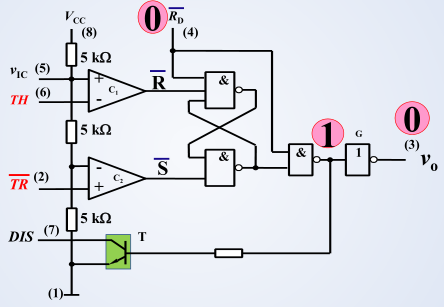

(1) 电路结构

(2) 工作原理

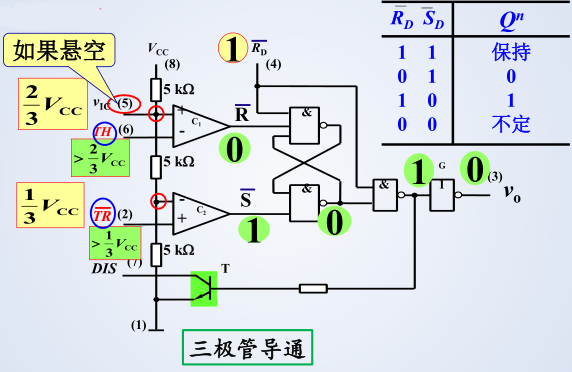

a.

R

D

‾

=

0

overline {R_D} = 0

RD=0 时,三极管导通:

b.

R

D

‾

=

1

,

T

H

>

2

3

V

C

C

,

T

R

‾

>

1

3

V

C

C

overline {R_D} = 1,TH > {2over 3} V_{CC},overline {TR} > {1over 3} V_{CC}

RD=1,TH>32VCC,TR>31VCC时,

R

‾

=

0

,

S

‾

=

1

overline R = 0,overline S = 1

R=0,S=1,三极管导通:

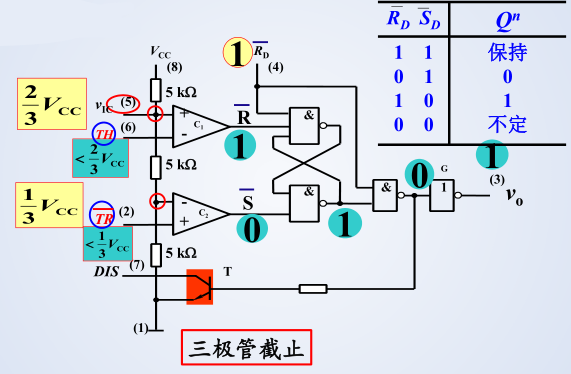

c.

R

D

‾

=

1

,

T

H

<

2

3

V

C

C

,

T

R

‾

<

1

3

V

C

C

overline {R_D} = 1,TH < {2over 3} V_{CC},overline {TR} < {1over 3} V_{CC}

RD=1,TH<32VCC,TR<31VCC时,

R

‾

=

1

,

S

‾

=

0

overline R = 1,overline S = 0

R=1,S=0,三极管截止:

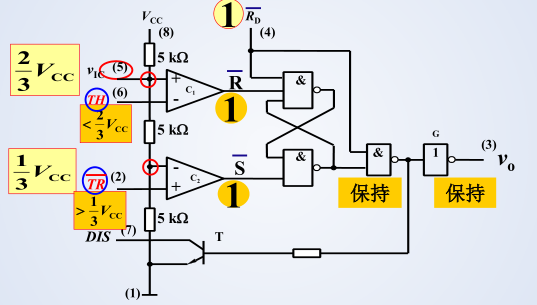

d.

R

D

‾

=

1

,

T

H

<

2

3

V

C

C

,

T

R

‾

>

1

3

V

C

C

overline {R_D} = 1,TH < {2over 3} V_{CC},overline {TR} > {1over 3} V_{CC}

RD=1,TH<32VCC,TR>31VCC时,

R

‾

=

1

,

S

‾

=

1

overline R = 1,overline S = 1

R=1,S=1,三极管保持:

e. R D ‾ = 1 , T H > 2 3 V C C , T R ‾ < 1 3 V C C overline {R_D} = 1,TH > {2over 3} V_{CC},overline {TR} < {1over 3} V_{CC} RD=1,TH>32VCC,TR<31VCC时, R ‾ = 0 , S ‾ = 0 overline R = 0,overline S = 0 R=0,S=0,无意义。

(3) 工作原理

功能表总结如下:

3. 用555定时器构成多谐振荡器

(1) 电路结构

(2) 工作原理

a. 第一暂稳态。接通

V

C

C

V_{CC}

VCC 后:

开始时

T

H

=

T

R

‾

=

u

C

≈

0

TH = overline {TR} = u_C approx 0

TH=TR=uC≈0 ,

u

O

u_O

uO 为高电平,放电管截止,

V

C

C

V_{CC}

VCC 经

R

1

,

R

2

R_1,R_2

R1,R2 向

C

C

C 充电 ,

u

C

u_C

uC 上升,这时电路 处于暂稳态

I

I

I 。

b. 第二暂稳态。当

u

C

u_C

uC 上升到

T

H

=

T

R

‾

=

u

C

≥

2

3

V

C

C

TH = overline {TR} = u_C ≥ {2 over 3} V_{CC}

TH=TR=uC≥32VCC 时,

u

O

u_O

uO 跃变为低电平,同时放电管

T

T

T 导通,

C

C

C 经

R

2

R_2

R2 和

T

T

T 放电,

u

C

u_C

uC 下降,电路进入暂稳态

Ⅱ

Ⅱ

Ⅱ 。

c. 第三暂稳态。当

u

C

u_C

uC 下降到:

T

H

=

T

R

‾

=

u

C

≤

1

3

V

C

C

TH = overline {TR} = u_C le {1 over 3} V_{CC}

TH=TR=uC≤31VCC 时,

u

O

u_O

uO 重新跃变为高电平,同时放电管

T

T

T 截止,

C

C

C 又被充电,

u

C

u_C

uC 上升,电路又返回到暂稳态

Ⅰ

Ⅰ

Ⅰ 。

(3) 振荡频率计算

电容

C

C

C 如此循环充电和放电,使电路产生振荡,输出矩形脉冲。

t

P

H

≈

0.7

(

R

1

+

R

2

)

C

t_{PH} approx 0.7(R_1 +R_2)C

tPH≈0.7(R1+R2)C

t

P

L

≈

0.7

R

2

C

t_{PL} approx 0.7R_2C

tPL≈0.7R2C

周期:

T

=

t

P

H

+

t

P

L

=

0.7

(

R

1

+

2

R

2

)

C

T = t_{PH} + t_{PL} = 0.7(R_1+2R_2)C

T=tPH+tPL=0.7(R1+2R2)C

频率:

f

=

1

(

t

P

L

+

t

P

H

)

≈

1.43

(

R

1

+

2

R

2

)

C

f = {1 over {(t_{PL} + t_{PH})}} approx {1.43 over (R_1 +2R_2)C}

f=(tPL+tPH)1≈(R1+2R2)C1.43

占空比:

q

=

t

P

H

T

=

R

1

+

R

2

R

1

+

2

R

2

q = {t_{PH} over T} = {{R_1+R_2}over {R_1 +2R_2}}

q=TtPH=R1+2R2R1+R2

最后

以上就是强健宝马最近收集整理的关于【数字逻辑】学习笔记 第五章 Part3 时序逻辑电路(常用时序逻辑电路及其应用)一、计数器二、寄存器三、多谐震荡电路(补充)的全部内容,更多相关【数字逻辑】学习笔记内容请搜索靠谱客的其他文章。

发表评论 取消回复