写寄存器前必须掌握的知识:

1、模块module的写法

2、寄存器:寄存器是由触发器构成,暂时存放数码或指令,存入和读取数据可以是串行或者并行。寄存器存取速度很快。

cpu如何执行一条高级指令:a+=10b?

①cpu将a搬到寄存器1中,

②把b搬到寄存器2中,

③把10搬到寄存器3中,

④把10b的执行结果搬到寄存器2中,此时并没有搬到新的寄存器中

⑤把a+10*b的执行结果搬到寄存器1中,

⑥最后把寄存器1中的数据搬到a存储器中,即分配了新的存储单元a

1、一个模块定义里面需要哪些东西?

时钟、输入、输出

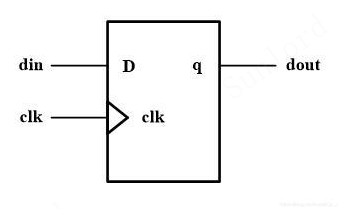

2、一个最基本的寄存器:(d触发器构成)

对应到模块里面就是三个变量:输入in、输出out、时钟clk

对应到模块里面就是三个变量:输入in、输出out、时钟clk

功能:在时钟上升沿,输入in 进入到 输出

module jcq(clk,in,out)//第一步定义模块,verilog要习惯使用模块。模块里面的东西:时钟、复位信号

input clk;//使用tab,不要和module左对齐了

input [3:0] in;

output out;//定义输出,不能忘记了

reg out;//定义输出为寄存器

always(posedge & !clk)//时钟上升沿时执行语句

//if 根据功能来看,是不需要if的,不要一看到always就想到if

begin

out<=in;

end

endmodule

最后

以上就是柔弱菠萝最近收集整理的关于verilog写寄存器的全部内容,更多相关verilog写寄存器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复