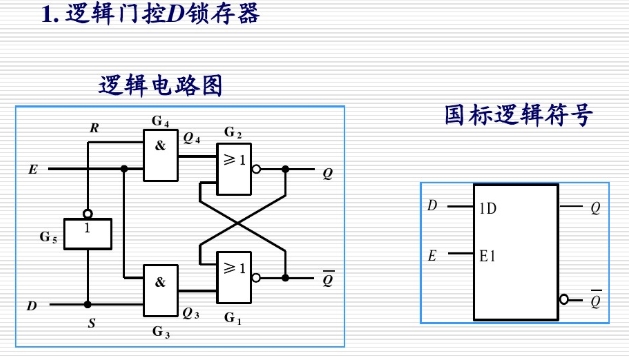

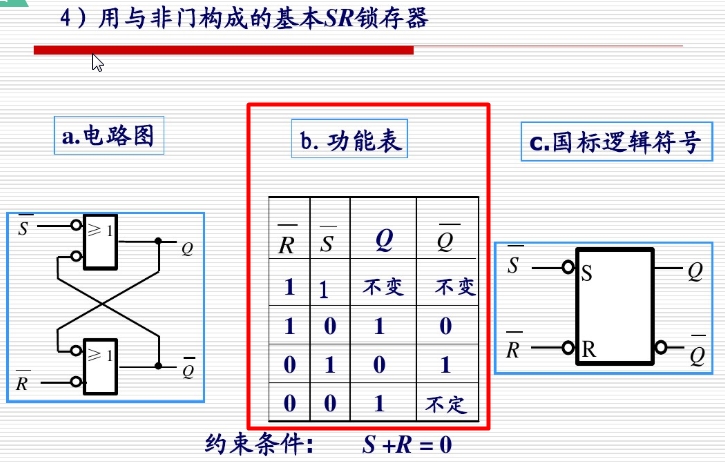

锁存器(latch):电平触发的存储单元,数据存储的动作(状态转换)取决于输入锁存信号的电平值,当锁存信号有效时,输出才会随着数据输入发生变化;当锁存信号无效时,输出信号保持不变。下面列举了SR和D锁存器的功能表:

锁存器特点:

- 锁存器在控制信号有效时,输出信号等于输入信号。 所以,输入信号的任何变化, 都将直接引起锁存器输出状态的改变。这时输入信号若发生多次变化,输出状态也可能发生多次变化,这一现象称为锁存器的空翻。

- 锁存器的控制信号有效时,锁存器就变成了一个组合电路,时序逻辑电路的模型就等效为两个各组合电路互为反馈的反馈系统,因此,系统有可能会因为瞬态特性不稳定而产生振荡现象。

触发器(flip-flop):边沿敏感的存储单元,数据存储的动作(状态转换)由某一信号的上升或者下降沿进行同步的(限制存储单元状态转换在一个很短的时间内) 。(钟控 D 触发器其实就是 D 锁存器,边沿 D 触发器才是真正的 D 触发器)触发器分为两种,一种是主从触发器和边沿触发器。主从触发器在时钟有效期内 (主触发器) 接收数据,在时钟边沿输出状态转换。边沿触发器在时钟边沿期间, 触发器才接收数据并使输出状态转换。现在基本上都是用边沿D触发器。

寄存器(register):用来暂时存放参与运算的数据和运算结果。在实际的数字系统中,通常把能够用来存储一组二进制代码的同步时序逻辑电路称为寄存器。

三者的区别对比:

触发器和寄存器区别与联系:由于触发器内有记忆功能,因此利用触发器可以方便地构成寄存器。由于一个触发器能够存储一位二进制码,所以把 n 个触发器的时钟端口连接起来就能构成一个存储 n 位二进制码的寄存器。

寄存器和锁存器的区别与联系:寄存器和锁存器的功能是相同的;它们的区别在于寄存器是同步时钟控制,而锁存器是电位信号控制。

一般的设计规则:在绝大多数设计中避免产生锁存器。锁存器最大的危害在于不能过滤毛刺 (使能信号有效时,输出状态可能随输入多次变化,产生空翻) 。这对于下一级电路是极其危险的。所以,只要能用 D 触发器的地方,就不用锁存器。

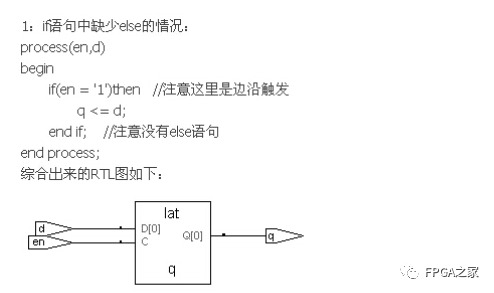

举例:在基于 always 的组合逻辑描述语句中容易综合出锁存器的地方:1:if 语句的使用中缺少 else 语句(前提是不是始终边沿触发);2:case 语句中没有给出全部的情况。

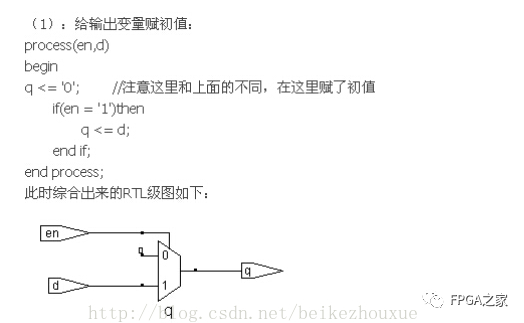

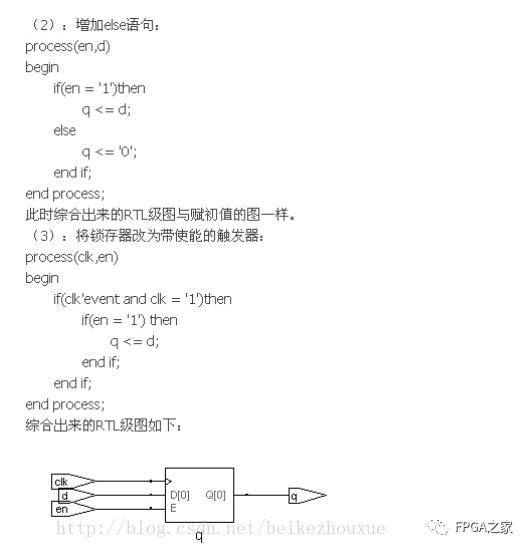

从上图可以看出综合出来的是锁存器。针对这种情路可以采用一些措施来防止生成锁存器:给输出变量幅初值;增加 else 语

句;将锁存器改为带使能的触发器。如下:

此时综合出来的就是选择器。

参考文章链接: https://mp.weixin.qq.com/s/5VPWqgq2G9zFFxTZ0R5_ow

最后

以上就是聪明咖啡最近收集整理的关于FPGA系列9——锁存器、触发器和寄存器的区别的全部内容,更多相关FPGA系列9——锁存器、触发器和寄存器内容请搜索靠谱客的其他文章。

发表评论 取消回复