1、触发器(以与非门为例,或非门可自行推导)

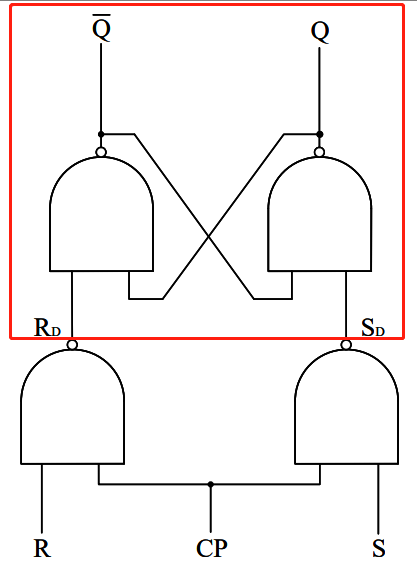

- 基本RS触发器

其中红色框图为基本RS触发器结构,特征方程为 Q n + 1 = S D ‾ + R D Q Q^{n+1}=overline{S_D}+R_DQ Qn+1=SD+RDQ, 限制条件为 R D + S D = 1 R_D+S_D=1 RD+SD=1。

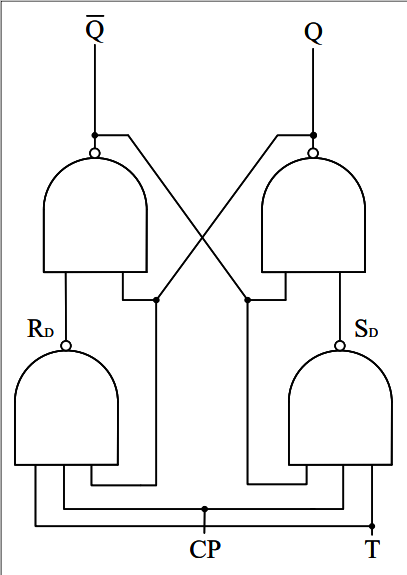

- 钟控RS触发器

1、各种钟控触发器相对与基本RS触发器,其状态转换由时钟控制,输入变化不一定会导致输出立即变化,而是按照一定的节拍进行动作;

2、CP=0: 触发器保持;CP=1: 特征方程为 Q n + 1 = S + R ‾ Q Q^{n+1}=S+overline{R}Q Qn+1=S+RQ,限制条件为 R S = 0 RS=0 RS=0。

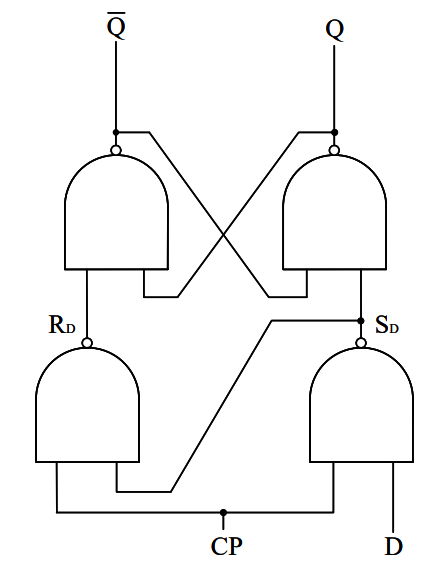

- 钟控D触发器

CP=0: 触发器保持;CP=1: 特征方程为 Q n + 1 = D Q^{n+1}=D Qn+1=D。

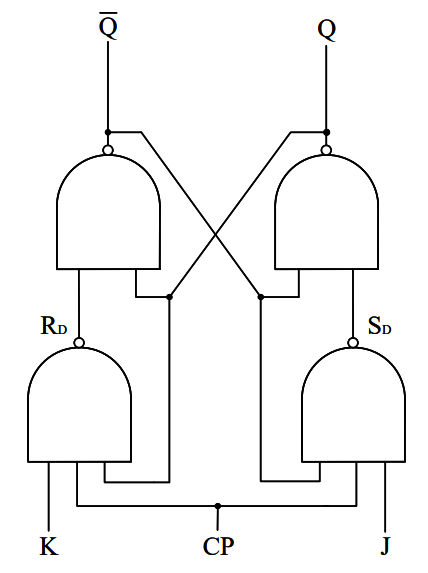

- 钟控JK触发器

1、CP=0: 触发器保持;CP=1: 特征方程为 Q n + 1 = J Q ‾ + K ‾ Q Q^{n+1}=Joverline{Q}+overline{K}Q Qn+1=JQ+KQ;

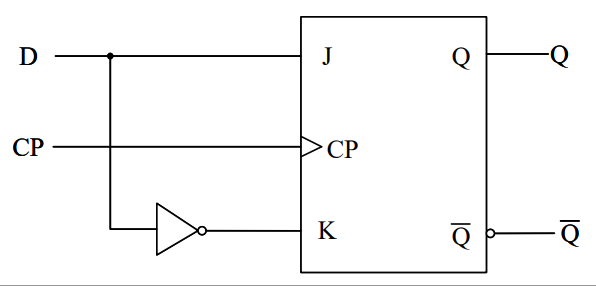

2、可以将 K K K输入端变成 J ‾ overline{J} J,使得JK触发器转化为 D D D触发器, Q n + 1 = J Q ‾ + J Q = J Q^{n+1}=Joverline{Q}+JQ=J Qn+1=JQ+JQ=J。

- 钟控T触发器

钟控T触发器即将JK触发器两个端口输入相同,CP=0: 触发器保持;CP=1: 特征方程 Q n + 1 = T Q ‾ + T ‾ Q = T ⊕ Q Q^{n+1}=Toverline{Q}+overline{T}Q=T oplus Q Qn+1=TQ+TQ=T⊕Q

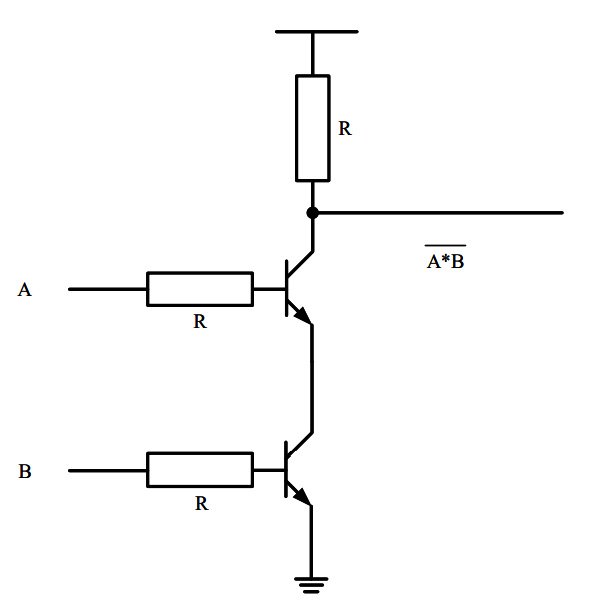

2、与非门 三极管搭建

参考: 三极管搭的逻辑门

微信公众号:通信随笔XIDIAN

最后

以上就是开放板凳最近收集整理的关于Verilog/数电 知识点随记(2)的全部内容,更多相关Verilog/数电内容请搜索靠谱客的其他文章。

发表评论 取消回复