ETM & Abstract model

由于目前的design越来越大,所以都倾向于hierarchy flow,走bottom-up的方式,也就是先从block开始做,然后再做sys level,最后做top level;

我们做完block level后,然后去做sys level时需要提供 block model,而block model可以分为两类:

1、ETM(Extracted timing model)

2、Abstract model

那么他们的区别是什么呢?

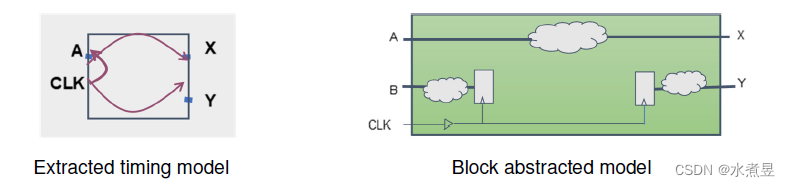

首先看下图

在ETM中,可以看出,这个model中只包含了input和output port和clock port之间的约束关系,没有具体描述block的内部信息;

而在abstract model中,描述了和input和ouput相关的interface logic的信息,包括

1、完整的clock network信息(A-Y)

2、input port到第一级flop的timing信息以及clock delay信息;

3、flop与output port之间的timing信息以及clock delay信息;

4、记录每个scenario下的上面的信息

两者使用的命令也不一致,分别是:

1、extract_model

2、create_abstract

那么什么时候用ETM,什么时候用abstract model呢?

Abstract benefits

使用abstract model的优点可以分几个部分:

1、Block Interface Timing Convergence

2、Clock

3、VCLP Convergence

Block Interface Timing Convergence

使用Abstract model的好处在于可以使用flat sdc,无需使用hierarchy sdc,另外在处理top与block之间的timing关系时会更方便;

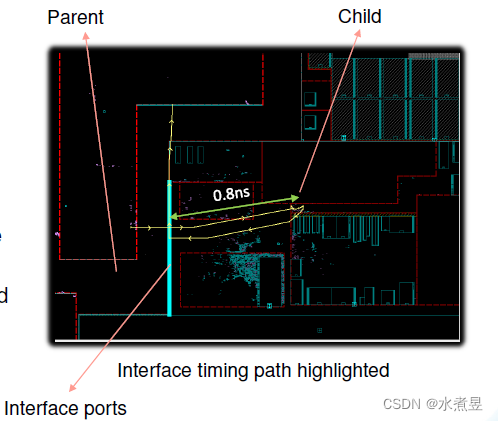

以下图为例

这里有一条top-to-block的timing path,由于我们使用的是Abstract mode,这个model中记录了capture register的timing信息,包括data path和clock啦path的delay信息,这是ETM无法提供的;

Clock

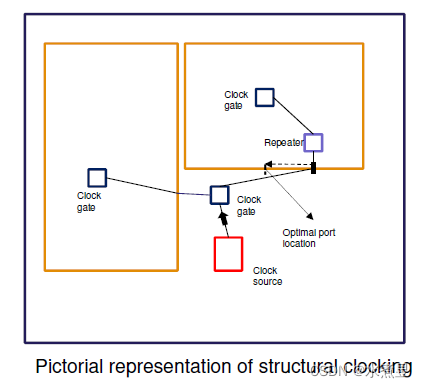

在做full chip的CTS时,需要block的clock tree信息,这是ETM无法提供的,而Abstract model可以提供,如下图

同时,我们可以对block做优化,例如上图中,我们可以调整clock port的location,使其更加合理,另外,还可以调整macro的位置,获得更好的timing;

VCLP Convergence

Abstract model中记录了连接到port的leaf logic的相关供电信息,这样我们可以很早发现VCLP的问题,例如

1、缺少iso或者level shifter可以更早发现,因为port连接的leaf cell信息也记录在abstract model中了;

2、Buffering was correct by construct from power domain perspective;

Timing Budgeting

在我们做timing budgeting时,也会使用到abstract model;

Timing Budget Flow

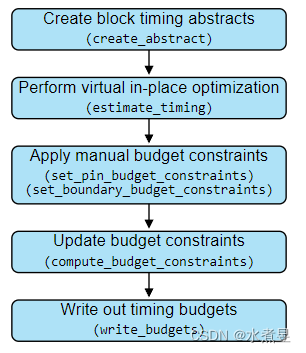

Timing Budget Flow如下图所示

做timing budget前,我们要先准备好chip level的SDC和UPF,并将其split成top level和block level的SDC和UPF;

当我们做top level的timing时,需要的是top SDC和block的abstract model;block level则使用block sdc即可;

Split Constraints Flow

Top level SDC主要包含以下几部分:

1、top level UPF

2、top level timing constraint

3、top-to-block boundary timing

最后

以上就是虚幻泥猴桃最近收集整理的关于ETM and Abstract modelETM & Abstract modelTiming Budgeting的全部内容,更多相关ETM内容请搜索靠谱客的其他文章。

发表评论 取消回复