数字逻辑综合工具-DC-04

——怎样增加时序约束(Timing Constraints)

逻辑综合的过程为:转化 优化 映射

另外还有环境约束和面积约束

时序有三个大的方面

input logic paths

internal paths

output paths

一个项目需要有一个spec即设计说明书

里面有项目的一些要求【文字性的描述】

(功能要求 性能要求)

逻辑综合需要添加满足这些要求的约束

在写rtl代码的时候最好是单个时钟,单沿触发,不然会生成一些很奇怪的FF

默认情况下,不告诉dc,默认为同步时钟

异步时钟需要手动设置

做时序分析需要路径

何为路径:

起点->终点

起点:Input port

Clock pin of FF or register

终点:Output port

input pin of a sequential device, except clock pin

【dc_shell 的一些Tcl命令】

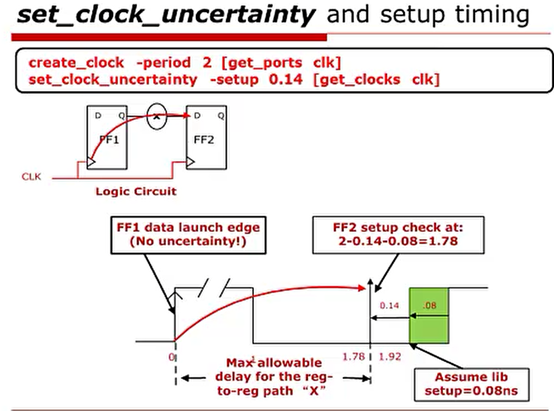

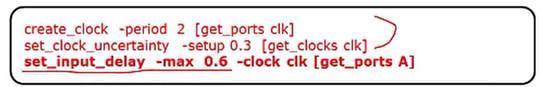

create_clock -period 2 [get_ports clk]

【创建时钟】【2ns】

【默认单位是ns】

【从工艺库里通过 report_lib 命令查看】

Tmax=Tc2q+Tcomb+Tsu

创建时钟的时候可以指定占空比 -waveform(注意,单位是时间),也可以指定一个名字-name

dc认为时钟是ideal的,dc不会处理时钟网络,因为直接放置clk会有大扇出,dc算的不准!这部分的工作是后端去做的!!后端的CTS(时钟树综合)

实际的时钟会有sker和jitter,可以用一个参数对这些特性进行模仿:

set_clock_uncertainty -setup Tu [get_clocks clk]

一般来讲,对setup建立一个模型

比如

会在原来setup time的基础上增加不确定度

设置时钟的上升时间、下降时间(即斜坡)

set_clock_transition Tt [gets_clocks clk]

这些值是猜测出来的,版图画好了之后,就不需要这些猜测的值了(CTS之后的STA)

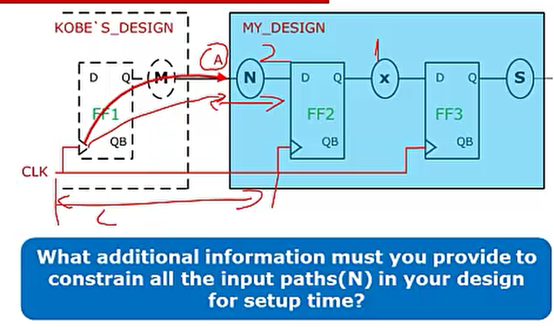

在路径涉及到外部端口的时候,如输入端,需要人为地告诉DC,之前的延时是多少

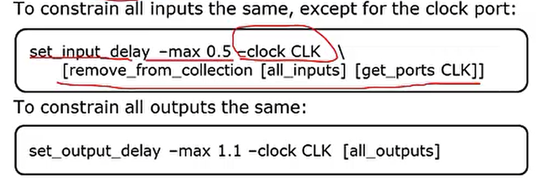

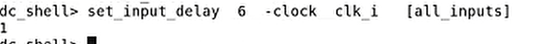

上一条:输入延迟,(要指定clock,(-clock CLK))输入端口要去除掉CLK,提取出端口进行约束

下一条:输出延迟(clock不是输出端口,不需要remove_from_collection)

【注意:一定要指定 clock】

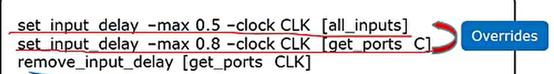

如果设置了多次,后面的会把前面的覆盖掉

这很有用,比如如果跟着input ports一起设置了CLK的input_delay, 可以通过remove_input_delay排除掉

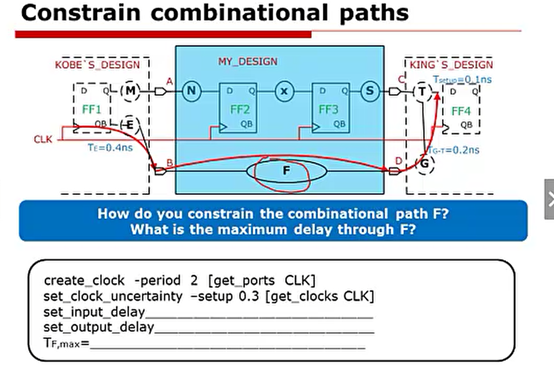

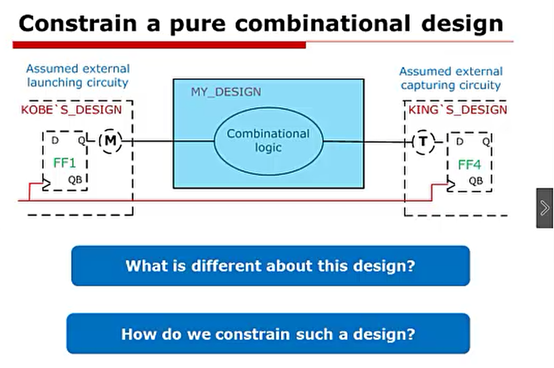

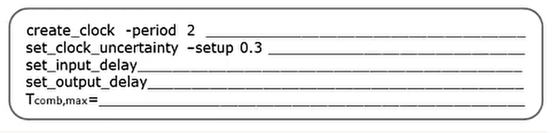

【从input到output的组合路径】

它处在两个寄存器的中间

1、 创建一个时钟

2、 clock uncertainty

3、 input_delay output_delay

【纯组合电路】

从输入直接到输出,没有时钟,那么就需要创建一个虚拟时钟(没有跟任何端口相连接)

这里的时钟是一个纯虚拟的,因为要跟其它电路相对于同一个参考源

create_clock -name VCLK -period 2

注释:

1、 设置虚拟时钟

2、 设置clock_uncertainty

3、 设置input_delay, output_delay

4、 根据纯组合设计约束

估算:不知道怎么设置input_delay 和output_delay的时候,采用组合电路40%+40%,剩下的20%留给clock_to_q和setup

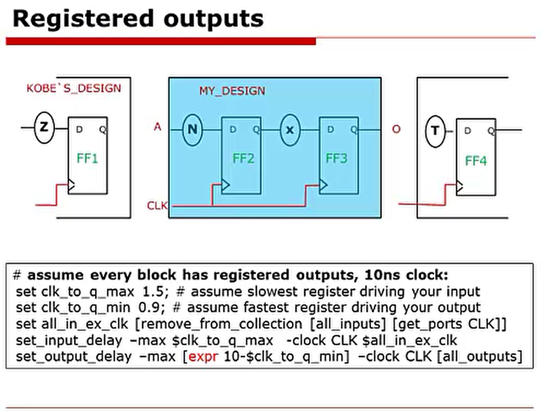

【寄存器输出】

所有的组合路径都集中在D触发器的输入端口

只要告诉dc clock2q的时间是多少就可以了

【注意output_delay 的写法 [expr 10-$clk_to_q_min]】(contamination delay)

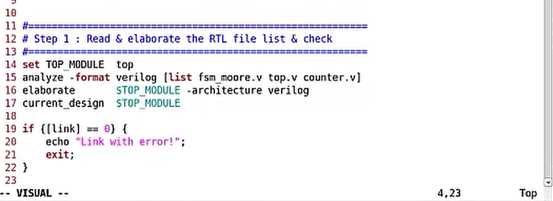

【实操环节】

list_designs

【查看当前dc读了的文件】

remove_design -hierarchy

analyze -format verilog [list top.v conter.v fsm_moore.v]

elaborate -architecture verilog top

【这两个指令会实现link,elaborate会自动指定top,也可以手动敲link】

但是用current_design 命令更好读

设计读进来了,需要检查一下语法命令

比如在例化的时候有没有出现递归

check_design

如果返回0,就有问题

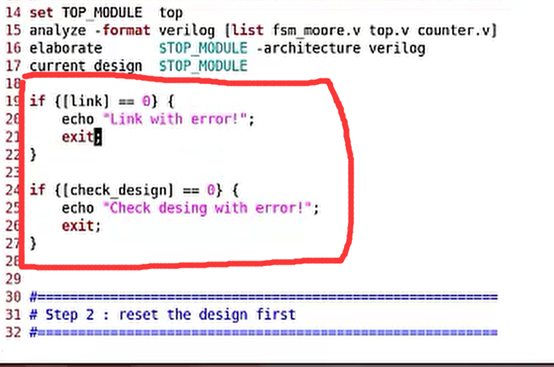

【在top脚本里,一般要做一些查错,如果有错,直接退出】

比如link_library没有设,或者library找不到

然后check_design,如果发生了module之间的嵌套,这里会查出来

在添加约束之前,建议执行reset_design

把以前的约束全部抹掉

【一部分在dc_shell下的实例操作:】

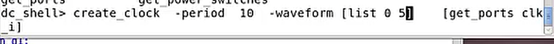

【创建时钟】

注意,如果设计里面涉及到了DDR器件,必须要指定占空比,不然差别很大

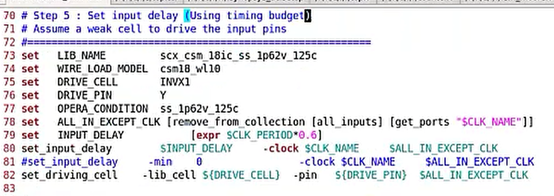

【input_delay】

外面留60%

(需要把clk剔除掉)

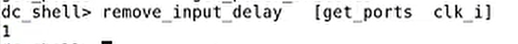

【检查时序问题check_timing】

检查有没有没有约束到的

【compile】

compile -map_effort high -area_effort high -boundary_optimization

(尽最大努力做优化)

DC到这里会去做综合

【做完综合之后,看看有没有约束违规的】

report_constraint -all_violators

工作环境,线负载模型、设计规则都没有约束,输入的驱动单元没有约束,输出的负载没有约束

还有一些别的命令:

report_timing -delay_type max【把最差的路径报出来】(后面会讲)

/*******************************

如何写一个DC的约束脚本

********************************/

【第一步】:把设计读进来,做一个link(也就是elaborate)

设置current_design

检查link和check_design,如果做失败了,就直接exit退出,因为综合是没有意义的

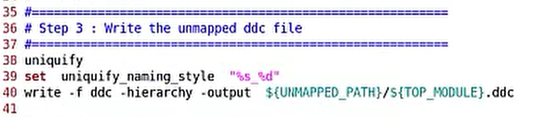

【第二步】:把以前的约束给撤销掉

【第三步】:暂不解释

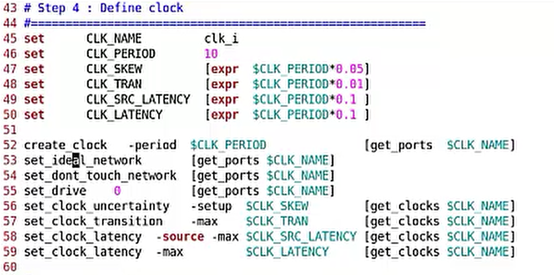

【第四(一)步】

【时钟约束】

1、 指定一些常用的名字,设置一些常用的变量

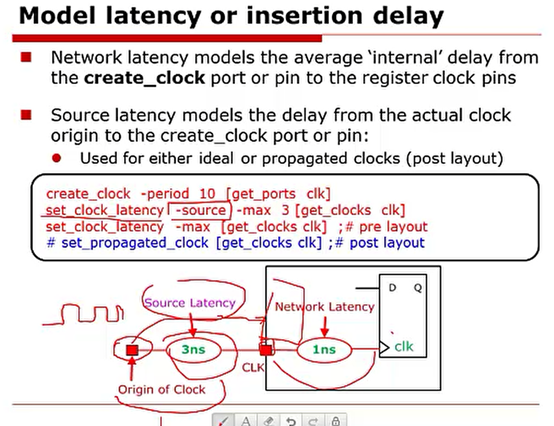

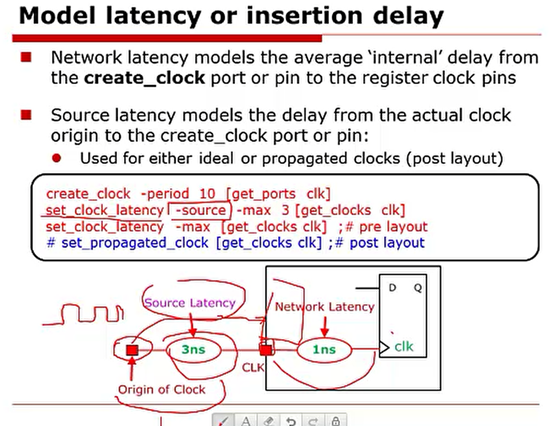

时钟的名字、周期、skew、transition time、latency、source latency

2、 创建时钟,指定周期和端口名

3、 set_ideal_network 这句话其实不用加,但是可以帮助理解

4、 don’t touch也是一句废话,对于ideal network,dc是不会管它的

5、 set_drive 0表示:驱动该端口的驱动能力无穷大

6、 set_clock_uncertainty模仿时钟树的skew

7、 set_clock_transition模仿时钟的transition

8、 source latency 模仿pcb板上的晶振到芯片引脚上的latency

9、 network latency 芯片的引脚到ff的clk端口的latency

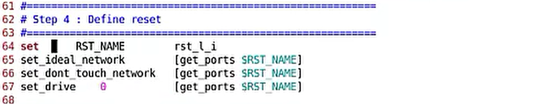

【第四(二)步】

【复位约束】

1、 指定复位的名字

2、 指定为理想网络

3、 指定为don’t touch

4、 驱动能力无穷大

【第五步】

【input_delay】

1、 set_input_delay 指定时长,指定clk,指定除了clk以外的其它输入端口

2、 指定驱动cell

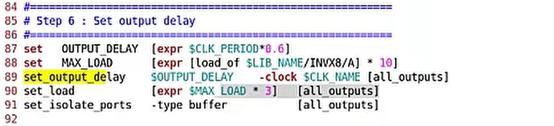

【第六步】

【outputdelay】

具体过程与大概同上

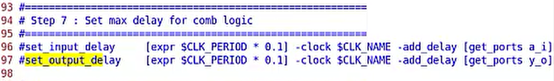

【第七步】

【组合逻辑最大延时】

………………………………………………

//这里很重要!!

【脚本写好了,怎么去检查语法错误?】

在dc_shell下运行命令:

dc_shell> dcprocheck <脚本名>

【写完之后,确认脚本没有错误,在dc_shell下启动脚本】

dc_shell> source …/script/top.tcl

(在top里面放了一个重定向的命令,把约束文件读进来)

最后

以上就是端庄太阳最近收集整理的关于数字逻辑综合工具-DC-04 ——怎样增加时序约束(Timing Constraints)数字逻辑综合工具-DC-04的全部内容,更多相关数字逻辑综合工具-DC-04内容请搜索靠谱客的其他文章。

发表评论 取消回复