第五课

Environment Attributes

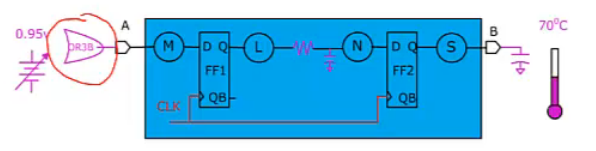

环境约束(environment attributes) 包括:1.输入驱动的强度 2.输出容性负载 3. PVT效应(温度的影响)以及工艺角 4.互连线上RC的影响

Factors affecting timing

图中标红的部分就是环境约束,添加环境约束的过程就是在模拟芯片实际的工作环境。

**即使不加任何约束DC也可以综合,但是综合出来的电路不一定能用。

- Cell delay是input_transition_time, output_capacitive_loading和PVTconditions的函数,这三种参数会影响电路的延迟。

- 为了模仿最差的情况,一般会使用ss工艺库进行综合。

Command

- Output

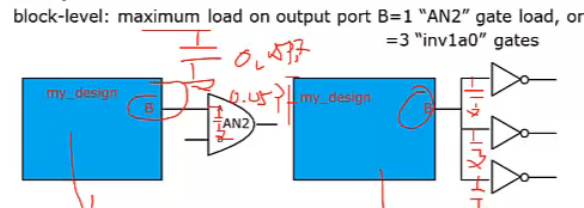

设置输出端口容性负载的命令如下,单位会在工艺库当中给出来:

set_load [expr 30.0/1000] [get_ports B]

如果不知道具体的容值,可以设置具体的器件端口

set_load [load_of _my_lib/AN2/A] [get_ports B] //AN2是load_of _my_lib中的器件,A是其中一个端口

set_load [expr{[load_of_my_lib/inv1a0/A]*3}] [get_ports B]

- Input

设置边沿传输时间:

set_input_transition 0.12 [get_ports A]

设置驱动强度:

set_driving_cell -lib_cell OR3B [get_ports A] //lib_cell选项可以选择某个器件作为驱动强度

set_driving_cell -lib_cell FD1 -pin Qn [get_ports A] //pin选项可以选择驱动哪个端口

-

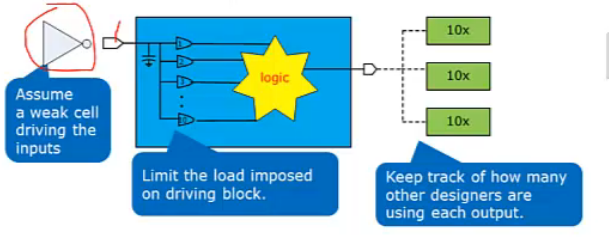

Load Budget

当不知道模块的输出负载/输入驱动的强度时,可以建立负载预算(Load budget)。

此时假设输入端口的能力较弱,并且给输入端口添加电容的约束,从而减小所接门的个数。

输出假设能够负载三个其它的模块

-

PVT effect

通常会有对应不同PVT工艺角的工艺库,详细可以去咨询工艺厂商。

list_lib可以查看当前装载了哪些工艺库。

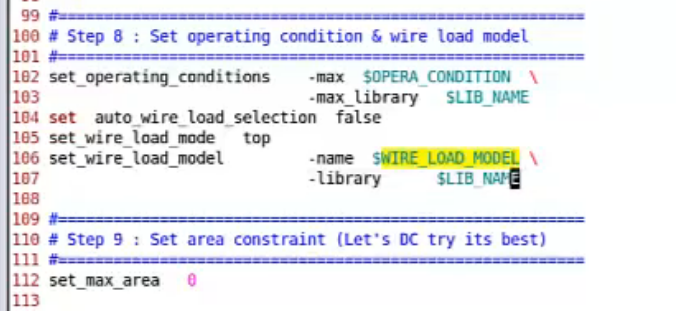

如果有很多工艺库,用命令set_operating_conditions设定operating conditions。

** 传输线的RC参数使用的是WLM(线负载)模型,当设计的芯片规模较小时线负载模型不必太过悲观,可以跟工艺厂商沟通。

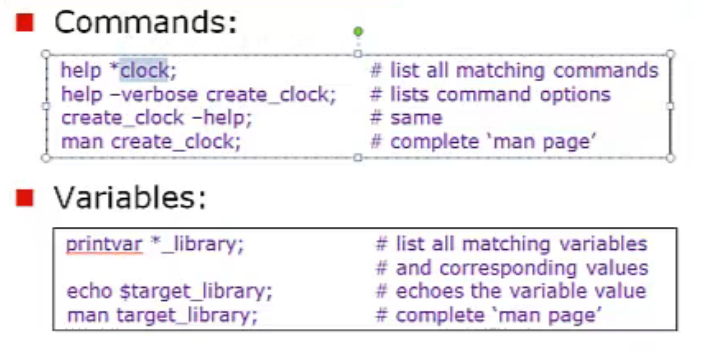

补充命令

DC自带的检查语法命令,不需要额外的安装:

dcprocheck TOP.con

查看目前所加的约束:

report_port -verbose

report_clock

report_clock -skew

检查是否有漏加的约束:

check_timing

其它:

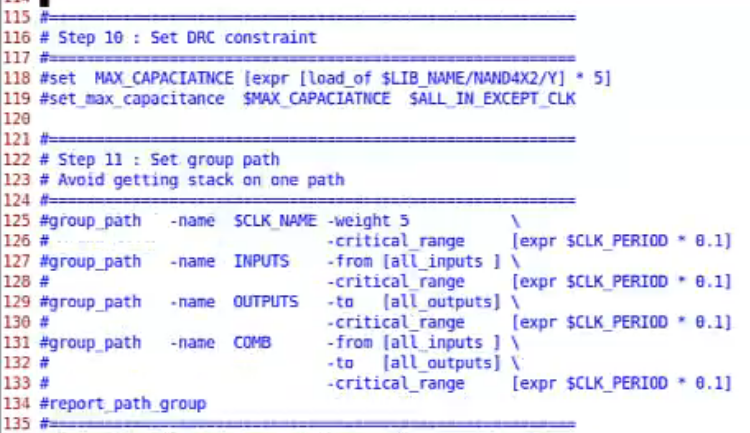

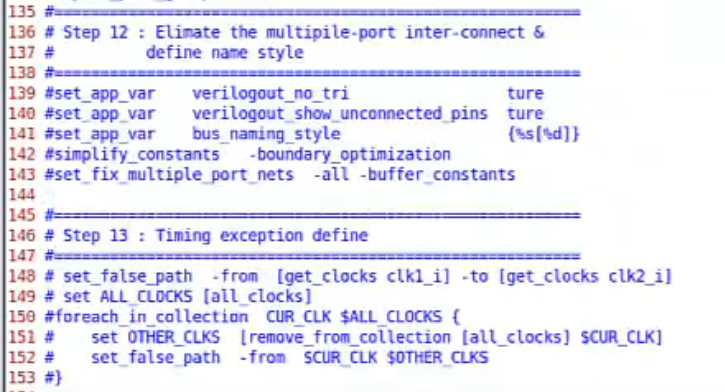

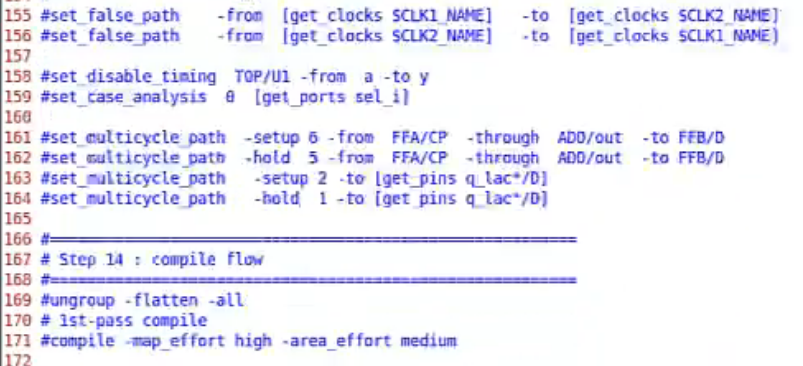

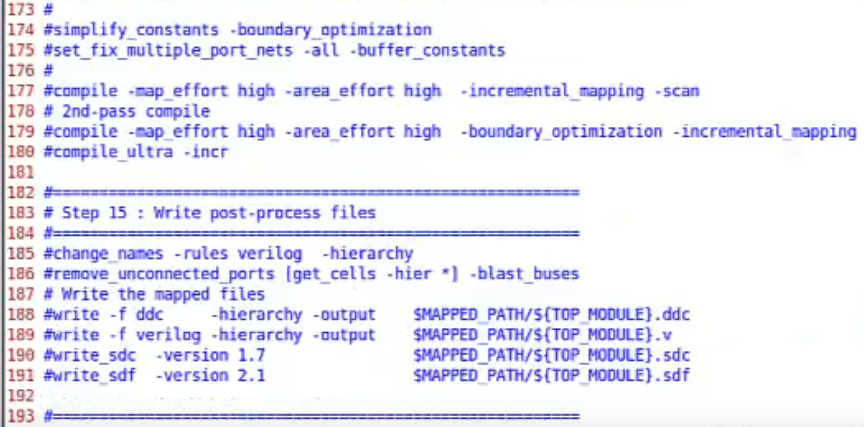

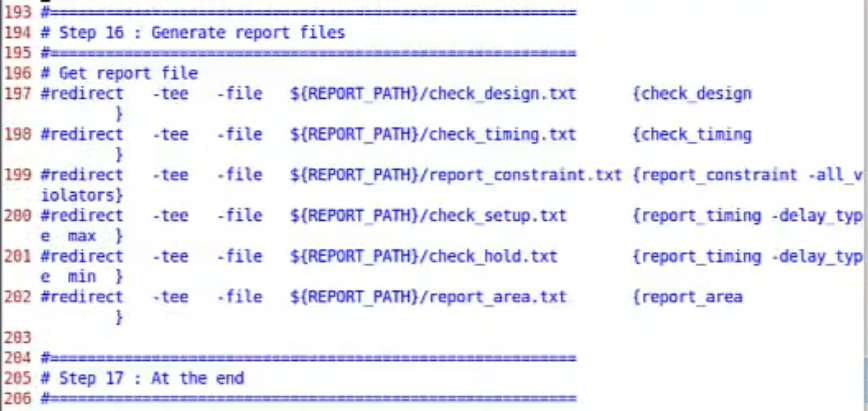

实例

(接上次课)

最后

以上就是听话手套最近收集整理的关于DC 视频教程 第五课的全部内容,更多相关DC内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复