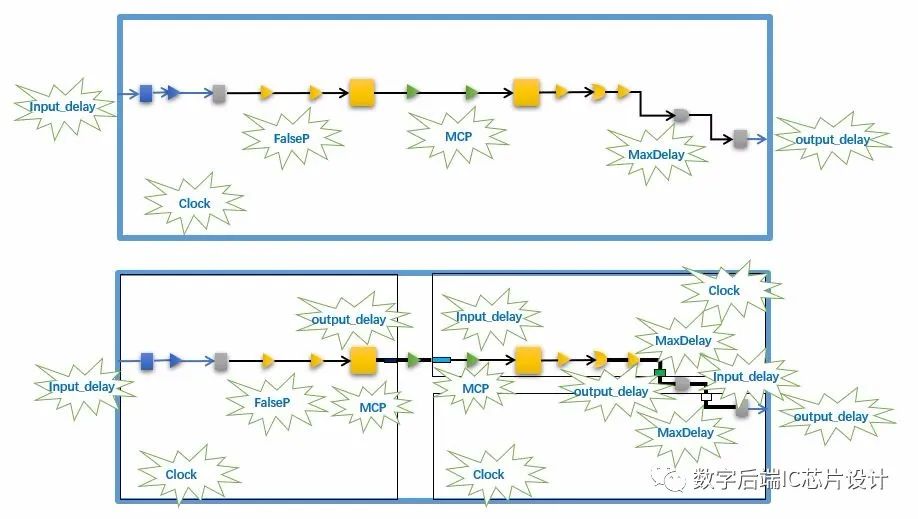

Timing budget是hierarchical flow中非常关键的一个步骤。Timing budget会分析整块芯片的时序情况,然后给各个block分配合适的时序约束文件。简单而言,Timing budget就是处理chip level上的各类sdc约束,包括set_input_delay(SID),set_output_delay(SOD),set_false_path,set_multicycle_path(MCP)以及clock的信息等等可以用下面的示意图表示:

假设上半部分是一条在full chip上完整的path,可以看到这条path上有input delay, output delay, false path, multicycle path, max delay, clock等信息,当定义完下面两个block并做完timing budget以后,工具会根据算法,重新去分配每个block端口上的约束。

那我们如何去做Timing budget呢?

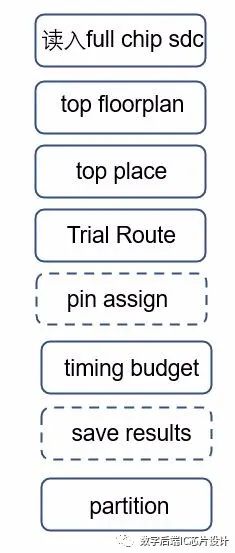

我们先来看一下它的flow.

1. 做timing budget之前,design的floorplan先要过关,timing budget本身并不会对优化你的设计,它也不能让一个很差的floorplan变成timing closure。所以在chip level flatten情况下,必须首先准备一个可以budgetable的floorplan.

2. 然后的,由于要计算每条timing path,所以要在chip level跑place以及trialRoute.

3. 做完physical budget(pin assignment)以后,就可以跑timing budget了,命令很简单,就是deriveTimingBudget。跑完以后可以save出timing budget的内容。主要如下:

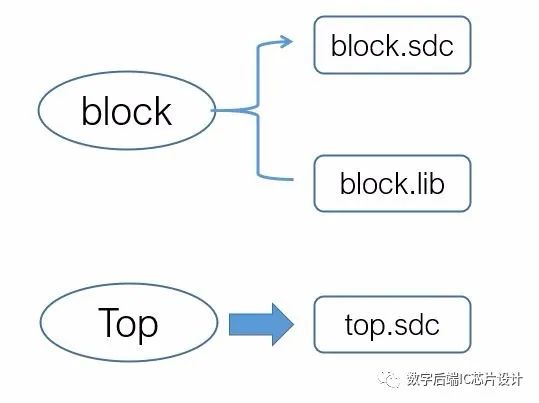

对于block level会save出block的sdc和lib, 对于top level,会save出top的sdc,并且timing budget会去处理chip level上的四种exception constrains(set_false_path, set_multicycle_path, set_min_delay, set_max_delay. 转换好top level和block level的view Definition file.

4. 最后,我们可以就可以commit partition. save出完整的block database.

往期回顾

IC工程师:百万年薪路上的20个阶段,你在哪个阶段?

静态时序分析STA合集一

静态时序分析STA合集二

时序基本概念介绍<sdc合集>

数字后端基本概念合集(一)

数字后端基本概念合集(二)

数字后端基本概念合集(三)

Low Power概念介绍合集

数字后端dbGet使用方法合集

号外,数字后端交流群招人啦

IC圈的世界杯 | 论芯片设计的胜利十一人

知否?知否?Block PD应该提交哪些数据?

Timing ECO手修攻略

数字后端面试100问(2019全新版)

数字后端面试100问(校招版)

简历请戳邮箱:taozhang3260@163.com

觉得有用的话,给我点个好看吧

最后

以上就是灵巧长颈鹿最近收集整理的关于时间都去哪了——timing budget(一)的全部内容,更多相关时间都去哪了——timing内容请搜索靠谱客的其他文章。

发表评论 取消回复