第二课

-

table

setup和hold time的检查也要通过一个table,在dc报告中的lib_setup_time的来源就是这一类表格。

信号传输的延迟以及控制晶体管开关的栅电压转换延迟,将会决定建立时间的正负。 -

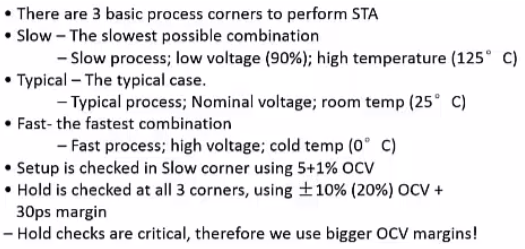

corner

一般高温低压的工艺参数会变差,但是60nm以下的某些工艺低温低压的参数也会较差。

layout canstraint

除了DRC和LVS意外还有DFM规则检查,DFM是工艺厂商推荐的规则,并不需要全部满足,但是会影响到芯片的良率。

-

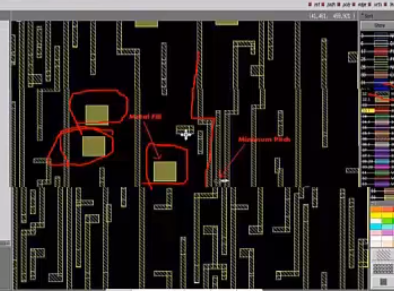

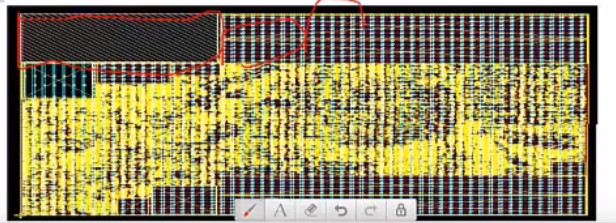

Metal fill

版图当中会有类似圈出来的金属dummy,保证芯片的金属密度均匀,从而满足流片过程中的抛光工艺的要求。

金属密度不够,会导致上层金属下沉,使timing model不准确,无法满足时序的要求。 -

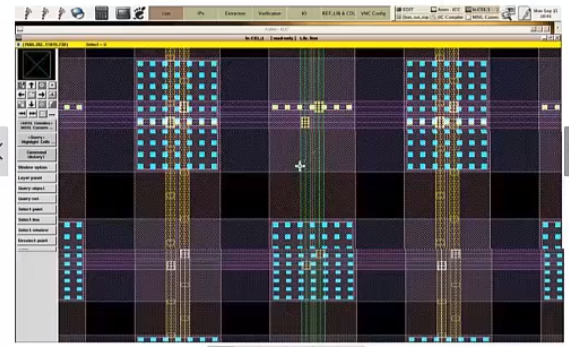

power grid

两根同信号的导线之间的距离叫做pitch,尽量保证不同信号的导线的pitch相同(如上图),可以避免多种寄生效应。

power constraints

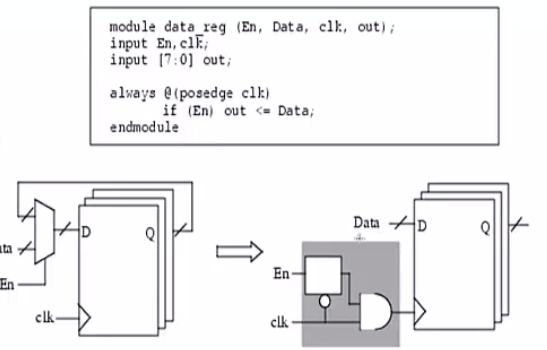

- clock gating

减少时钟反转带来的功耗

一般来说右边图中的en所接模块是latch - high vt cells

可以使漏电流更小 - power gating

多电压域设计,与工艺有关,例如LP代表low power

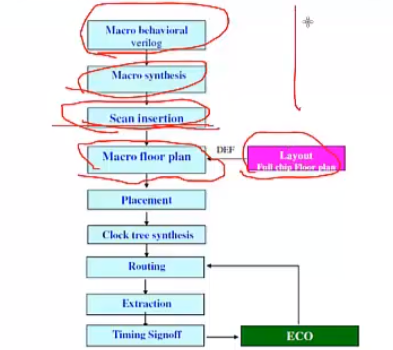

设计流程

-

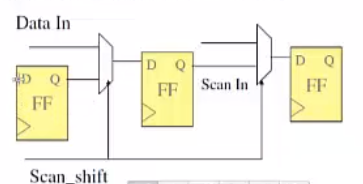

Scan Insertion

大致结构如下,以除法器和mux作为主体:

此步骤属于DFT的范围,还有shift capture等结构

在后端当中存在scandef文件,scandef当中描述了扫描链的结构。扫描链有两种结构,floating chain和ordered chain。两者的区别在于前者可以做scan reorder而后者不能。 -

Macro floor plan从顶层开始,首先从macro开始决定形状和大小,pin和port的位置则由软件根据布局生成,最后写成.DEF和netlist文件。这个步骤也叫做partition。

不仅会做floorplan的partition,还会做timing budget,从而产生sdc文件,用于block级别的后端。

***.def文件中描述了block,macro level的floorplan,比如pin的位置和power走线

macro cell放在四周,standard cell放在中间区

若floorplan没做好,绕线和时序都会出问题。 -

Routing分为三个步骤,首先做global routing,用虚拟的绕线方式确定大致的连线方式;然后做track(?) assignment,将线assign至track(?)上,到这步都不考虑DRC;第三部做detailed routing,进行真正的绕线

-

Extraction提取出寄生参数,提供给给后续的Timing signoff,包括cross cap带来的串扰,每个corner都要做

spef文件中描述了rc delay,pt做静态时序分析时线延迟来自版图,cell延迟来自lib文件 -

ECO的全称是Engineering change order,这个过程中对版图的critical path做微小的改动,然后再返回至Routing迭代,来调整电路的时序或者其它的潜在问题。

-

Clock Tree Synthesis

名词解释:

Clock root:create_clock时所定义的时钟信号输入口

End point:时序弧的终点

Ignore point:在ICC中叫做exception pin,指CTS时不受约束影响的end point,但是会受DRC的限制(包括transition,cap和fanout)

CTS的过程中会使用特殊的buffer保证balance delay

***一个cell驱动能力过强会造成EM(电迁移) -

Timing Signoff

时钟的transition与data path的transition要求是不一样的,时钟的transition变长就会极大影响动态功耗。

PR和signoff下算出来的model参数是不同的,若差距过大则需要debug,这个过程叫做correlation

遇到时序问题后修正的方法:(1)sizeup(2)加buffer(3)useful skew,使接受时钟的边沿到来更晚从而满足holdtime,但是会影响这一级的hold和下一级的setup(4)HVT/LVT(会影响功耗,优先级最后)

***做PR的时候有两种模型:NLDM和CCS,后者更为精确但是计算所需要的时间更长。

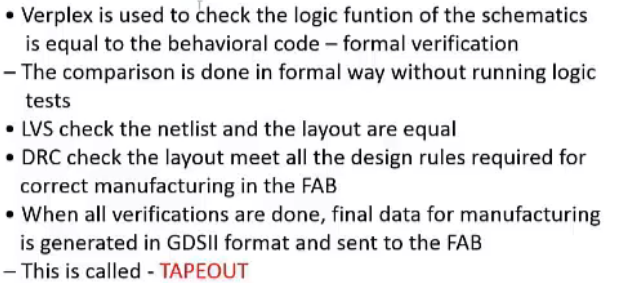

Other verification flows

包括形式检查,LVS检查,DRC检查

-

其它相关知识

tk语言经常用于制作gui界面;

前端部分无法解决的setup violation(即出现的slack)可以放到后端,利用CTS等手段解决

是否由后端可修要根据wns/tns(worst/total negative slack)综合判断 -

CTS routing

做时钟树的绕线时需要采用NDR(non-default rule),与默认的绕线规则做区别,可以设置更宽的线宽等特殊选项。

在布局时钟信号等high fanout pin时需要做hfs(high fanout synthesis)

最后

以上就是欢呼篮球最近收集整理的关于布局布线ICC 第二课的全部内容,更多相关布局布线ICC内容请搜索靠谱客的其他文章。

发表评论 取消回复