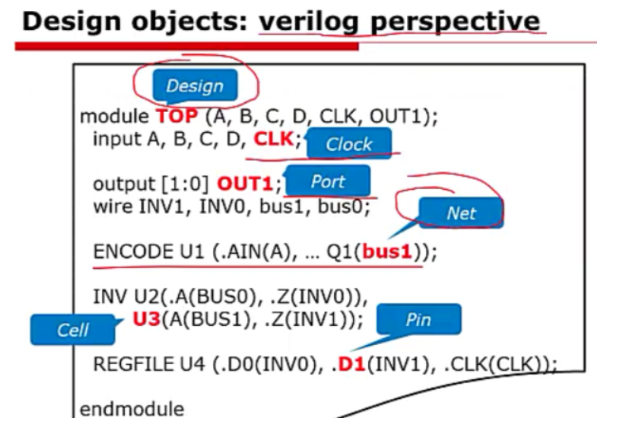

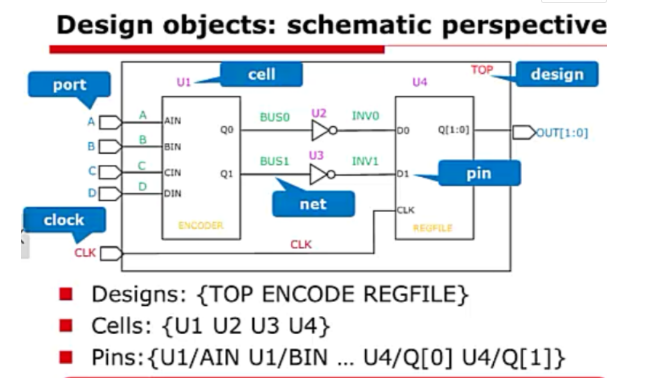

关于objects

1、分类

2、包括六类:Design、clock、port、net(模块与模块之间的互连线)、cell(例化的模块)、pin(cell里面的引脚)

3、design可以转换为cell

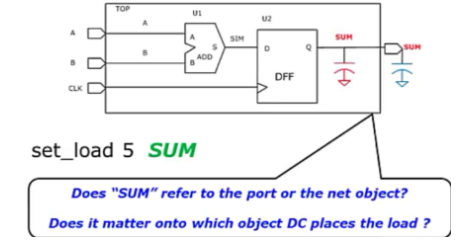

4、当objects名字相同时:

加在net上,5个单位的电容会覆盖原电容值;加在port上,5个单位电容与原电容值x并联,总电容值为(5+x)个单元

set_load 5 [get_net sum]:加载在net上

相关命令:

1、get_:返回一组objects;使用echo返回objects的句柄

set_load 5 [get_ports addr_bus * ] * 是模式匹配里多个的意思,以addr_bus开头的n个port

set_load 6 [get_ports "Y??M Z"] ?是模式匹配里匹配前面字符0个或者1个的意思

如果不存在,返回empty_collection

2、all_*:

all_inputs

all_outputs

all_clocks

all_registers

3、 remove_from_collection

remove_from_collection [all_inputs] [get_ports CLK] #从所有inputs里去除CLK

add_to_collection $pci_ports [get_ports CTRL] #在pci_ports里添加CTRL

4、query_objects $pci_ports

query_objects $foo #得到集合的具体objects

5、sizeof_collection $pci_ports(大小)

6、echo

set foo [get_ports p*]

echo $foo #返回集合的句柄值

7、过滤器

filter_collection [get_cells ] "ref_name = ~AN "

get_cells *-filter “don’t_touch == true”

8、index_collection $pci_ports number

相当于求数组的某个number值

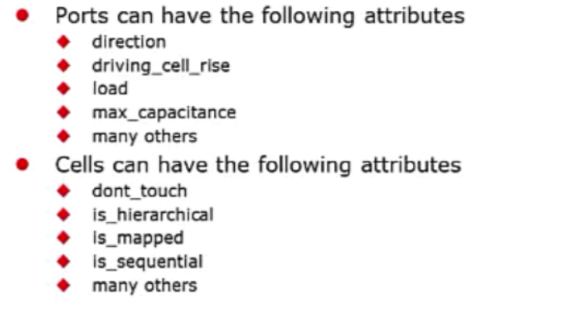

objects的属性:

基本时序约束:

1、分类:时钟的约束(寄存器与寄存器之间)、输入延时的约束、输出延时的约束

2、时序约束对电路的要求:

- 综合工具现在不能很好地支持异步电路,甚至不支持异步电路;

- single clock,single cycle,单个时钟,单延触发,不要一会posedge,一会negdege

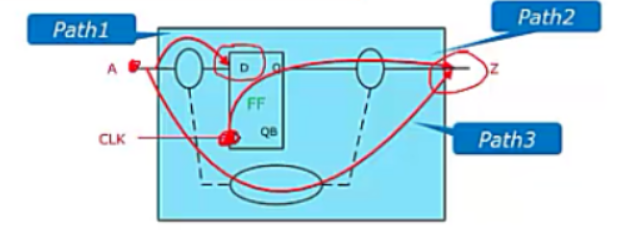

3、路径:

- 起点:输入端口(input port)、触发器或寄存器的时钟引脚

- 输出端口:输出端口、时序器件的除时钟引脚外的所有输入引脚

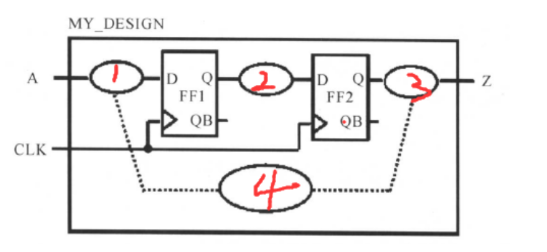

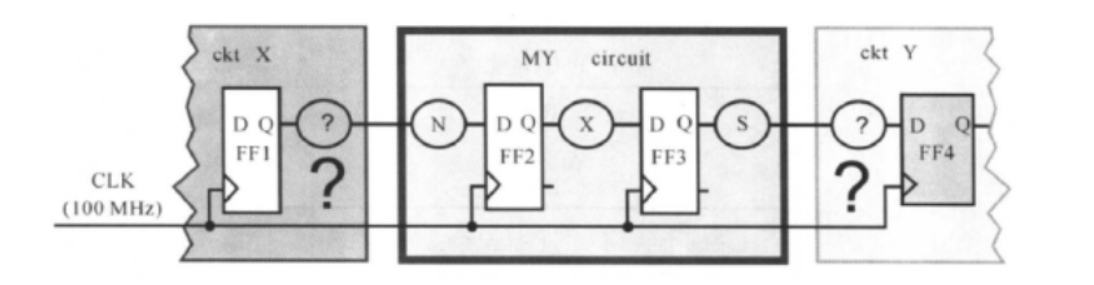

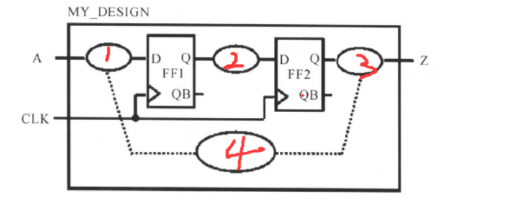

具有四条路径: - 从输入端口A到FF1的D端口

- 从时钟clk到FF2的D端口

- 从时钟clk到FF2的输出端口

- 从输入端口A到FF2的输出端口

路径的特性是存在延时,也就是说,路径1、2、3、4都存在有延时,延时最长的一条路径称为关键路径。

满足建立时间的约束:为了满足FF2建立时间的要求,数据从FF1的clk端口到达FF2的D端口+FF2的建立时间不能超过时钟周期,也就是说(触发器的翻转时间/转换延时、寄存器与寄存器之间的组合逻辑延时、连线延时这些种延时)不能过大。

满足保持时间的约束:也就是数据经过上面的延时(触发器的翻转时间/转换延时、寄存器与寄存器之间的组合逻辑延时、连线延时)之后到达FF2的D端的时间,不能小于某个值。也就是说,这些延时也不能太小。

(在0ns的时候,触发器有效沿到来,FF1和FF2都要更新下数据,FF1准备锁存高电平,FF2准备锁存低电平;由于FF1反应很快,电路延时很小,FF1寄存住的高电平很快就会传到FF2的D端口,高电平就会冲掉FF2要锁存的低电平(也就是FF2的D端口低电平还没有稳定,违反了保持时间),也就是说会导致低电平对FF2的保持时间不能得到满足,导致FF2更新数据失败,要锁存住的低电平可能就产生亚稳态)

所以,保持时间的分析比建立时间的分析提前一个时钟周期沿,也就是说在0ns时候传输数据,建立时间是在下一个时钟上升沿(20ns时刻)进行检查FF2的D端口数据是否稳定(若不稳定,就违反了建立时间),而保持时间是在发送数据的同一时刻(也就是0ns时刻)检查FF2的D端口数据是否稳定(如果不稳定,就违反了保持时间)

时钟约束

寄存器与寄存器间的延时小于时钟周期减去建立时间,即: path delay <= Clock Period - Tsetup

定义时钟周期的命令为:create_clock。例如:create_clock -period 10 [get_ports clk]

定义时钟时,必须定义时钟周期(-period)和时钟源(端口或引脚)也可以加上一些可选项(option)来定义时钟的占空因数(duty cycle),偏移(offset/skew)和时钟名( clock name)等(一旦定义好时钟,可以通过report_clock命令来查看所定义的时钟以及其属性,如果我们需要使用时钟的两个沿(上升沿和下降沿),时钟的占空因数将影响时序的约束)

需要再添加其他的时钟属性,在添加之前,需要知道时钟的偏移(skew)、抖动(jitter)、转换时间(transition)、延时(latency)这几个概念或者这几个时钟的属性。

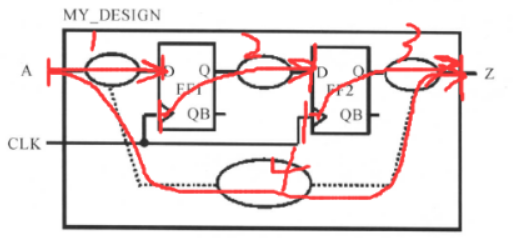

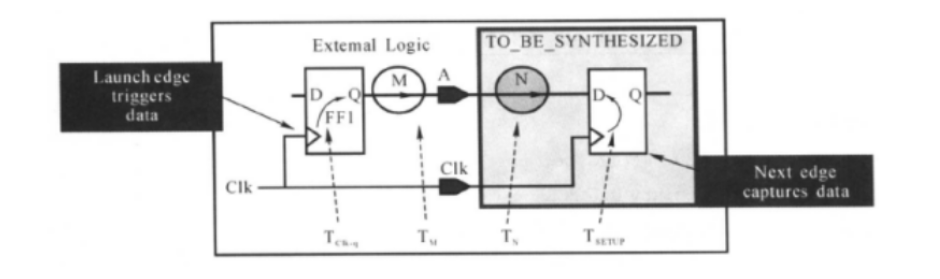

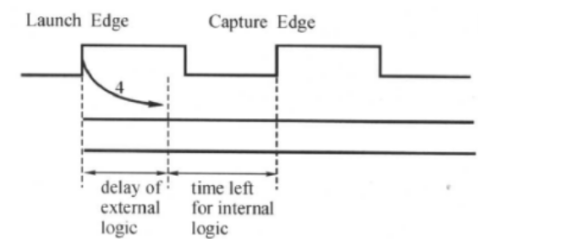

路径1:输入端口A到寄存器D端的约束

之前讨论前后使用的是同一个时钟CLK,如果使用不同时钟,那么约束就不同了。

如果Tn较大(Tn+Tsetup>Tclk-(Tclk-q+Tm)),那么DC就会进行优化,使Tn减少,如果Tn还是过大,DC就会报错。因此我们要进行输入端口的约束,告诉外部电路的延时是多少,以便DC约束输入的组合逻辑。

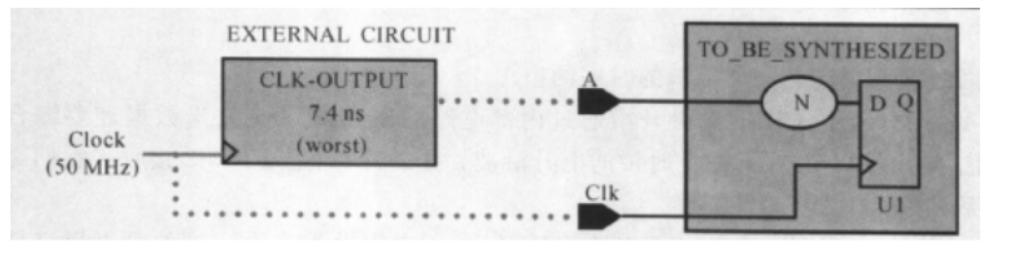

如果我们已知输入端口的外部延迟(假设为4 ns,包括翻转延时和外部的逻辑延时),就很容易计算出留给综合电路输入端到寄存器N的最大允许延迟。

DC中,用set_input_delay命令约束输入路径的延迟

set_input_delay -max 4 -clock CLK [get_ports A]

在这条命令中,外部逻辑用了4 ns,对于时钟周期为10 ns的电路,内部逻辑的最大延迟为10 - 4 - Tsetup = 6

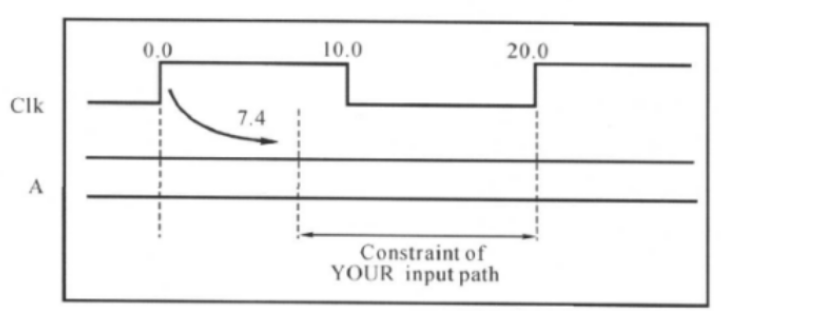

输入端口延时的约束为

creat_clock -period 20 [get_ports CLK]

set_input_delay -max 7.4 -clock CLK [get_ports A]

当有抖动和偏移的时候(假设不确定时间为U),如果触发器U1的建立时间为1ns,外部输入延时为D(包括前级寄存器翻转和组合逻辑的延时),则N逻辑允许的最大延迟S为:

20-D-U-1=S

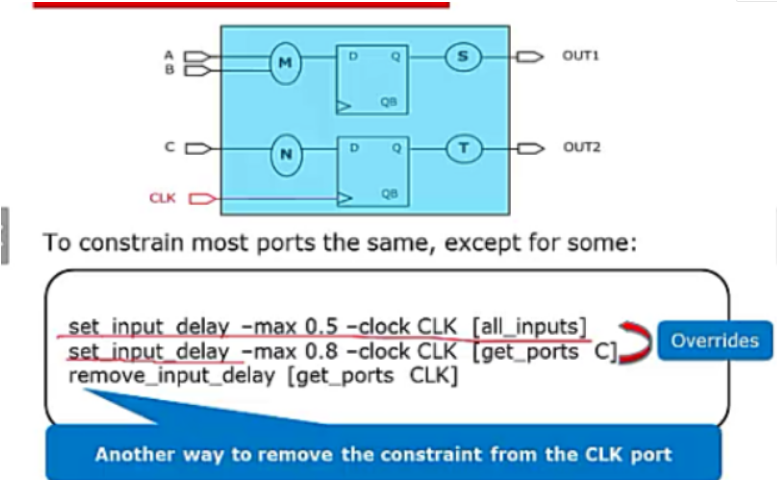

可以用下面命令对除时钟以外的所有输入端口设置约束:

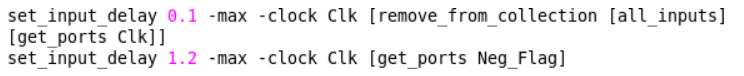

set_input_delay -max 3.5 -clock CLK [romove_from_collection [all_inputs] [get_ports CLK]];#表示从所有输入端口中除掉时钟CLK

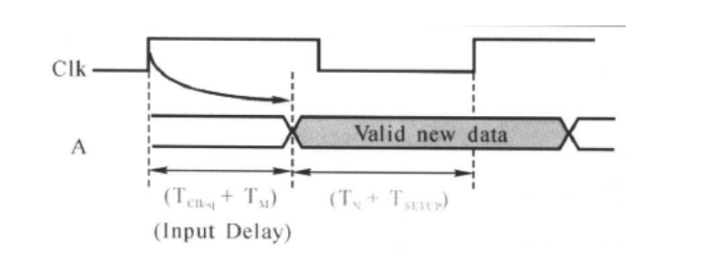

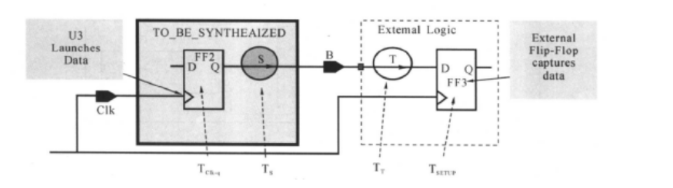

路径3:寄存器到输出端口的约束

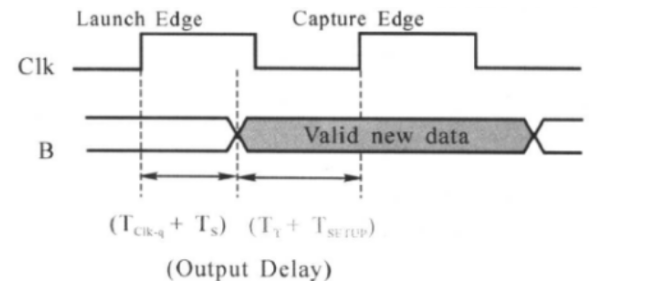

clk时钟上升沿通过内部电路的寄存器FF2发送数据经要综合的电路S,到达输出端口B,在下一个时钟的上升沿被到达外部寄存器的FF2接收。他们之间的时序关系如下图。

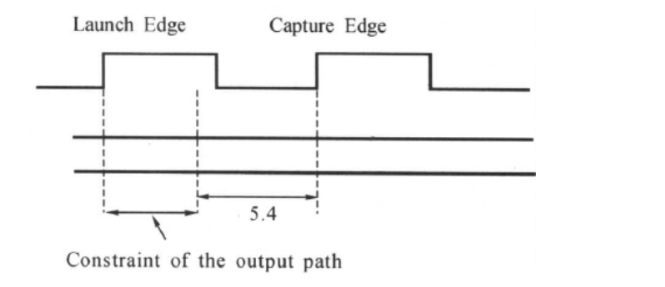

当我们已知外部电路的延迟(假设为5.4ns),就可以很容易计算出留给要综合电路输出端口的最大延迟

set_output_delay -max 5.4 -clock CLK [get_ports B]

内部逻辑最大延迟为:Tclk_q+Ts=Tclk-5.4

实际情况

进行SOC设计时,由于电路比较大,需要对设计进行划分,在一个设计团队中,每个设计者负责一个或几个模块。设计者往往并不知道每个模块的外部输入延迟和/或外部输出的建立要求

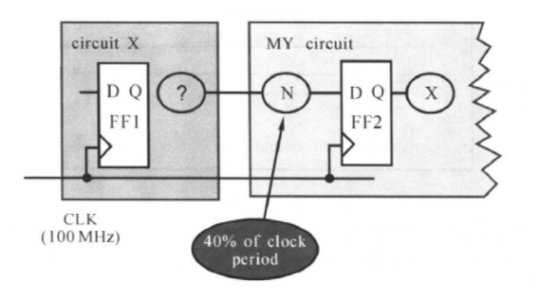

可以通过建立时间预算(Time Budget),为输入/输出端口设置时序的约束,也就是先预置这些延时:

DC要求我们对所有的时间路径作约束,而不应该在综合时还留有未加约束的路径。我们可以假设输人和输出的内部电路仅仅用了时钟周期的40%。如果设计中所有的模块都按这种假定设置对输人/输出进行约束,将还有20%时钟周期的时间作为富余量( Margin),富余量中包括寄存器FF1的延迟和FF2的建立时间,即:富余量=20%时钟周期 - Tclk-q - Tsetup

create_clock -period 10 [get-ports CLK]

set_input_delay -max 6 -clock CLK [all_inputs]

remove_input_delay [get ports CLK] ;#时钟不需要输入延迟的约束

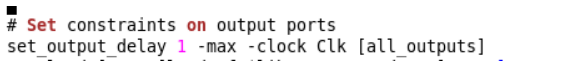

set_output_delay -max 4 -clock CLK [all-outputs]

路径4:组合逻辑的路径

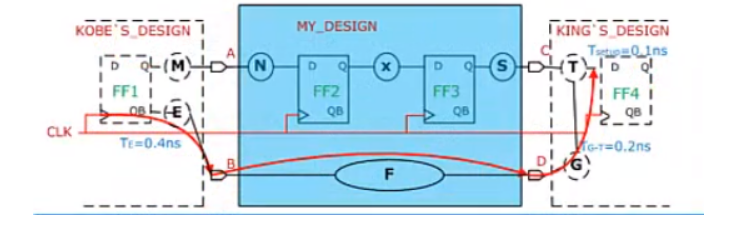

路径4是组合逻辑的路径,组合逻辑的约束可能需要虚拟时钟的概念。组合逻辑可能有两种中情况,一种是前面电路中的路径4:

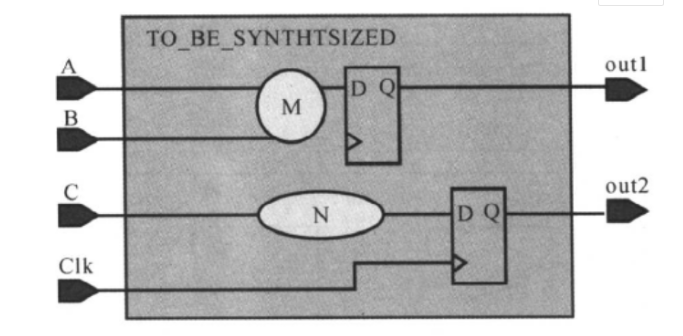

模块里面有输入端口到输出端口的组合逻辑外,也有时序逻辑,也就是模块里面有时钟,那么就可以对于路径4,就下面的电路模型进行约束:

组合逻辑部分F的延时Tf就等于时钟周期T-Tinput_delay-Toutput_delay,时钟周期减去两端,就得到了中间的延时约束了,对于上面的模型,可以这样约束为:

set_input_delay 0.4 -clock CLK -add_delay [get_ports B]

set_output_delay 0.2 -clock CLK -add_delay [get_ports D]

set_max_delay $CLK_PERIOD -from [get_ports B] -to [get_ports D]

另一种纯组合逻辑:

用到虚拟时钟的概念,create_clock -name VCLK -period 2 ;#指定一个虚拟时钟名称

当输入延时不同时,第二个输入延时命令会覆盖第一个输入延时命令

使用DC的步骤:

1、启动DC

list_designs ;#打开当前设计

remove_design -hierarchy;#移除设计

2、读verilog(analyze - elaborate)

analyze -format verilog ./rtl/TOP.v

elaborate architecture verilog TOP

3、检查设计

link

check_design

4、输入约束条件

- 在添加约束之前,使用reset_design清除前面存留的约束

- 添加时钟频率:create_clock -period 2 [get_ports Clk]

- 添加输入端口延时

- 添加输出端口延时

(若写的是脚本约束,检查语法命令:shell脚本下 dcprocheck ./script/file.con)

5、检查所有路径是否约束

check_timing

//出现error则有路径没有约束完

6、编译

compile

7、综合后的检查(检查不通过的需要优化,这里只作为一般流程,没有进行优化)

report_constraint -all (查看是否违规)

report_timing (查看时序报告)

report_area (查看面积情况)

时钟的约束:

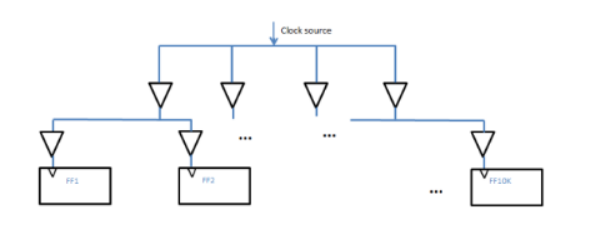

1、时钟树

全局时钟在芯片中的体现形式是时钟树(是个由许多缓冲单元(buffer cell)平衡搭建的时钟网状结构)

2、时钟属性

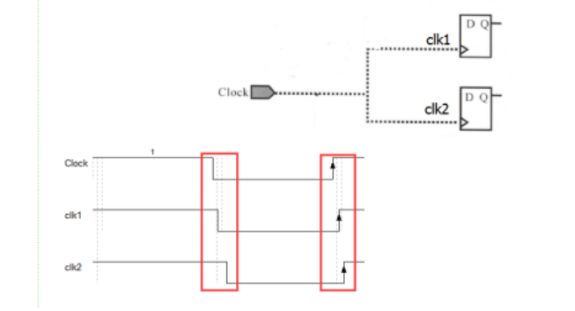

(1)时钟偏移(skew):时钟分支信号在到达寄存器的时钟端口过程中,都存在有线网等延时,由于延时,到达寄存器时钟端口的时钟信号存在有相位差,也就是不能保证每一个沿都对齐,这种差异称为时钟偏移(clock skew),也叫时钟偏斜。时钟的偏移如下图所示:此外,时钟skew与时钟频率并没有直接关系,skew与时钟线的长度及被时钟线驱动的时序单元的负载电容、个数有关。

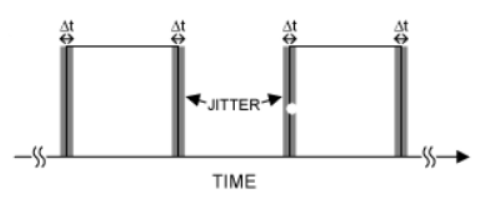

(2)时钟抖动(jitter):相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动

时钟的抖动可以分为随机抖动(Random Jitter,简称Rj)和固有抖动(Deterministic jitter):

- 随机抖动的来源为热噪声、Shot Noise和Flick Noise,与电子器件和半导体器件的电子和空穴特性有关,比如ECL工艺的PLL比TTL和CMOS工艺的PLL有更小的随机抖动;

- 固定抖动的来源为:开关电源噪声、串扰、电磁干扰等等,与电路的设计有关,可以通过优化设计来改善,比如选择合适的电源滤波方案、合理的PCB布局和布线。

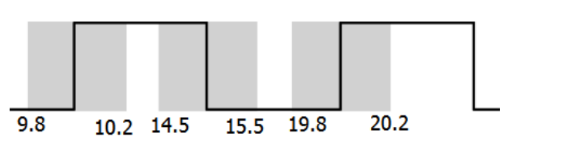

时钟的偏移和时钟的抖动都影响着时钟网络分枝的延迟差异(相位差异),在Design Compiler里面,我们用时钟的不确定性(uncertainty)来表示这两种情况的影响。

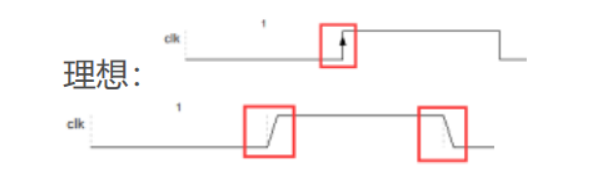

(3)时钟的转换时间(transition):时钟的上升沿跳变到下降沿或者时钟下降沿跳变到上升沿的时间,这个时间并不是如左下图所示那样完全没有跳变时钟的,而是像右下图那样,时钟沿的跳变时间就是时钟的转换时间

时钟的转换时间与与单元的延时时间(也就是器件特性)还有电容负载有关

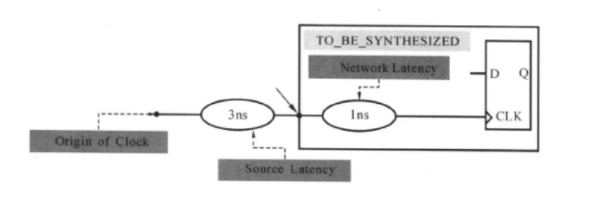

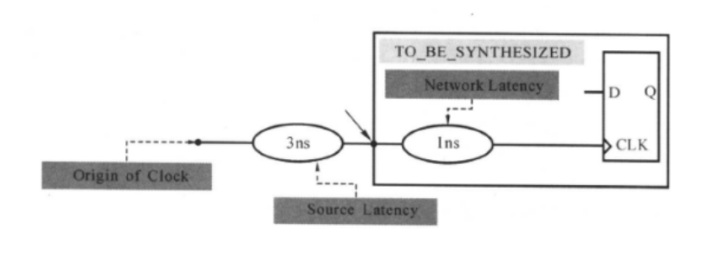

(4)时钟的延时(latency) :时钟从时钟源(比如说晶振)出发到达触发器时钟端口的延时,称为时钟的延时,包含时钟源延迟(source latency)和时钟网络的延迟(network latency)

时钟源延迟(clock source latency),也称为插入延迟(insertion delay),是时钟信号从其实际时钟原点到设计中时钟定义点(时钟的输入引脚)的传输时间,上图是3ns

时钟网络的延迟( clock network latency)是时钟信号从其定义的点(端口或引脚)到寄存器时钟引脚的传输,经过缓冲器和连线产生的延迟(latency),上图是1ns

时钟约束命令

create_clock、set_clock_uncertainty、set_clock_latency、set_clock_transition分别进行时钟的周期、偏移、延时、转换约束。

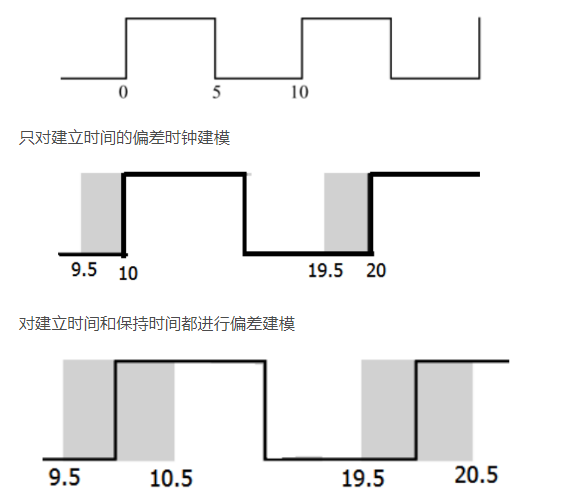

1、时钟偏差的建模

set_clock_uncertainty:对时钟的偏移与抖动进行建模,也就是对时钟的偏差进行建模。

create_clock -period 10 [get_ports CLK]

set_ clock_ uncertainty -setup 0.5 [get_clocks CLK]

在默认的情况下,“set-clock_uncertainty”命令如果不加开关选项“-setup”或“-hold”,那么该命令给时钟赋予相同的建立和保持偏差值。

除此之外,还可以对时钟的上升沿和下降沿进行偏差建模,比如上升沿的偏差是0.2ns,下降沿的偏差是0.5ns,则有:

set_ clock_ uncertainty -rise 0.2 -fall 0.5 [get_clocks CLK]

2、时钟转换时间的建模

由于时钟并不是理想的方波,用set_ clock_ transition来模拟时钟的转换(transition)时间。默认的上升转换时间为从电压的20%上升至80%的时间,下降的转换时间为从电压的80%下降至20%的时间。如果set_clock_transition命令中不加开关选项“-setup”或“-hold" ,那么该命令给时钟赋予相同的上升和下降转换时间。一般情况下,我们只约束最大的转换时间,如最大转换时间是0.2ns,那么就加上-max选项:

set_clock_transition -max 0.2 [get_clocks CLK]

3、时钟延迟的建模

一般情况下,我们把时钟源延迟(source latency)和时钟网络的延迟(network latency)分开来,因为时钟源延时需要建模,是因为DC是真的不知道这延时是多大,但是对于时钟网络的延迟,DC在布局布线前不知道,但是在布局布线后就可以计算出来时钟网络的延时了,因此在布局布线之后进行综合时,就没有必要对时钟网络进行延时,因此就要把这两个延时分开来进行约束。

布局布线之前:时钟周期为10ns,时钟源到芯片的时钟端口时间是3ns,时钟端口都内部触发器的时间是1ns,如下图所示

create_clock -period 10 [get-ports CLK]

set_clock_latency -source 3 [get_clocks CLK]

set_clock_latency 1 [get_clocks CLK]

布局布线之后:就可以计算实际的线网延时,就要使用

set_propagated_clock [ get_clocks CLK]

set_clock_latency 1 [get_clocks CLK]

最后

以上就是谨慎镜子最近收集整理的关于DC学习(时序分析和命令)的全部内容,更多相关DC学习(时序分析和命令)内容请搜索靠谱客的其他文章。

发表评论 取消回复