为了确保有精确的静态时序分析结果,我们必须制定所有的时钟和相关联的时钟的参数。TimeQuest analyzer支持标准的SDC命令,他可以提供各种时钟参数的设置。

TimeQuest analyzer支持一下类型时钟的约束:

1、基础时钟——也就是输入时钟;

2、虚拟时钟——用于做IO约束;

3、多周期时钟;

4、生成时钟;

时钟为同步传输指定时序上的需求,并且指导布线优化算法来达到最佳布线结果。在.sdc文件中应该首先指定clock约束,因为其他的约束会以定义的时钟来作为参考,TimeQuest analyzer读取SDC文件的顺序是从上到下;

创建base clock

base clock 是器件的最前端的输入时钟,她不像PLL时钟产生自期间的内部,她有片外晶振或者片外的前级芯片输入,他应该最先被约束。

从register、Port、pin、来创建时钟约束,采用create_clock命令,一些例程如下:

create_clock -period 10 -waveform { 2.5 7.5 } [get_ports clk_sys]

create_clock -period 10 -name clk_sys [get_ports clk_sys]

create_clock命令的的target经常是一个一个管脚,一般使用get_ports命令,如下:

create_clock -period 10 -name clk_sys [get_ports clk_sys]

可以选用-add选项在同一个时钟节点上增加多个时钟约束设置,如下设置中,两个晶体驱动了同样的时钟port:

create_clock -period 10 -name clk_100 [get_ports clk_sys]

create_clock -period 5 -name clk_200 [get_ports clk_sys] -add

创建virtual clock

设计中的virtual clock一般是指一些没有真正时钟源的时钟,或者作为时钟但没有影响设计(that does not interact directly with the design),虚拟时钟一般用于IO约束,他们反映了连接在FPGA外部,前级和后级的芯片的时钟(因为这些芯片的产生的数据送给了FPGA,或者FPGA产生的数据送给了芯片)。

创建虚拟时钟使用create_clock命令,这个命令不用指定<targets>,因为是虚拟的。使用虚拟时钟作为set_input_delay和 set_output_delay约束的参考。

下面为一个参考实例:

create_clock -period 10 -name my_virt_clk

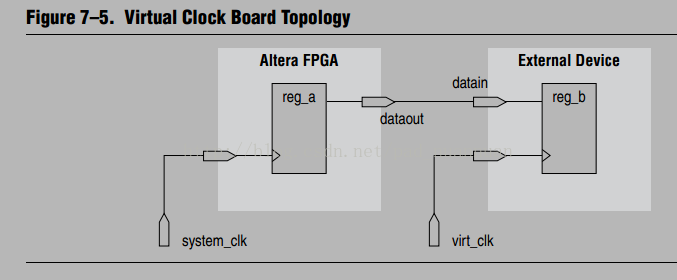

下图表明TimeQuest analyzer的确需要一个virtual clock来恰当的分析外部中的寄存器和内部器件中的寄存器之间的关系;如下图,因为晶振、virt_clk和FPGA并没有相互影响,但它却作为外部期间的寄存器时钟源,所以我们必须把它定义为一个虚拟时钟,在你创建了虚拟时钟后,就可以做外部器件和内部期间的寄存器间分析。

下面的命令创建一个10ns,占空比50%的virtual clock,他的第一个时钟上升沿发生在0ns处:

#create base clock for the design

create_clock -period 5 [get_ports system_clk]

#create the virtual clock for the external register

create_clock -period 10 -name virt_clk

#set the output delay referencing the virtual clock

set_output_delay -clock virt_clk -max 1.5 [get_ports dataout] #创建最大输出延时

set_output_delay -clock virt_clk -min 0.0 [get_ports dataout] #创建最小输出延时

IO接口的不确定

Virtual clocks are recommended for I/O constraints because the derive_clock_uncertainty command can add different un certainty values on clocks that interface with an external I/O port than uncertainty values between register paths fed by a clock inside the FPGA.

指定IO接口的不确定性,必须创建一个virtual clock,并进行输入和输出约束:以virtual clock作为参考,使用set_input_delay和set_output_delay命令。当set_input_delay和set_output_delay以FPGA的时钟输入或者PLL的输出作为参考时,derive_clock_uncertainty命令可以为内部时钟和IO接口时钟设置不同的时钟不确定性。

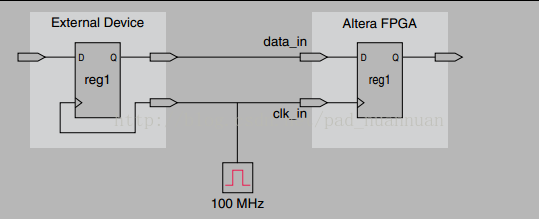

下面的这个例程更能代表虚拟时钟的用处:FPGA和外部芯片使用相同的时钟源。

100Mhz的晶振驱动外部芯片输出数据,同时又驱动FPGA接受数据,此时对于 输入端做端口input约束就很有现实意义。

# Create the base clock for the clock port

create_clock -period 10 -name clk_in [get_ports clk_in]

# Create a virtual clock with the same properties of the base clock driving the source register

create_clock -period 10 -name virt_clk_in

# Create the input delay referencing the virtual clock and not the base clock

set_input_delay -clock virt_clk_in <delay value> [get_ports data_in]

此处约束,ALTERA的官方手册特别强调不能使用clk_in,想想也是,data_in的数据来自于前级的器件,前级的驱动时钟在我们的本次约束中可定不是clk_in ,而是我们专门为它而创建的虚拟时钟。

创建多周期时钟约束

如果在我们的设计中,一个引脚上存在多个频率的时钟输入(额外的是一个低功耗时钟,频率较正常工作的频率要低),那么就必须创建一个多周期的时钟约束。

命令在于一个关键自 -add,如下:

create_clock –period 10 –name clock_primary –waveform { 0 5 } [get_ports clk]

create_clock –period 15 –name clock_secondary –waveform { 0 7.5 } [get_ports clk] -add

创建生成时钟

什么样的时钟是适合做生成时钟约束呢?PLL时钟输出,或者通过寄存器(计数器)分频得到的时钟。

如果我们的设计中的某个node存在多个周期的时钟,同时这个node又作为生成时钟的时钟源,那么此时我们就应该根据不同的源时钟定义多个生成时钟,每一个生成时钟对应一个基本的时钟。

对于PLL产生的生成时钟,可以使用一句命令进行约束—— derive_pll_clocks

自动检测时钟和创建默认的时钟约束:

如果设计中没有时钟约束,那么将会给所有检测到的时钟node创建一个默认的时钟约束;但是考虑这样一种情况:如果你的设计中有两个时钟,而你对其中的一个做了约束,那么工具不会对另一个创建默认的时钟约束。(必须是都没有创建的情况下才)。

自动创建时钟约束使用这样的一个命令:derive_clocks。不过它使用所有的时钟都约束为同一个时钟频率(引起想要较好的指导工具优化你的设计,那么请对每个时钟都进行独立的分析约束)。

创建时钟组:

TQ默认认为所有的时钟都是相关的。如果你想要指定设计中的时钟是独立的,并且是异步的,那么需要使用set_clock_group命令,这个命令有两个参数:-exclusive和-asynchronous

-exclusive

表明这两个时钟是不同时存在,例如某个port上会存在两个时钟(物理上他们不会同时存在),25Mhz和50Mhz,那么使用这个命令表明他们是不同时存在的。

例如如下:

create_clock -period 40 -name clk_A [get_ports {port_A}]

create_clock -add -period 20 -name clk_B [get_ports {port_A}]

set_clock_groups -exclusive -group {clk_A} -group {clk_B}

-asynchronous:

这个命令表明任何一个组和另一个组都是异步的,同一个组内的时钟都是同步的。

set_clock_groups -asynchronous -group {clk_A clk_B} -group {clk_C}

一些影响时钟的关键因素:

Clock Latency(时钟延迟)

使用TimeQuest analyzer创建的时钟都是理想时钟,没有考虑到板上的影响,可以通过指定clock latency和clock uncertainty来指定这种时钟上的影响。

clock latency包括两个方面,时钟源延迟和时钟网络延迟;时钟源延迟是指从时钟发出的点(晶振)到FPGA的时钟引脚处的传播延迟。时钟网络延迟是指从FPGA的时钟引脚处到寄存器的时钟引脚处的传播延迟。总的时钟延迟是上述两种延迟的综合。对FPGA的时钟引脚做时钟源传播延迟设置使用set_clock_latency命令。TimeQuest analyzer会自动计算出时钟网络延迟。

clock uncertainty(时钟不确定性)

最后

以上就是神勇衬衫最近收集整理的关于quartus时序分析文档理解与翻译(3) ——创建时钟和时钟约束的全部内容,更多相关quartus时序分析文档理解与翻译(3)内容请搜索靠谱客的其他文章。

发表评论 取消回复