简单的one-hot 状态机转换

- one-hot 编码

- verilog中写法

one-hot 编码

0001 0010 0100 1000

如上例每次只有1个bit位置high其余low的状态叫one-hot,相反只有1个bit low 其余bit high 叫 one-cold。

verilog中写法

一般状态机转换中我们会先

paremeter A = 0001, B = 0010, C = 0100, D = 1000;

像这样预设值,这里介绍一种新的方法,

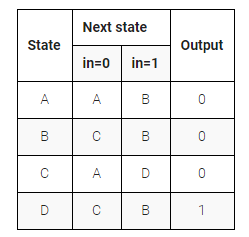

如上图的变化,如果state想变到 A状态的话有2种方式,一是从A in=0,二是 C in=0。所以等式可以写成A: next_state[0] = state[0]&(~in) | state[2]&(~in)。 这种形式相较于传统的状态机转换要简单很多,这种形式叫做“drive equation by inspection”。

module top_module(

input in,

input [3:0] state,

output [3:0] next_state,

output out); //

parameter A=0, B=1, C=2, D=3;

// State transition logic: Derive an equation for each state flip-flop.

assign next_state[A] = state[A] & ~in | state[C] & ~in;

assign next_state[B] = state[A] & in | state[B] & in | state[D] & in;

assign next_state[C] = state[B] & ~in | state[D] & ~in;

assign next_state[D] = state[C] & in;

// Output logic:

assign out = state[D];

endmodul

因为one hot 只有1位是高电位,利于判断具有速度快的优势,但是会消耗更多寄存器资源,相应减少组合逻辑资源。就相当于已经译码过的3-8译码器。

对于Gary 格雷码来说 每次只变动一个bit的值,是最节省功耗的方法。

所以在选择采用那种状态机的时候,如果状态比较少就采用one-hot,而如果状态较多就采用格雷码来节省功耗。

最后

以上就是自由小蚂蚁最近收集整理的关于verilog中简单的one-hot 状态机转换one-hot 编码verilog中写法的全部内容,更多相关verilog中简单的one-hot内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

![[从零开始学习FPGA编程-36]:进阶篇 - 基本时序电路-有限状态机简述(数字电路描述)=》Moore 型、Mealy 型](https://www.shuijiaxian.com/files_image/reation/bcimg17.png)

发表评论 取消回复