数字IC设计——用Verilog实现序列检测器(有限状态机)

序列检测器在数据通讯,雷达和遥测等领域中用与检测步识别标志。它是一种用来检测一组或多组序列信号的电路。例如检测器收到一组串行码{1110010}后,输出标志1,否则,输出0。

一、“101” 序列检测器

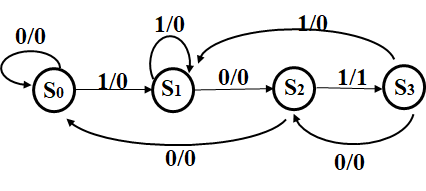

序列检测器:有“101”序列输入时输出为1,其他输入情况下,输出为0。画出状态转移图,并用Verilog描述。

- 先分析输入序列时,产生的结果

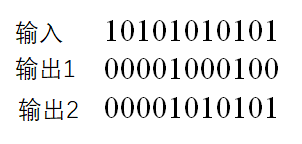

序列检测器就是将一个指定序列从数字码流中识别出来。本例中将设计一个“101”序列的检测器。设X为数字码流的输入,Z为检测出标记输出,高电平表示发现指定的序列101.考虑码流为10101010101…则

| 时钟 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 输入X | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| 输出Z | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

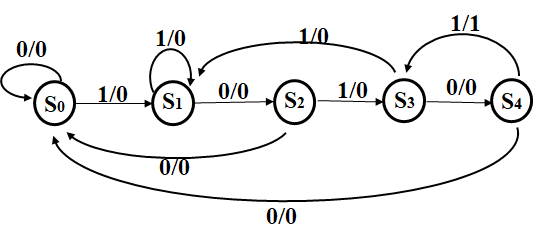

- 将上述功能转化为状态转移图:

- 用Verilog语言描述状态机

module Detect_101(

input clk,

input rst_n,

input data,

output flag_101

);

parameter S0 = 0,

S1 = 1,

S2 = 2,

S3 = 3;

reg [1:0] state;

always @(posedge clk or negedge rst_n)begin

if(rst_n == 1'b0)begin

state <= S0;

end

else begin

case(state)

S0:

if(data == 1)

state <= S1;

else

state <= S0;

S1:

if(data == 0)

state <= S2;

else

state <= S1;

S2:

if(data == 1)

state <= S3;

else

state <= S0;

S3:

if(data == 1)

state <= S1;

else

state <= S2;

default:

state <=S0;

endcase

end

end

assign flag_101 = (state == S3)? 1'b1: 1'b0;

endmodule

采用三段式状态机将时序逻辑和组合逻辑分开,把状态和输出单独列开,方便检查和维护。可以写成如下:

module Detect_101(

input clk,

input rst_n,

input data,

output flag_101

);

parameter S0 = 0,

S1 = 1,

S2 = 2,

S3 = 3;

reg [1:0] state;

reg [1:0] next_state;

wire flag_101;

always @(posedge clk or negedge rst_n) begin

if (! rst_n)

state <= S0;

else

state <= next_state;

end

always @(*)begin

case(state)

S0:

next_state = (data) ? S1:S0;

S1:

next_state = (data) ? S1:S2;

S2:

next_state = (data) ? S3:S0;

S3:

next_state = (data) ? S1:S2;

default:

state = S0;

endcase

end

always @(*)begin

if (! rst_n)

flag_101 = 1'b0;

else if (state == S3)

flag_101 = 1'b1;

else

flag_101 = 1'b0;

end

endmodule

- 需要注意的地方

由于对于 有“101”序列输入时输出为1,其他输入情况下,输出为0。

在画状态转移图的时候,只要有101的序列输出就会输出为1

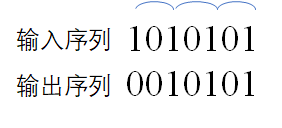

但是有时会出现如下情况,即输出完101序列后,状态机又回到初始状态重新检测101序列:

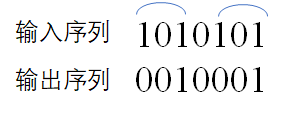

因此状态转移又会发生变化:

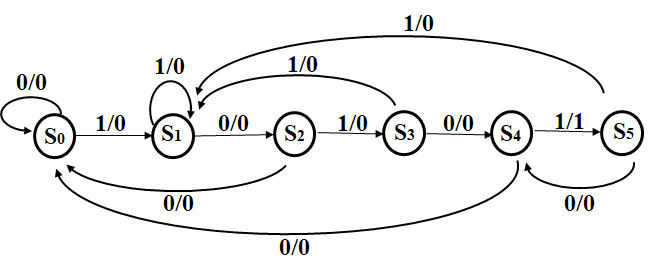

二、“10101” 序列检测器

分析这个序列的状态转移图时,当状态机的个数,状态转移发生变化时,也会有不同的结果:

- 当有五个状态机时,有如下两种状态转移图:

2. 在设计状态机时,应注意合理选择状态机数量,以及状态转移的路径。

三、序列检测器设计的思路步骤

总统设计思路:

1.列出检测器的逻辑功能

2.画出状态图,注意多余的状态图。

3.设计代码

4.写测试代码

5.时序仿真

最后

以上就是安静发箍最近收集整理的关于数字IC设计——用Verilog实现序列检测器(有限状态机FSM)的全部内容,更多相关数字IC设计——用Verilog实现序列检测器(有限状态机FSM)内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

![[从零开始学习FPGA编程-36]:进阶篇 - 基本时序电路-有限状态机简述(数字电路描述)=》Moore 型、Mealy 型](https://www.shuijiaxian.com/files_image/reation/bcimg17.png)

发表评论 取消回复