题目

描述

实现一个深度为8,位宽为4bit的ROM,数据初始化为0,2,4,6,8,10,12,14。可以通过输入地址addr,输出相应的数据data。

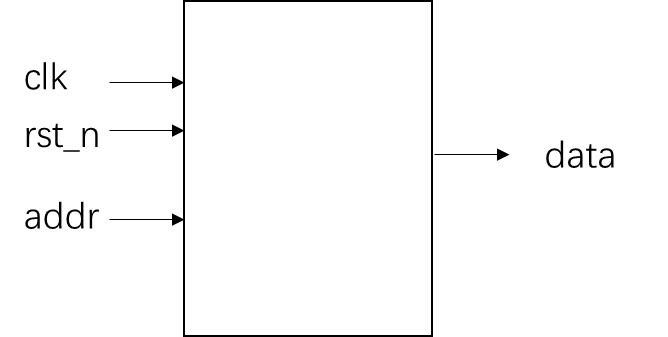

接口信号图如下:

使用Verilog HDL实现以上功能并编写testbench验证。

输入描述:

clk:系统时钟

rst_n:异步复位信号,低电平有效

addr:8bit位宽的无符号数,输入到ROM的地址

输出描述:

data:4bit位宽的无符号数,从ROM中读出的数据

题解

`timescale 1ns/1ns

module 最后

以上就是拼搏人生最近收集整理的关于【校招Verilog快速入门】时序逻辑篇:VL23、ROM的简单实现题目题解的全部内容,更多相关【校招Verilog快速入门】时序逻辑篇:VL23、ROM内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

![[从零开始学习FPGA编程-36]:进阶篇 - 基本时序电路-有限状态机简述(数字电路描述)=》Moore 型、Mealy 型](https://www.shuijiaxian.com/files_image/reation/bcimg17.png)

![[从零开始学习FPGA编程-33]:进阶篇 - 基本时序电路-寄存器(Verilog语言)](https://www.shuijiaxian.com/files_image/reation/bcimg23.png)

发表评论 取消回复