前言

学习说明此文档为本人的学习笔记,注重实践,关于理论部分会给出相应的学习链接。

学习视频:是根据野火FPGA视频教程——第十一讲

https://www.bilibili.com/video/BV1nQ4y1Z7zN?p=3

学习资料:《数字电子技术基础》清华大学出版社

理论学习

相关数字电路基础理论学习请参考本人的另一个笔记,可以让你深刻理解相关知识。

《数字电子技术基础》6.3 时序逻辑电路——寄存器和计数器功能介绍_追逐者-桥的博客-CSDN博客寄存器和移位寄存器、计数器功能介绍https://blog.csdn.net/ARM_qiao/article/details/124415549

实战演练

一、设计规划

1.1 实验(项目)目标

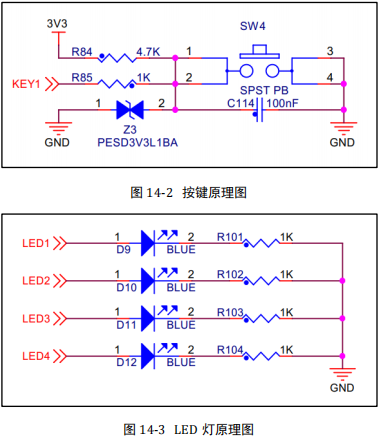

使用D触发器来控制LED灯,当按键未按下时led灯处于点亮状态;当按键被按下时led灯熄灭。

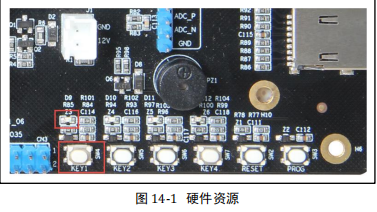

1.2 硬件资源:

二、程序设计

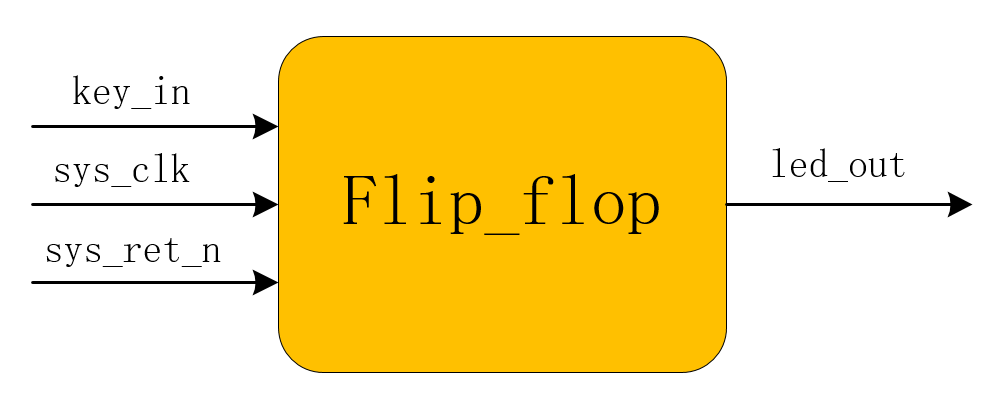

2.1 模块框图及波形图

| 输入输出信号描述 | |||

| 信号 | 位宽 | 类型 | 功能描述 |

| sys_clk | 1bit | input | 工作时钟信号,频率50MHz |

| sys_ret_n | 1bit | input | 复位信号,低电平有效 |

| key_in | 1bit | input | 按键输入信号 |

| led_out | 1bit | output | 输出控制LED灯 |

2.2 代码编写

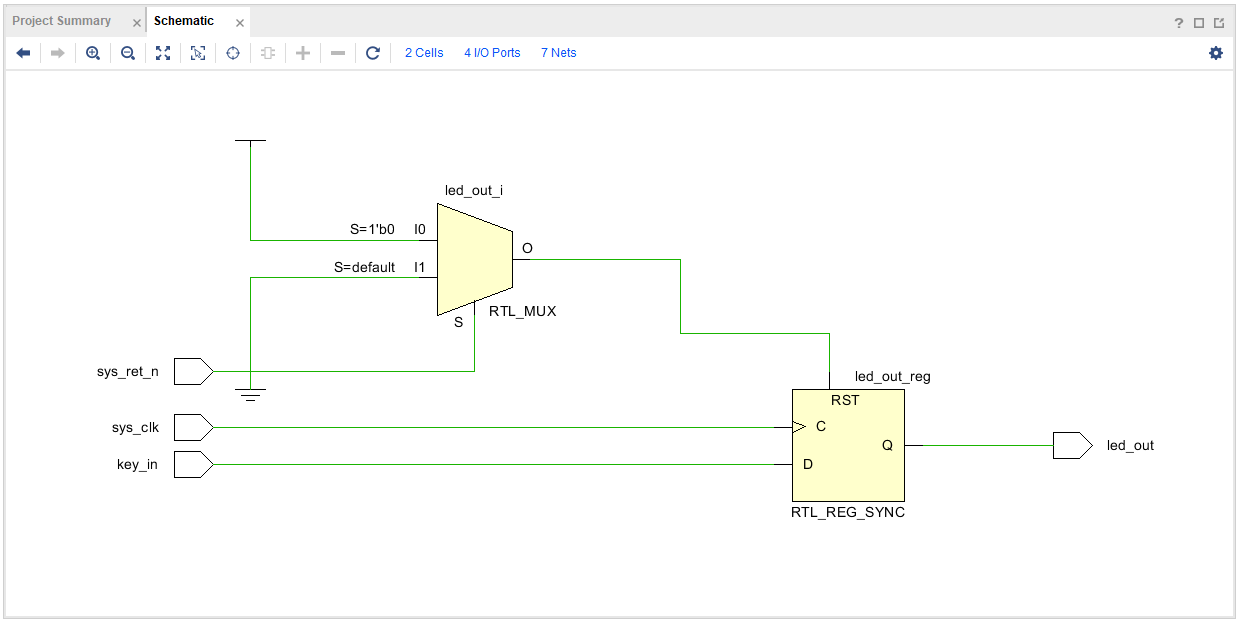

同步时序电路:

`timescale 1ns / 1ps

//

// Company: 追逐者——桥的小作坊

// Engineer:

//

// Create Date: 2022/04/25 09:23:40

// Design Name: D触发器实现按键控制LED

// Module Name: counter4

// Project Name:

// Target Devices:

// Tool Versions: Vivado 2018_3

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:视频学习代码

//

//

module flip_flop(

input wire sys_clk, sys_ret_n, key_in,

output reg led_out

);

always@(posedge sys_clk)

if(sys_ret_n == 1'b0)

led_out <= 1'b0;

else

led_out <= key_in;

endmoduleRTL视图

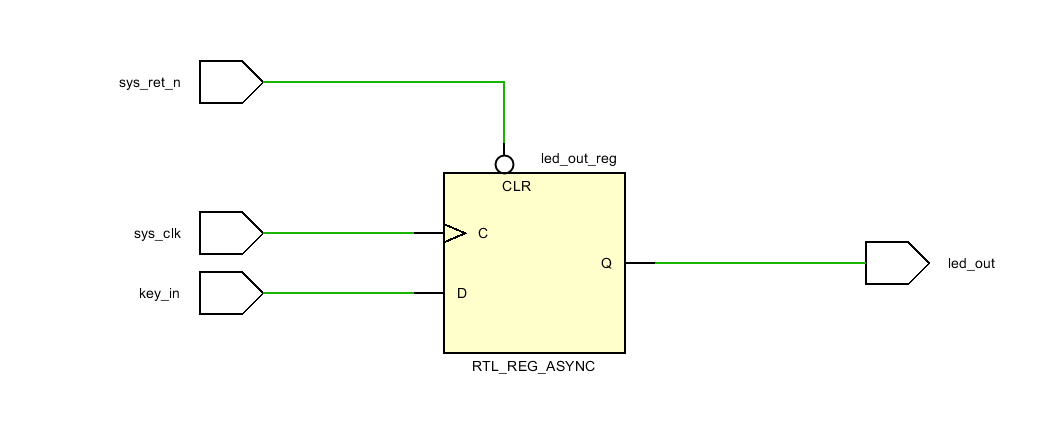

异步时序逻辑电路

module flip_flop(

input wire sys_clk, sys_ret_n, key_in,

output reg led_out

);

always@(posedge sys_clk or negedge sys_ret_n) //添加条件

if(sys_ret_n == 1'b0)

led_out <= 1'b0;

else

led_out <= key_in;

endmodule

三、逻辑仿真

3.1 仿真文件的编写

`timescale 1ns / 1ns

//

// Company: 追逐者——桥的小作坊

// Engineer:

//

// Create Date: 2022/04/25 09:23:40

// Design Name: D触发器实现按键控制LED

// Module Name: counter4

// Project Name:

// Target Devices:

// Tool Versions: Vivado 2018_3

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:视频学习代码

//

//

module tb_flip_flop();

reg sys_clk, sys_ret_n, key_in;

wire led_out;

initial begin

sys_clk = 1'b1;

sys_ret_n <= 1'b0;

key_in <= 1'b0;

#20

sys_ret_n <= 1'b1;

#210

sys_ret_n <= 1'b0;

#40

sys_ret_n <= 1'b1;

end

always #10 sys_clk = ~sys_clk; //模拟时钟,没10ns电平翻转一次,周期20ns,频率50MHz

always #20 key_in <= {$random} % 2;

initial begin

$timeformat(-9, 0, "ns", 6);

$monitor("@time %t:key_in=%b, led_out=%b", $time, key_in, led_out);

end

flip_flop ff_inst(sys_clk, sys_ret_n, key_in, led_out);

endmodule

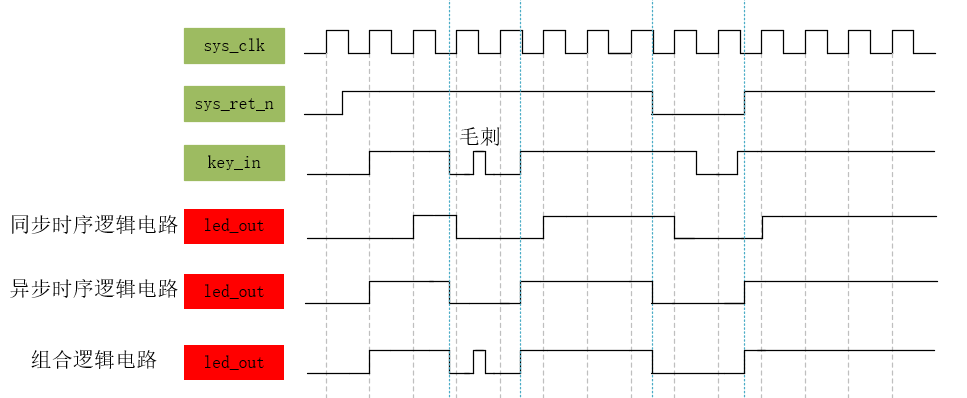

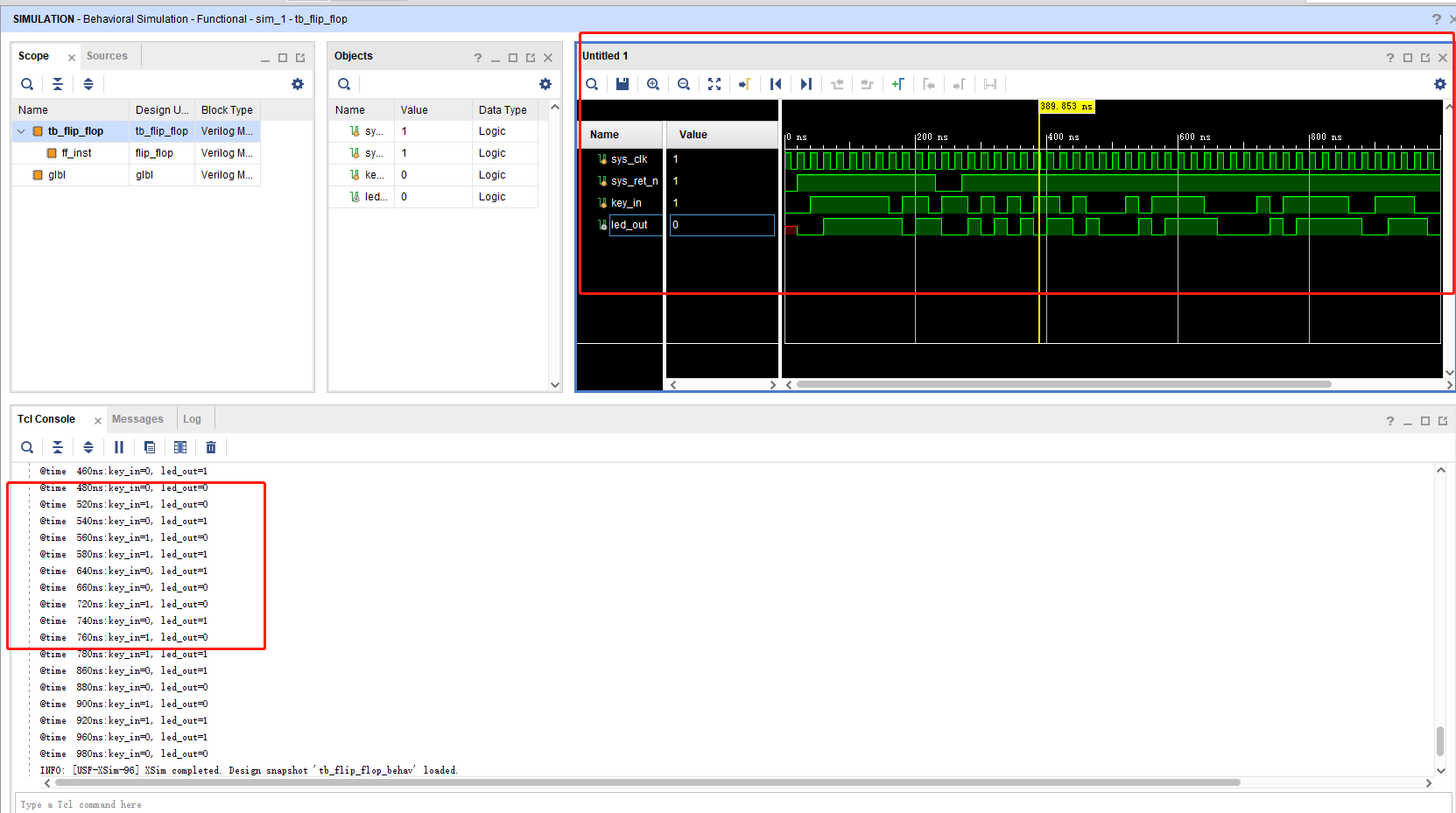

3.2 仿真波形图对比

从仿真图与波形图对比发现,输出未正常同步时序电路控制。

四、上板验证

请参考之前按键控制LED灯的实战:

二、3【FPGA】如何点亮LED灯_追逐者-桥的博客-CSDN博客FPGA开发 按键控制LED灯的亮灭Xilinx Artix7https://blog.csdn.net/ARM_qiao/article/details/123969251

最后

以上就是大方小懒虫最近收集整理的关于二、9【FPGA】时序逻辑电路——寄存器前言理论学习实战演练的全部内容,更多相关二、9【FPGA】时序逻辑电路——寄存器前言理论学习实战演练内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复