疑惑:什么是时序逻辑会延迟组合逻辑一拍?如何理解该现象?当数据变化沿与寄存器时钟上升沿重合时,寄存器输出信号是什么?

结论:

- DFF有输入端(D端)和输出端(Q端),D端连接部分组合电路,其值随组合电路的输入值同步变化;

- 所谓“延迟一拍”是指当时钟上升沿来临时,D端数据会传送到Q端,即Q值相较于D值会延迟一拍;

- 当数据变化沿与寄存器时钟上升沿重合时,可看作D端数据先变化,随即再将值传给Q端,即波形图显示的是寄存器输出(Q)为信号跳变沿后的值,如图4;

- 寄存器之间的延迟,即每经过一个DFF,就会增加一个时钟周期的延迟。

说明:

一、组合逻辑VS时序逻辑

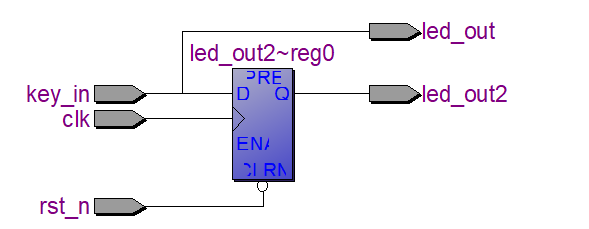

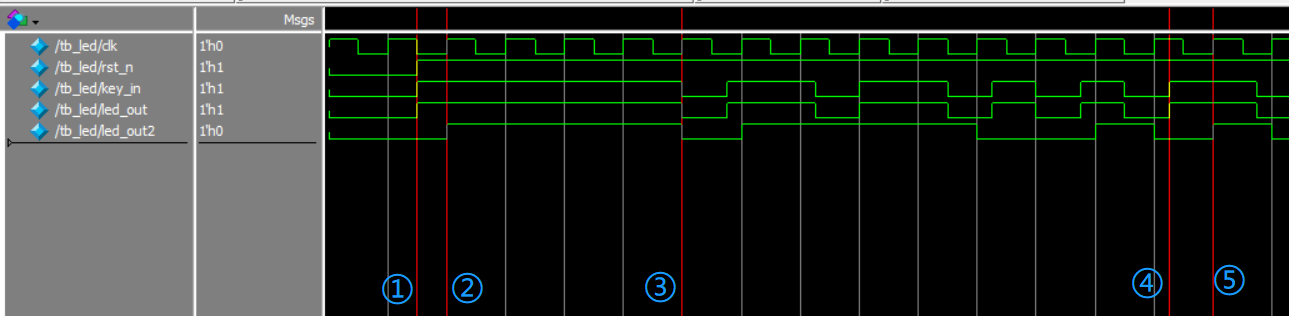

如图1所示,led_out直接与key_in相连,led_out2与key_in之间有DFF,输出信号的波形如图2所示。①②处和④⑤处,led_out2延迟led_out;但在③处key_in的变化与clk上升沿重合时,led_out2与led_out的变化同步。该过程可以看作,DFF的D端随key_in随时同步变化(组合电路),但只有在clk上升沿时才将D端值(led_out)赋给Q端(led_out2),跳变沿重合时可看作因为组合逻辑D端值马上变化,再传输到Q端。

结论:led_out2最多延迟led_out一个时钟周期,在仿真中也可能同步

图1

图2

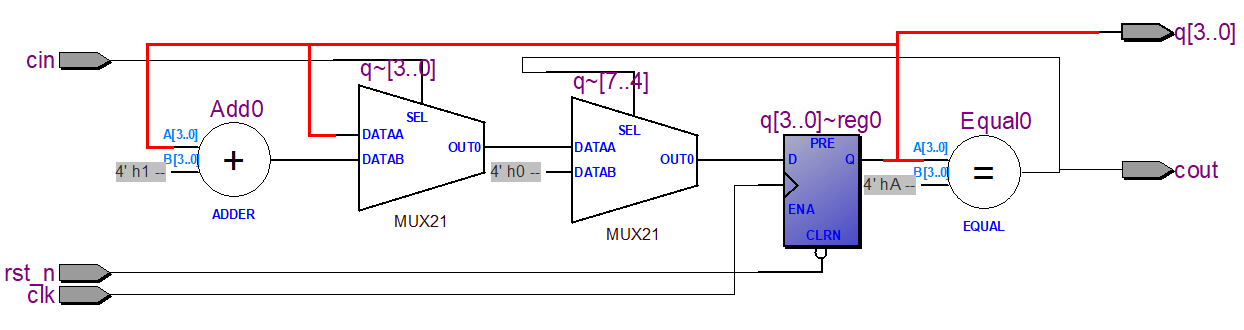

二、4bit计数器,当计数使能cin与clk上升沿同时到达时的情况

如下代码:

else if(cin == 1'b1)

q <= q + 1'b1;

完整代码见文末

仿真环境:Modelsim SE-64 10.5

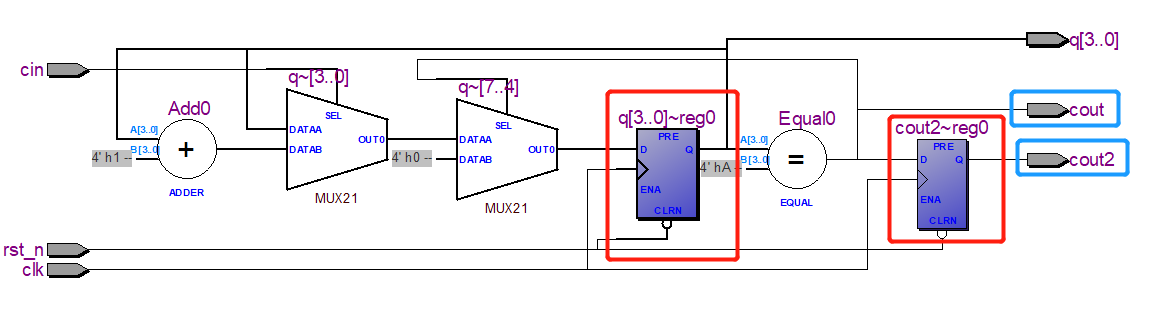

图3 counter_4bit 的电路

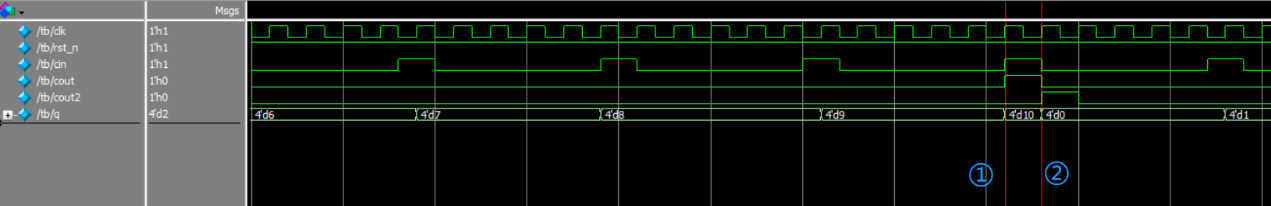

图4 仿真波形图

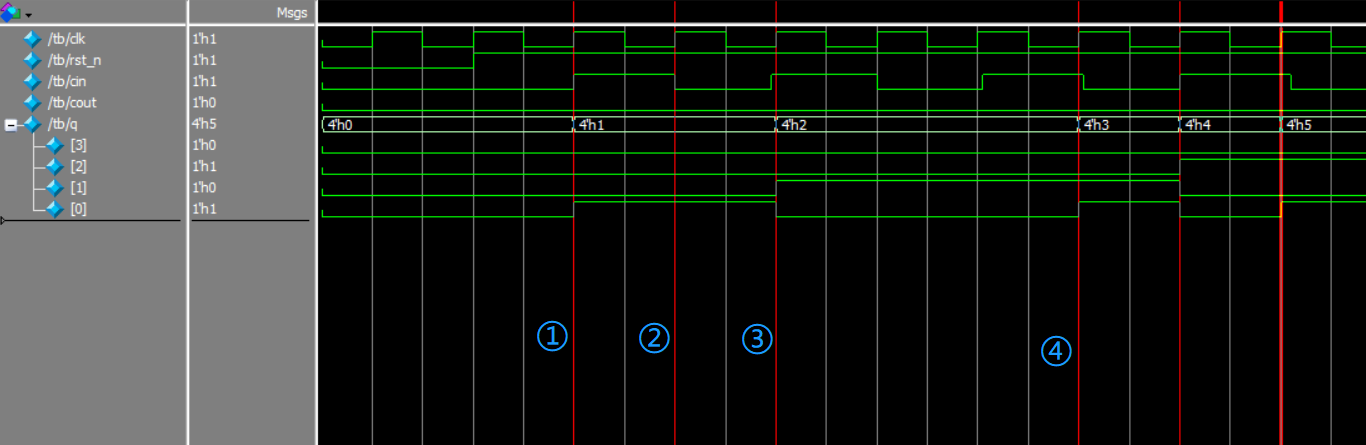

如图4所示,当cin的变化与时钟上升沿重合时(①②处),q在①处“加1”,但在②处“不变”。即重合时,捕获到的是cin“下一时刻”的值;不重合时,捕获到的是当前时刻的值。

三、DFF之间的数据延迟

在上述计数器中再加入一个DFF2,cout2会延迟cout一个时钟周期,如图6.

图5

图6

当DFF2的D端连接的是DFF1的Q端时,因为DFF总是在时钟上升沿传送数据,所以在此刻DFF2的Q值是上一时刻DFF1的Q值,即DFF2的输出值相较于DFF1的输出值,延迟一个时钟周期。

counter_4bit

RTL:

module counter_4bit

#( parameter c_number = 4'd10 )

(

input clk ,

input rst_n ,

input cin ,

output reg cout ,

output reg cout2 ,

output reg[3:0] q

);

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

q <= 4'd0 ;

else if(q == c_number)

q <= 4'd0 ;

else if(cin == 1'b1)

q <= q+1'b1;

else q <= q;

end

always@(*) begin

if(q == c_number)

cout <= 1'b1;

else cout <= 1'b0;

end

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

cout2 <= 1'd0 ;

else if(q == c_number)

cout2 <= 1'd1 ;

else cout2 <= 1'b0 ;

end

endmoduleTb:

`timescale 1ns/1ns

`define clk_period 20

module tb();

reg clk;

reg rst_n;

reg cin;

wire cout;

wire cout2;

wire[3:0] q;

initial begin

clk <= 1'b0;

cin <= 1'b0;

rst_n <= 1'b0;

#30 rst_n <= 1'b1;

repeat(20)begin

#90 cin <= 1'b1;

#20 cin <= 1'b0;

end

#1000

$stop;

end

always #(`clk_period/2) clk <= ~clk;

counter_4bit

#( .c_number (10) )

u1

(

.clk (clk ),

.rst_n (rst_n),

.cin (cin ),

.cout (cout ),

.cout2 (cout2),

.q ( q )

);

endmodule 最后

以上就是有魅力大碗最近收集整理的关于FPGA学习笔记(3)——如何理解时序逻辑会延迟一拍的现象的全部内容,更多相关FPGA学习笔记(3)——如何理解时序逻辑会延迟一拍内容请搜索靠谱客的其他文章。

发表评论 取消回复