目录1.D触发器:2.D触发器功能表如下:3.功能表解析:4.同步D触发器解析:5.复位置数D触发器电路图:_d触发器功能表-嵌入式文档类资源-CSDN文库 https://download.csdn.net/download/zhjysx/85593499

https://download.csdn.net/download/zhjysx/85593499

晶体管级数字电路设计专栏目录_LD QM的博客-CSDN博客

关于D触发器设置N进制计数器的方法

MOS管制作三分频电路 multisim仿真源文件

Multisim使用MOS管搭建的五分频电路

目录

1.D触发器:

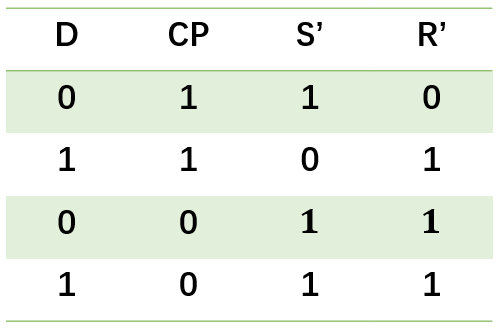

2.D触发器功能表如下:

3.功能表解析:

4.同步D触发器解析:

5.复位置数D触发器电路图:

6.上升沿触发的D触发器:

7.带复位置数的上升沿触发的D触发器:

晶体管级数字电路设计专栏目录_XMJYBY的博客-CSDN博客

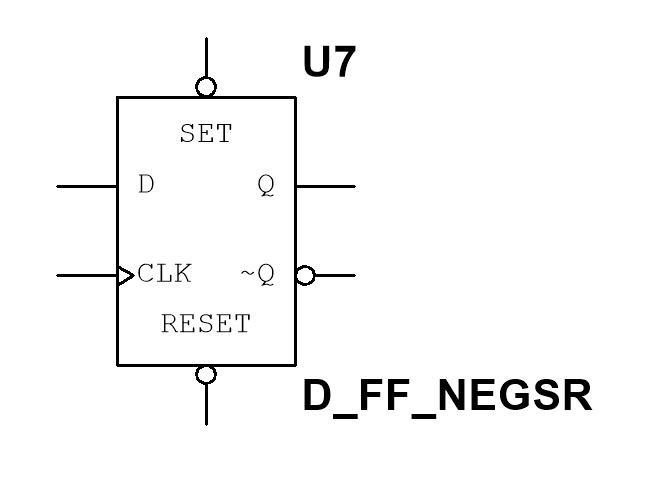

1.D触发器:

从封装中可以看出:

CLK的三角形表示边沿触发,即该D触发器为上升沿触发

SET和RESET均为低电平有效

2.D触发器功能表如下:

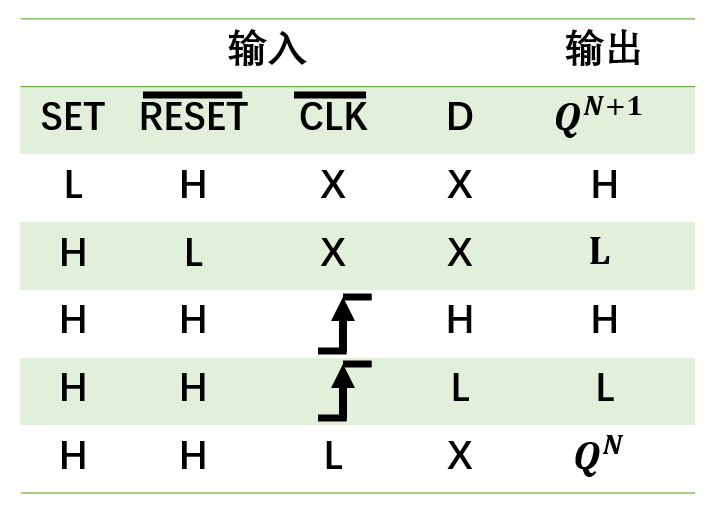

3.功能表解析:

由于SET和RESET都为低电平有效,所以在D触发器工作时,都要接高电平

当RESET为低电平时,触发器复位。

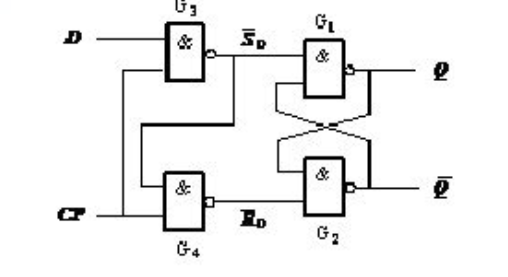

4.同步D触发器解析:

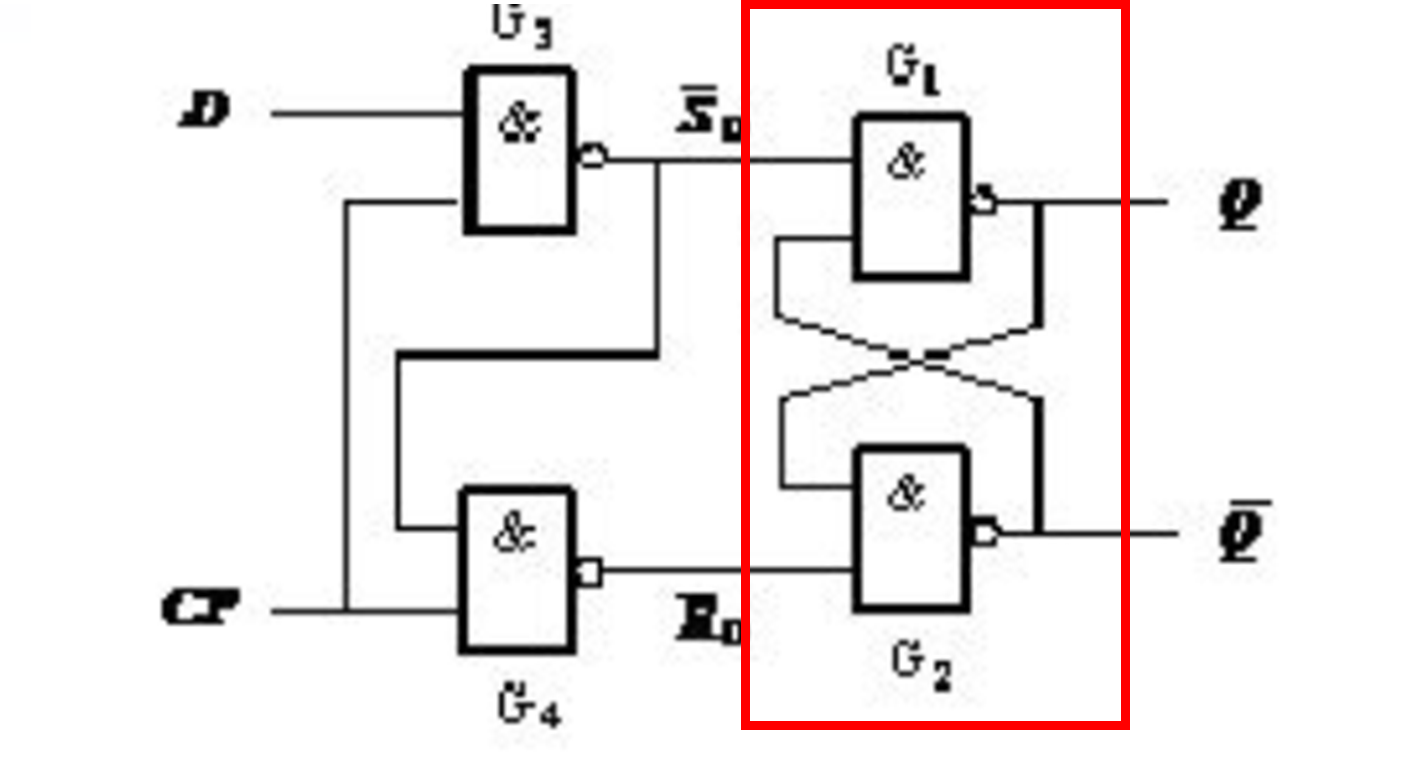

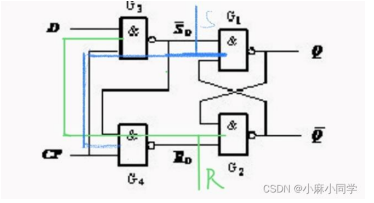

同步D触发器内部结构如下图所示

第一部分:

对应真值表:

第二部分:

为一个RS触发器

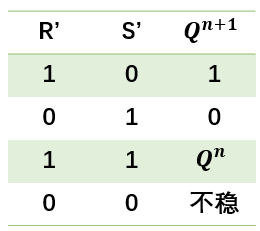

对应真值表:

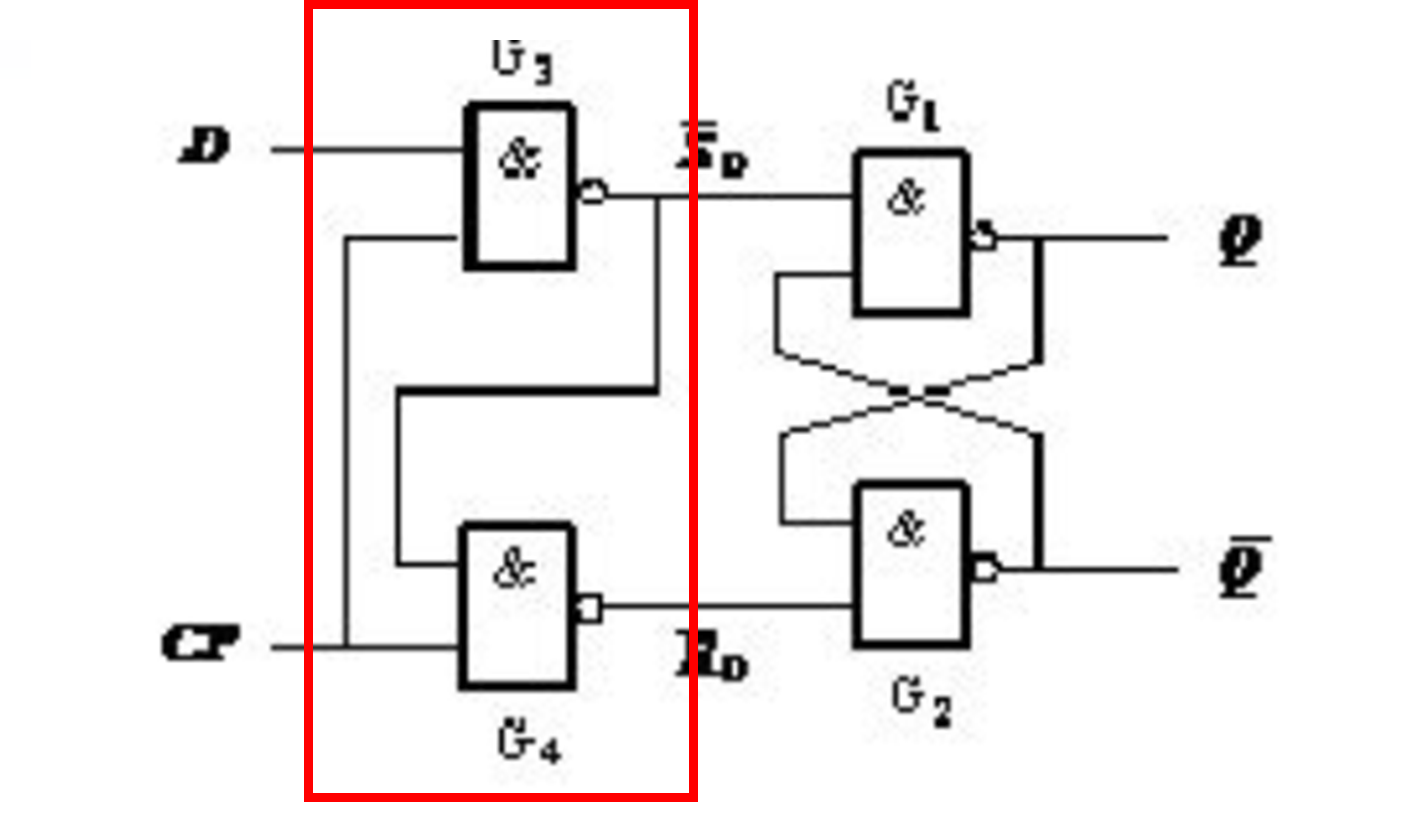

5.复位置数D触发器电路图:

利用与非门有 0 出 1 的特性,插入 S 和 R,将二输入与非门变成三输入与非 门,在电路中先将 S 定为 1 此时当 R 为 1 时,对与非门电路无影响, 当 R 为 0 时,无论 D 和 CP 取值如何,输出的 Q 固定为 0

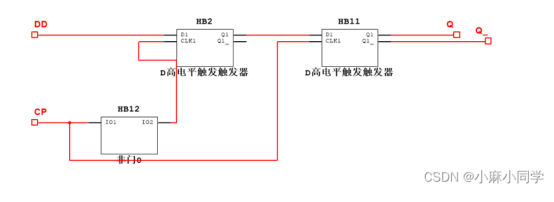

6.上升沿触发的D触发器:

当 CP 信号为 0 时,通过非门输入第一个触发器为 1,第一个触发器就会输出 D 相同的值,第二个触发器保持输出。当 CP 信号为 1 时,第一个触发器保持输 出,第二个触发器读取第一个触发器的输出值并输出,这就构成了一个上升沿 触发的 D 触发器

晶体管级数字电路设计专栏目录_LD QM的博客-CSDN博客

最后

以上就是不安大神最近收集整理的关于十八、D触发器介绍:晶体管级数字电路设计专栏目录_LD QM的博客-CSDN博客关于D触发器设置N进制计数器的方法MOS管制作三分频电路 multisim仿真源文件的全部内容,更多相关十八、D触发器介绍:晶体管级数字电路设计专栏目录_LD内容请搜索靠谱客的其他文章。

发表评论 取消回复